Fターム[5F064DD42]の内容

ICの設計・製造(配線設計等) (42,086) | ICの構造(配線を除く) (6,653) | 付加的要素に関する構造 (884) | ボンディングパッドに関するもの (728)

Fターム[5F064DD42]の下位に属するFターム

Fターム[5F064DD42]に分類される特許

1 - 20 / 359

半導体集積回路

半導体装置

半導体装置および半導体パッケージ

【課題】パッドが設けられた面の向きを変えても、パッドを基板に接続するボンディングワイヤが交差しない半導体装置を提供する。

【解決手段】複数のパッドを含む第1のパッド群と、第1のパッド群に平行に一列に配置された複数のパッドを含む第2のパッド群と、第1のパッド群を基準にして第2のパッド群とは反対側に設けられた複数のバッファ回路を含む第1のバッファ回路群と、第2のパッド群を基準にして第1のパッド群とは反対側に設けられた複数のバッファ回路を含む第2のバッファ回路群と、第1のパッド群の複数のパッドのそれぞれを第2のバッファ回路群の複数のバッファ回路のそれぞれに対応して接続する複数の第1の配線と、第2のパッド群の複数のパッドのそれぞれを第1のバッファ回路群の複数のバッファ回路のそれぞれに対応して接続する複数の第2の配線と、を有する。

(もっと読む)

半導体集積回路装置

【課題】半導体集積回路装置において、I/Oセルの高さを低減すると同時に幅の増大を防ぐことでI/Oセルの占める領域の面積を削減すること。

【解決手段】レベルシフタ回路、I/Oロジック回路およびI/Oバッファ回路を含むI/Oセルがコア領域の周囲に配置された半導体集積回路装置であって、I/Oロジック回路が配置されたI/Oロジック領域、および、I/Oバッファ回路が配置されたI/Oバッファ領域は、I/Oセルに対するパッドが配置された領域と重なり合うとともに、コア領域の辺に平行な方向に互いに並んで配置されている。

(もっと読む)

半導体集積回路装置

【課題】過電流に対して内部回路を保護する半導体集積回路装置を提供することを目的としている。

【解決手段】多層配線構造を有する半導体集積回路装置であって、半導体集積回路装置の内部にある内部回路と半導体集積回路装置の外部にある外部回路とを接続するために半導体集積回路装置の内部に設けられたパッドパターンにおいて、第1の配線層と、第1の配線層が形成されている層とは別の層に形成されている第2の配線層と、第1の配線層と第2の配線層を接続するビアと、を備え、第2の配線層にヒューズパターンが形成されており、ヒューズパターンを経由して内部回路と外部回路とを電気的に接続する。

(もっと読む)

半導体チップ

【課題】チップ面積が小さく低コストで誤動作が発生し難い半導体チップを提供する。

【解決手段】半導体チップ1をパッケージ3に搭載する場合は80個のパッドPAをパッケージ3の80個の端子TAに接続し、半導体チップ1をパッケージ5に搭載する場合は100個のパッドPA,PB,PCをパッケージ5の100個の端子TAに接続する。半導体チップ1の内部回路は、電極E1,E2が絶縁されている場合は80端子のマイクロコンピュータ4として動作し、電極E1,E2がボンディングワイヤWの端部によって短絡されている場合は100端子のマイクロコンピュータ4として動作する。したがって、パッケージの端子数を設定する専用パッドが不要となる。

(もっと読む)

半導体装置の製造方法及び半導体装置

【課題】半導体チップを積層して半導体装置を製造する際に、当該半導体チップの回路の不良電子素子を救済し、半導体装置の歩留まりを向上させる。

【解決手段】ウェハ10を厚み方向に貫通する一対の貫通電極50〜52を形成し、デバイス層11に一対の貫通電極50〜52を短絡する共有配線24、26、28を形成し、デバイス層11の表面11aにおいて異なる場所につながる一対のフロントバンプ20〜22を形成する。一対の貫通電極50〜52に対して異なる極性で電圧を印加し、一対の貫通電極50〜52のうちの一の貫通電極50〜52上にバックバンプ80〜82を形成する。ウェハ10を積層し、一のウェハ10上のバックバンプ80〜82と、他のデバイス層11上のフロントバンプ20〜22とを接続する。

(もっと読む)

回路動作の検証装置及び回路動作の検証方法

【課題】電圧規格や電流規格を満たさない箇所があった場合に、その影響を反映させて検証を行うことができる回路動作の検証装置を提供する。

【解決手段】回路動作の検証装置は、結線情報4と、定格情報6とを用い、回路に入力する信号パターン7が与えられると、その入力パターン7に基づいて回路動作を検証する(S1〜S5)。そして、検証の結果、回路素子に印加される電圧や通電される電流等が定格値を超えることで破壊に至る回路素子が存在すると、当該回路素子を破壊の態様に応じた破壊状態モデルに置換し(S6)、破壊状態モデルに置換した回路について検証を継続する。

(もっと読む)

半導体装置

【課題】チップサイズの増大を抑えつつ、多数の配線間の時定数を一致させる。

【解決手段】半導体装置は、第1のサイズを持つ第1の外部端子と、第1のサイズよりも小さな第2のサイズを持つ複数の第2の外部端子と、第1の外部端子及び複数の第2の外部端子が、前記第1のサイズを基準として配列される外部端子領域と、外部端子領域に隣接して形成され、複数の第2の外部端子にそれぞれ対応付けられる複数の回路と、複数の第2の外部端子とそれら対応付けられた複数の回路との間をそれぞれ接続する複数の配線とを備える第1のチップを含む。複数の第2の外部端子及びそれらに接続された複数の配線は複数のインタフェースを構成し、複数のインタフェースの夫々は、互いに実質的に等しい時定数を持つように、時定数を調整する調整部を少なくとも一つ含む。調整部の少なくとも一部は、外部端子領域内の第1のサイズと第2のサイズとの差により生じるマージン領域に配置される。

(もっと読む)

テスト回路、集積回路、及び、テスト回路のレイアウト方法

【課題】 より簡易な設計手法で作製可能なテスト回路を提供する。

【解決手段】 テスト回路100は、基板と、基板上に形成された配線部及び被試験デバイス部10とを備える構成とする。テスト回路100では、被試験デバイス本体のパターン形成面内における回転中心位置Oと複数の接続電極13a〜13dのそれぞれとを結ぶ直線L1の延在方向が、配線21の延在方向に対して所定の角度で傾いている。さらに、被試験デバイス本体及び複数の接続電極13a〜13dをパターン形成面内で90度回転させた際にも、複数の接続電極13a〜13d及び複数の配線21〜24間の接続が維持されるような位置に複数の接続電極13a〜13dが配置される。

(もっと読む)

半導体装置およびその製造方法

【課題】トリミングヒューズの上の絶縁膜が、トリミングヒューズの機能を高めるために適正な状態を維持することが可能な半導体装置を提供する。

【解決手段】表面を有する絶縁膜III上のヒューズ配線F1と、ヒューズ配線F1上の層間絶縁層II1,II2,PIと、層間絶縁層II1,II2,PIの内部に位置する、ヒューズ配線F1と平面視において重ならない領域に形成された電極部PDとを備える。上記ヒューズ配線F1の真上のうち少なくとも一部の第1の領域において、層間絶縁層II1,II2,PIの厚みが、第1の領域以外の第2の領域における層間絶縁層II1,II2,PIの厚みより薄くなるようにトリミング開口部LTCが形成される。トリミング開口部LTCの内側において側壁および底面の少なくとも一部を覆うアルミニウム薄膜部SALを備える。アルミニウム薄膜部SALは、側壁の少なくとも一部から、底面より上側において上記表面に沿う方向に連なる。

(もっと読む)

半導体ダイ上にフィーチャをめっきするためのヒューズバス

【課題】半導体ダイ上に相互接続部又はボンドパッドなどのフィーチャ構造を電気めっきする方法を提供する。

【解決手段】方法は半導体基板の上方に複数のヒューズ(208)を形成する工程と、半導体基板の上方の複数の相互接続層(400〜408)と、該複数の相互接続層の上面の複数の相互接続パッド(502)とを形成する工程と、を含む。シールリング(202)が、半導体基板(302)と、前記複数の相互接続パッド(502)と、前記複数のヒューズ(208,320)とに形成された能動回路を包囲する。各ヒューズ(208,320)は、対応する相互接続パッド(502)とシールリング(202)とに電気的に接続される。各ヒューズ(208)が導通状態にあるとき、該ヒューズは対応する相互接続パッド(502)をシールリング(202)に電気的に接続する。

(もっと読む)

半導体集積装置

【課題】SiPのチップ間を接続するための端子数が増加する。

【解決手段】パッケージ内部に第1の半導体チップと第2の半導体チップが集積される半導体集積回路であって、前記第1の半導体チップは、第1の通信部と、複数のアナログ回路とを備え、前記第2の半導体チップは、第2の通信部と、前記複数のアナログ回路の特性調整用データを格納するメモリ部とを備え、前記第1の通信部と前記第2の通信部とがシリアルデータ通信線で接続され、前記シリアルデータ線を経由して前記第1の半導体チップが備える複数のアナログ回路の特性調整用データをそれぞれ複数のアナログ回路に転送する半導体集積回路。

(もっと読む)

半導体集積回路装置

【課題】内部コアエリアのトランジスタを犠牲にすることなく、周辺エリアのトランジスタを用いてリップルフィルタによる電源供給回路を構成する。

【解決手段】入出力回路を構成するためのトランジスタが配列されてなる周辺エリア(図2の12に相当)をチップ上に有する半導体集積回路装置であって、ドレインを電源に接続し、ソースを負荷側に接続し、ゲートを容量素子(図2のC1)を介して交流的に接地する第1のトランジスタ(図2のMN1)と、容量素子をゲート・基板間によって形成する第2のトランジスタと、を周辺エリアに備える。

(もっと読む)

半導体装置、半導体装置の設計方法、半導体装置設計装置、及びプログラム

【課題】より多くのI/Oセルを配置することができるようにする。

【解決手段】多層配線層には、電位供給用接続配線230が設けられている。電位供給用接続配線230は、平面視で外周セル列20を構成するI/Oセル200のいずれか、および内周セル列30を構成するI/Oセル200のいずれかと重なっている。そして電位供給用接続配線230は、外周セル列20の下方に位置する電源電位供給配線222を、内周セル列30の下方に位置する電源電位供給配線222に接続するとともに、外周セル列20の下方に位置する接地電位供給配線224を、内周セル列30の下方に位置する接地電位供給配線224に接続している。

(もっと読む)

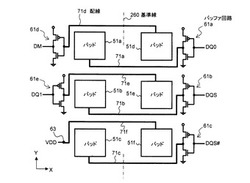

半導体装置

【課題】従来の入出力セルよりも回路面積の大きな入出力セルを面積効率良く配置する。

【解決手段】半導体装置において、複数の第1バッファセル31〜34は、基板の一辺に沿って1列に設けられる。複数の第2バッファセル21,22は、複数の第1バッファセルよりも基板の中央寄りの位置に、複数の第1バッファセルの配列方向に沿って1列に設けられる。複数の第1パッド81〜88は、複数の第1バッファセルの上部に上記配列方向に沿って1列に設けられる。複数の第2パッド61〜66は、複数の第1パッドよりも基板の中央寄りの位置に、上記配列方向に沿って1列に設けられる。複数の第2パッド61〜66は、各々が、複数の第1バッファセルのいずれか1つと個別に接続される複数の第3のパッド61,63,65,66と、各々が、複数の第2バッファセルのいずれか1つと個別に接続される複数の第4パッド62,64とを含む。

(もっと読む)

半導体装置における電流による配線破壊箇所の予測方法

【課題】半導体装置の電流による配線破壊箇所の予測方法において、解析時間を短縮する。

【解決手段】下層配線14A,14Bをそれぞれ一つの直列抵抗で、第1の下層ビア15A,第2の下層ビア15Bを1個の抵抗で、第1の上層ビア17A、第2の上層ビア18Bを1個の抵抗で、第1及び第2の上層配線16A,16Bを抵抗ブリッジ回路で、パワートランジスタTRを直列抵抗で、それぞれモデリングしてなる解析モデルをモデリング用計算機により生成する。回路シミュレータ3により、解析モデルにおけるパワートランジスタTRに電流を供給し、解析モデルにおける各抵抗に流れる電流に基づいて、第1及び第2の下層配線14A,14B、第1及び第2の上層配線16A,16Bにおける各抵抗の電流密度を計算し、各抵抗の電流密度と、配線破壊を起こす電流密度閾値とを比較器4により比較することにより、配線破壊箇所を予測する。

(もっと読む)

半導体集積回路装置

【課題】配線層間膜の平坦化を行いながら、クラックの伝搬と配線層間膜の剥がれを抑制することを目的とする。

【解決手段】電極パッド113形成領域の、低誘電率膜より誘電率の高い配線層間膜からなる多層配線層領域において、ダミービアを形成しないことにより、配線層間膜の平坦化を行いながら、クラックの伝搬と配線層間膜の剥がれを抑制することができる。

(もっと読む)

半導体集積回路装置

【課題】電源幹線内で同電位の電源線を相互に接続することにより配線抵抗を削減するとともに、電源幹線間で同電位の電源線を接続することにより配線抵抗をさらに削減できるようにすること。

【解決手段】半導体集積回路装置は、第1の層において第1の方向に延伸する第1の電源線および第2の電源線と、第2の層において第1の方向に延伸するとともに第1の電源線の直上に設けられた第3の電源線と、第2の層において第1の方向に延伸するとともに第2の電源線の直上に設けられた第4の電源線とを備え、第1の電源線および第2の電源線は第1の方向に延伸するセル棚(セル列)に含まれる複数のセルに電源を供給し、第3の電源線は第1の電源線の電位と異なる電位が供給され、第4の電源線は第2の電源線の電位と異なる電位が供給される。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】チップ面積を増大させることなく、針ずれに起因する誤測定や誤検査を防止することができる、半導体装置および半導体装置の製造方法を提供する。

【解決手段】半導体装置は、内部回路と、内部回路と電気的に接続されるとともに、検査装置に接続された複数の探針がそれぞれ接触する複数のパッドを備える。少なくとも2つのパッド2a、2bの間に、当該2つのパッド2a、2bを電気的に接続するとともに、所定の電流を印加することにより、恒久的に、電気的に切断されるヒューズ素子4が設けられる。パッド2a、2bの間の抵抗値を測定することで、針ずれの有無を検知することができる。その後、ヒューズ素子を切断し、内部回路の検査が実施される。

(もっと読む)

1 - 20 / 359

[ Back to top ]