Fターム[5F064EE12]の内容

ICの設計・製造(配線設計等) (42,086) | 配線 (13,054) | 配線パターン (7,249) | メッシュ状、格子状配線 (332)

Fターム[5F064EE12]の下位に属するFターム

格子点 (103)

Fターム[5F064EE12]に分類される特許

1 - 20 / 229

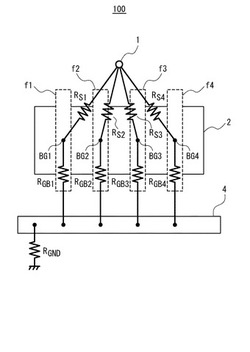

ノイズ解析モデル及びノイズ解析方法

【課題】解析対象回路内に設けられた素子のそれぞれに対する基板ノイズの影響を解析することができるノイズ解析モデル及びノイズ解析方法を提供すること。

【解決手段】本発明の一態様にかかるノイズ解析モデル100は、抵抗RS1〜RS4、抵抗RGB1〜RGB4及び接地抵抗RGNDを有する。抵抗RS1〜RS4は、ノイズ発生源から半導体基板を介して基板ノイズが伝搬する接続点1と、バックゲート直下の半導体基板中の点BG1〜BG4の間にそれぞれ接続される。抵抗RGB1〜RGB4は、バックゲート直下の半導体基板中の点BG1〜BG4とガードバンド4との間に接続される。接地抵抗RGNDは、ガードバンド4と接地電位との間に接続される。

(もっと読む)

集積回路

【課題】電力消費量の増大を抑制しつつ、タイミング信号のスキューを低減する。

【解決手段】主クロック分配回路は、タイミング信号を複数の主タイミング信号に分岐して分配する。副クロック分配回路は、タイミング信号の分配が指示された場合にはタイミング信号を複数の副タイミング信号に分岐して分配する。最小遅延タイミング信号出力部は、複数の主タイミング信号のいずれかと複数の副タイミング信号のいずれかとのうち先に分配された信号を最小遅延タイミング信号として出力する。同期動作回路は、最小遅延タイミング信号に同期して動作する。測定部は、複数の主タイミング信号のいずれかの遅延のばらつきを示す値を測定する。クロック分配回路制御部は、測定された値の示す前記ばらつきが前記所定値以上であるときに副分配回路に前記タイミング信号の分配を指示する。

(もっと読む)

半導体集積回路、半導体集積回路の設計方法、および半導体集積回路の設計装置

【課題】配線層に形成される信号配線をなるべく迂回させずに配線できるように電源スタックビアが配置された半導体集積回路を提供すること。

【解決手段】半導体集積回路は、第1の方向に延伸された第1,第2の下層電源配線11A,11Bと、第2の方向に延伸された第1,第2の上層電源配線12A,12Bと、上層,下層電源配線を接続させる第1,第2接続部3A,3Bと、を備え、第1,第2接続部は、第1,第2の接続用配線26A,26Bと、第1,第2の位置変換用配線27A,27Bと、第1,第2の上側ビア28A,28Bと、を有して構成され、第1,第2の接続用配線は、第2の方向に沿った同一ライン上に配置され、第1,第2の位置変換用配線は、第1,第2の接続用配線を第2の方向に沿って延長した領域内に形成され、第1,第2の上側ビアは、第1の方向に沿った同一ライン上となる位置に配置される。

(もっと読む)

レイアウト設計装置、レイアウト設計方法およびレイアウト設計プログラム

【課題】マクロの全端子で配線が引き出し可能かを判定できるレイアウト設計装置、レイアウト設計方法およびレイアウト設計プログラムを提供する。

【解決手段】記憶部11は内部にマクロを含んだ多層回路の階層レイアウトの設計データを記憶する。チャネル数算出部13は設計データに基づいて、マクロの各端子から所定の配線層まで配線を引き出すために使用可能なチャネル数を端子毎に算出する。経路算出部15は算出したチャネル数の少ない端子から順に、端子から所定の配線層まで配線を引き出すための経路を算出する。経路判定部16はマクロの全ての端子について引き出し経路を算出できたか否かを判定する。

(もっと読む)

配線抵抗網作成装置および配線抵抗網作成方法

【課題】配線形状の複雑化に起因するエレクトロマイグレーション解析の処理時間の増加を抑制する。

【解決手段】配線パターン分割部(22)と、ビア部分抵抗網設定部(25)と、配線部分抵抗網設定部(24)と、配線抵抗・ビア抵抗接続部(28)を有する配線抵抗網作成装置(10)を構成する。配線パターン分割部(22)は、レイアウトデータからビアとの接続位置情報を含む配線パターンを取得し、配線パターンをアレイビア部分と配線部分に分割する。ビア部分抵抗網設定部(25)は、アレイビア部分に対応するビアノードおよびビア部分抵抗を含むビア部分抵抗網を設定する。配線部分抵抗網設定部(24)は、配線部分に対応する配線ノードおよび配線部分抵抗を含む配線部分抵抗網を設定する。配線抵抗・ビア抵抗接続部(28)は、ビア部分抵抗網と配線部分抵抗網を接続して配線抵抗網データを生成する。

(もっと読む)

半導体集積回路および半導体集積回路の設計方法

【課題】半導体集積回路の面積を増大させることなく、配線性のよいテスト専用回路の電源遮断を実現する半導体集積回路を提供する。

【解決手段】テスト実行時のみ動作するテスト専用回路を有する半導体集積回路1であって、当該半導体集積回路1の内部回路領域(内部制御回路部100)に電源を供給する通常電源(通常動作用電源)104と、当該内部回路領域の全面にメッシュ状に配線され、テスト専用回路に電源供給するテスト用電源103と、テスト用電源103と通常電源104とを接続及び遮断して、通常電源104からテスト用電源103への電源供給を制御する電源遮断スイッチ109と、を備える。

(もっと読む)

キャパシタおよび半導体装置

【課題】キャパシタの電極として機能する配線の延伸方向への電流供給を容易とすること。

【解決手段】第1金属層12と、前記第1金属層の膜厚方向に離間して設けられ、第1方向および前記第1方向に交差する第2方向に配列された複数の孔36を備えた第2金属層14と、前記第2金属層の膜厚方向で前記第1金属層とは反対側に離間して設けられ、前記第1方向および前記第2方向とは異なる方向に延伸し、第1配線と第2配線とが交互に設けられた複数の第1配線16aおよび複数の第2配線16bと、前記複数の第1配線と前記複数の第2配線との間に設けられた誘電体膜26と、前記複数の第1配線を、それぞれ前記複数の孔を通過し前記第1金属層に電気的に接続する複数の第1ビア配線32と、前記複数の第2配線を、それぞれ前記第2金属層に電気的に接続する複数の第2ビア配線34と、を具備するキャパシタ。

(もっと読む)

半導体集積回路

【課題】製造コストを増大させずに、半導体集積回路の電源配線、接地配線の電圧降下を減少させる。

【解決手段】半導体チップ1上の第1の方向に延びる電源配線12Aが配置され、半導体チップ1上の第2の方向に延びると共に、第2の方向から第1の方向に屈曲し、電源配線12Aの一部と重畳する屈曲部24Aを有する電源引き出し配線22Aが配置されている。また、第1の方向に延びる接地配線12Bが配置され、第2の方向に延びると共に、第2の方向から、第1の方向とは逆方向の第3の方向に屈曲し、接地配線12Bの一部と重畳する屈曲部24Bを有する接地引き出し配線22Bが配置されている。電源引き出し配線22Aと接地引き出し配線22Bを覆う第1の層間絶縁膜13の中には、電源配線12Aと屈曲部24Aを接続する電源配線ビアコンタクト14Aと、接地配線12Bと屈曲部24Bを接続する接地配線ビアコンタクト14Bが配置されている。

(もっと読む)

遅延解析装置、遅延解析方法、及び遅延解析プログラム

【課題】高い精度を保ちながらも、高速に遅延時間を算出できる遅延解析装置等を提供する。

【解決手段】遅延解析装置100は、クロックメッシュ上の複数の位置におけるクロック信号の遅延時間および/または波形鈍り値に基づいて、クロックメッシュ接続素子に入力されるクロック信号の遅延時間および/または波形鈍り値を算出する。そして、その算出した遅延時間および/または波形鈍り値に基づいて、クロックパス上の他の回路素子に入力されるクロック信号の遅延時間を算出する。

(もっと読む)

半導体集積回路及び半導体集積回路の設計方法

【課題】電位ドロップに起因するセルの動作不良を防止すること。

【解決手段】本発明に係る半導体集積回路は、チップ1上に配置された電源パッド2aと、電源配線構造10を介して電源パッド2aに接続された回路群21,22とを備える。その電源配線構造10は、異なる配線層に形成され複数の交差点IS1,IS2においてオーバーラップする複数の第1電源配線11及び複数の第2電源配線12と、それら複数の第1電源配線11と複数の第2電源配線12を接続するビア13とを有する。上記回路群は、第1領域R1に配置された機能ブロック21を含む。ビア13は、第1領域R1と電源パッド2aの間の第2領域R2における複数の交差点IS2の一部に配置されていない。

(もっと読む)

半導体装置

【課題】電源遮断がされる領域同士の場合であっても生じる、電源遮断移行時および復帰時の貫通電流の問題を解決しつつアイソレーション回路を不要とする半導体装置を提供する。

【解決手段】半導体装置は、第1の電源線601と、第1のスイッチ605を介して第1の電源線に接続される第2の電源線101、および第2の電源線に接続されるマクロセルコア508を有するマクロセルと、第2のスイッチ603を介して第1の電源線に接続される第3の電源線602と、第3の電源線に接続され、マクロセルコアの入力または出力の少なくともいずれかに接続される回路ブロック501とを備え、第2の電源線と第3の電源線とが接続される。

(もっと読む)

半導体装置

【課題】配線及びビア間接続の信頼性を向上させた半導体装置を提供する。

【解決手段】実施形態に係る半導体装置は、半導体基板と、前記半導体基板上の異なる高さに配置され、配線が形成された複数の配線層と、前記配線層の積層方向に延びる柱状に形成され、異なる複数の前記配線層の配線間を電気的に接続するビアとを備え、前記配線の一部は、前記ビアの中間部において前記ビアに接触する中間配線であり、所定の前記配線層の中間配線及びその他の所定の前記配線層の中間配線は、それぞれ前記ビアを前記積層方向に直交する方向で貫通し、且つ、前記ビア内において相互に交差していることを特徴とする。

(もっと読む)

半導体装置

【課題】被測定素子の配置密度を高めることが可能な半導体装置を提供する。

【解決手段】異なる層に設けられた列配線M1および行配線M2からなる単位アレイ配線21と、異なる層に設けられた列配線M3および行配線M4からなる単位アレイ配線22とを、互いに異なる層に設ける。複数の単位アレイ配線21,22には、それぞれ、複数の被測定素子11,12のいずれか一つを接続する。複数の単位アレイ配線21,22どうしを部分的に重ね合わせて(オーバーラップさせて)配置することにより、被測定素子11,12の配置密度を高めることが可能となる。

(もっと読む)

半導体装置、半導体装置の製造方法

【課題】内部電源と、該内部電源に電源を供給する補償容量部を有する半導体装置では、コンデンサの容量値が配置場所で変化するため、容量値の見積もりが煩雑になるという問題を解決する。

【解決手段】内部電源と、該内部電源に電源を供給する補償容量部を有する半導体装置の補償容量部のレイアウト配置の際に、補償容量部を構成する領域に拡散層の矩形領域を配置する。また、該拡散層の矩形領域の各辺に対し、各辺の中心が直行する箇所に矩形開口部を設ける。また、該拡散層の矩形領域の中心線近傍に沿ってゲート電極を直行するように形成する。また、該拡散層の該矩形領域の四隅に上層の金属層と接続するためのコンタクトを形成する。また、該ゲート電極と該拡散層の矩形開口部の重なる箇所にゲート電極と上層の金属層を接続するコンタクトを形成する。また、該ゲート電極が直行する箇所で容量を形成する。また、補償容量の単位セルを構成する。

(もっと読む)

半導体装置

【課題】複数の電圧レベルの電源電圧が供給される入出力バッファ回路に対して、従来よりも少ない電源配線スペースで十分な電源供給を可能にする。

【解決手段】半導体装置3において、入出力バッファ回路BFは電圧レベルの変換を行なう。第1の電源配線HVLは、入出力バッファ回路BFの第1の回路部分HCと接続され、第1の回路部分HCに第1の電源電圧VCC1を供給する。第2の電源配線LVLは、入出力バッファ回路BFの第2の回路部分LCと接続され、第2の回路部分LCに第2の電源電圧VCC2を供給する。複数のスイッチ部SWは、第3の電源配線SVLに沿った複数箇所にそれぞれ設けられる。複数のスイッチ部SWの各々は、内部回路10から出力された制御信号に応じて、第1および第2の電源配線HVL,LVLのうち選択された一方の電源配線と第3の電源配線SVLとを接続する。

(もっと読む)

回路設計支援装置、回路設計支援方法および半導体集積回路

【課題】配線の遅延特性のばらつきを抑制すること。

【解決手段】回路設計支援装置1は、設定部1aと生成部1bとを有している。設定部1aは、半導体集積回路モデル2の層2a、2bそれぞれに、積層方向および面方向に隣接するユニット3の配線方向が互いに異なる方向に配線が生成される複数の矩形のユニット3を設定する。生成部1bは、ユニット3の境界で異なる層のユニット3に跨る配線を生成する。

(もっと読む)

半導体装置及びそのレイアウト方法

【課題】良好な伝送性能と小さい配置面積を両立可能なデータバスを備える半導体装置を提供する。

【解決手段】本発明の半導体装置は、配線層M1、M2と、複数のデータ入出力端子と、N本のデータ線(DU、DL)を含むデータバスとを備え、N本のデータ線は所定の配線長の長短に応じた2種類のデータ線群を含む。配線層M1、M2にはデータ線(DL、DU)の各々に隣接する複数のシールド線(Sa、Sb、Sc)が配置され、各データ線(DL、DU)は、配線層M1、M2の積層方向で互いに重ならない位置に配置される。このような配線構造により、各データ線(DL、DU)の間のカップリング容量を抑え、データバスのクロストークを防止することができる。

(もっと読む)

半導体集積回路の設計方法

【課題】 半導体集積回路の電源EM及びスタティックIRドロップの解析と電源補強設計を改善する。

【解決手段】 一つの実施形態の半導体集積回路の設計方法では、電源配線のEM解析を行い、EM解析でEMエラーが発生した場合、EMエラーとなるレイヤ及び座標をチェックしてリストを格納し、半導体集積回路の抵抗網を抽出し、EMエラーとなるレイヤ及び座標を含む抵抗セグメントを全て削除してIRドロップ値が許容値を満足するかの第1の判定を行い、記第1の判定でIRドロップ値が許容値を満足する場合、EMによって半導体集積回路が動作不良とならない抵抗セグメントをレイアウトデータから削除する。

(もっと読む)

半導体装置の設計装置、半導体装置の設計方法、及び半導体装置

【課題】回路の面積の増大や、設計時間の長期化や、大規模な回路の場合における修正の困難性などの問題が発生することなく、EMの発生が著しく抑制された配線を設計する。

【解決手段】半導体装置の設計方法は、互いに平行に配置された複数の配線と複数の配線を互いに接続する複数のビアとを備えるグリッド配線を配置するステップS01と、グリッド配線に接続された複数の内部回路を配置するステップS02と、複数の内部回路によりグリッド配線内に流れる電流の電流密度を計算するステップS03と、電流密度に応じたエレクトロマイグレーションを抑制する配線長となるように、複数の配線の各々を分断するステップS04、S05とを具備する。

(もっと読む)

ダミーメタル配置評価装置、ダミーメタル配置評価方法及びダミーメタル配置評価プログラム

【課題】配線オブジェクトの敷設方向に対してずれを持たせたダミーメタルの配置を評価すること。

【解決手段】ダミーメッシュ情報作成部21は、配線オブジェクトの方向に対してずれを設けて規則的に配置したダミーメタルのブロック群を、各メッシュ内のダミーメタルの配置が同一となるようにメッシュ形状に分割する。重複判定部23は、分割によって得られた複数のダミーメッシュについて、配線オブジェクトとメッシュ内のダミーメタルのブロックとの重複を判定する。判定の結果、配線オブジェクトと重複するダミーメタルのブロックを除去したダミー情報をダミー情報算出部25が算出し、情報統合部26が配線オブジェクトの情報と統合する。評価部27は、統合したダミー挿入後の回路レイアウトが設計基準を満たすかを評価する。

(もっと読む)

1 - 20 / 229

[ Back to top ]