Fターム[5F064EE19]の内容

ICの設計・製造(配線設計等) (42,086) | 配線 (13,054) | 配線パターン (7,249) | 配線の配列、ピッチ (319)

Fターム[5F064EE19]に分類される特許

1 - 20 / 319

閾値テーブルの作成方法、クロストーク解析の悲観性削減方法、クロストーク解析方法、及びクロストーク解析プログラム

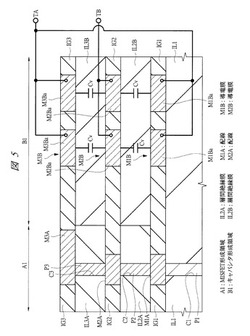

半導体装置

【課題】容量素子を有する半導体装置の性能を向上させる。

【解決手段】MISFET形成領域A1の配線M1Aと配線M2Aとの間に位置する層間絶縁膜IL2Aと、キャパシタ形成領域B1の導電膜M1Bと導電膜M2Bとの間に位置する層間絶縁膜IL2Bについて、層間絶縁膜IL2Bを、層間絶縁膜IL2Aより誘電率の大きい膜[ε(IL2A)<ε(IL2B)]とする。また、導電膜M1Bと導電膜M2Bとは、層間絶縁膜IL2Bを介して対向し、導電膜M1Bには第1電位が印加され、導電膜M2Bには第1電位とは異なる第2電位が印加される。このように、縦方向に容量(Cv)を形成することで、耐圧劣化の問題を回避し、容量を構成する導電膜M1BとM2B間に高誘電率の絶縁膜を用いることで、容量を大きくする。

(もっと読む)

半導体装置

【課題】配線間の寄生容量を削減可能にした半導体装置を提供する。

【解決手段】X方向に配列する複数のトランジスタについて、夫々が、対応するダミーゲートDG1,DG2を挟む複数のソース拡散層S1,S2に接続する第2及び第3の金属配線M12,M13は、2つのS1,2つのS2に夫々接続する複数の第1のビアV1の両方を含む第1の幅L1と、V1を含まず、L1よりも短い第2の幅L2と、を有する。ドレイン拡散層D1に接続する第1の金属配線M11と、M12との間、並びにM11及びM13の間の夫々は、L1に対応する第1のギャップSP1と、L2に対応する、L1よりも大きな第2のギャップSP2と、を有する。好ましくは、M11〜M13の夫々と第2のビアV2を介して接続される第4〜第6の金属配線M24〜M26の夫々は、L1よりも短い第3の幅L3を有する。

(もっと読む)

半導体装置

【課題】占有面積の小さな直線状の電気ヒューズを有する半導体装置を提供する。

【解決手段】複数の突出部10fは、電気ヒューズ部10aの中央位置からずれた位置、より具体的には、ビア10dに近くかつビア10eから遠い位置に設けられている。また、複数の突出部20fは、電気ヒューズ部20aの中央位置からずれた位置、より具体的には、ビア20dから遠くかつビア20eに近い位置に設けられている。つまり、突出部10fおよび突出部20fは、ジグザグ状に配置されている。

(もっと読む)

レイアウト設計方法、および、レイアウト設計プログラム

【課題】チップ面積の増大を抑制しつつ、ダミー配線パターンの配置にかかる工数を低減する。

【解決手段】レイアウト設計方法は、レイアウト設計装置が、レイアウト領域に対して、半導体集積回路の配置配線(S1)を行った後、レイアウト領域に配置されているバルクセルを抽出し(S2)、レイアウト領域において、抽出したバルクセルの周囲に、所定の大きさを備える空き配線領域が存在するかどうかを検索し(S3)、検索の結果、所定の大きさを備える空き配線領域を検出した場合、抽出したバルクセルの座標を基準にして、検出した空き配線領域にダミー配線パターンを配置(S4)する。

(もっと読む)

半導体装置、半導体装置の製造方法、及び、半導体装置のレイアウト方法

【課題】新たな要因に起因したクラックの発生を抑制すること。

【解決手段】第1のAl配線31と絶縁膜33とを含む第1のAl配線層30と、第2のAl配線41と絶縁膜43とを含む第2のAl配線層40と、複数の第3のAl配線51と絶縁膜52とを含む第3のAl配線層50と、第1のAl配線31と第2のAl配線41とを接続する第1のビア32と、第2のAl配線41と第3のAl配線51とを接続する第2のビア42とを有し、少なくとも一部の第3のAl配線51は隣り合う第3のAl配線51同士の間隔Bが2.25μm以下である隙間60を形成しており、平面視で隙間60の中の少なくとも一部は第1のAl配線31及び第2のAl配線41と重ならない領域を有し、隙間60を形成するように対峙した第3のAl配線51の対峙方向の配線幅Cは15μmより大きく、第2のビア42同士の間隔Fは第2のビア42の径Gの3倍以上である半導体装置。

(もっと読む)

キャパシタおよび半導体装置

【課題】キャパシタの電極として機能する配線の延伸方向への電流供給を容易とすること。

【解決手段】第1金属層12と、前記第1金属層の膜厚方向に離間して設けられ、第1方向および前記第1方向に交差する第2方向に配列された複数の孔36を備えた第2金属層14と、前記第2金属層の膜厚方向で前記第1金属層とは反対側に離間して設けられ、前記第1方向および前記第2方向とは異なる方向に延伸し、第1配線と第2配線とが交互に設けられた複数の第1配線16aおよび複数の第2配線16bと、前記複数の第1配線と前記複数の第2配線との間に設けられた誘電体膜26と、前記複数の第1配線を、それぞれ前記複数の孔を通過し前記第1金属層に電気的に接続する複数の第1ビア配線32と、前記複数の第2配線を、それぞれ前記第2金属層に電気的に接続する複数の第2ビア配線34と、を具備するキャパシタ。

(もっと読む)

半導体装置および配線レイアウト方法

【課題】配線間のピッチを縮小可能にした半導体装置を提供する。

【解決手段】半導体基板に形成された複数のトランジスタと、第1の方向に延在する第1の配線を備えた第1の配線層と、第1の配線層よりも上層に設けられ、第1の方向と交差する第2の方向に延在し、第1の配線と電気的に接続された第2の配線を備えた第2の配線層と、半導体基板と第1の配線層との間に設けられ、複数のトランジスタに接続する第1の中継配線と、第1の中継配線が形成された第1の中継配線層と第1の配線層との間に設けられ、第1の配線と複数のトランジスタのうちの一つとを接続する第2の中継配線とを有する構成である。

(もっと読む)

半導体装置

【課題】周辺回路領域を整形された形状とすることによりチップ面積を縮小する。

【解決手段】Y方向に延在する複数のデータバスDBがピッチP1でX方向に配列されたメモリセル領域40と、対応する複数のデータバスDBにそれぞれ接続された複数のバッファ回路BCが設けられたバッファ領域61とを備える。バッファ領域61上においては、Y方向に延在する複数のデータバスDBがピッチP2でX方向に配列され、ピッチP2はピッチP1よりも小さい。本発明によれば、データバスDBの配列ピッチをバッファ領域上において縮小していることから、他の回路ブロックに割当可能な面積を十分に確保することが可能となる。これにより、当該回路ブロックの幅拡大や形状の変形が不要となることから、無駄な空きスペースが生じにくく、チップ面積を縮小することが可能となる。

(もっと読む)

信頼性を改良するための導電性層間のビア

【課題】ビアの信頼性を改良するための技術を提供する。

【解決手段】別の半導体デバイスが、複数の導電性配線(12−20)を含む第1層(21)および第2層(33)を含み、複数の非機能的ビアパッド(34)が、第2層または第1層と第2層との間に含まれる。複数のダングリングビア(40)は、第1層の特定の領域内に含まれる。ダングリングビアは、第1層の1つまたは複数の配線をビアパッドの対応する一つに接続する。

(もっと読む)

半導体装置

【課題】隣接する2つのトランジスタ同士が接続された構成を有し、省スペースと電流集中による信頼性の低下の抑制とを両立させた半導体装置を実現できるようにする。

【解決手段】半導体装置は、第1のトランジスタ101と接続された第1のバス111、第2のトランジスタ102と接続された第2のバス112と、第1のバス111と第2のバス112との間に形成され、第1のバス111と第2のバス112とを接続するバス間配線121とを備えている。バス間配線121は、第1のバス111における第2のバス112と対向する辺の一部及び第2のバス112における第1のバス111と対向する辺の一部と接続されている。第1のコンタクトパッド131は、第1のバス111の一部と接続され、第2のコンタクトパッド132は、第2のバス112の一部と接続されている。

(もっと読む)

レイアウト設計装置、レイアウト設計方法およびプログラム

【課題】配線およびダミーパターンが配置された領域の割合を各メタル層において均一に保ちつつ、ダミーパターンの生成によって生じたタイミングエラーを解消できるようにすること。

【解決手段】レイアウト設計装置は、配線およびダミーメタルが配置されたメタル層において、エラーを生じた配線の周囲に配置された複数のダミーメタルの中から該エラーの原因となったダミーメタルを抽出し、該メタル層を分割して得られた複数の領域のそれぞれにおいて、配線およびダミーメタルを含むメタルが占める割合であるメタル密度が該メタル層に対して規定された所定のメタル密度以上となるようにしつつ、該エラーが解消されるように、抽出したダミーメタルの中から削除すべきダミーメタルを選択するダミーメタル選択部と、選択されたダミーメタルを削除するダミーメタル変更部と、を備えている。

(もっと読む)

半導体集積回路のレイアウト設計方法、レイアウト設計装置及びレイアウト設計プログラム

【課題】長さが均一で直線的な配線を配置することができる半導体集積回路のレイアウト設計方法、レイアウト設計装置及びレイアウト設計プログラムを提供すること。

【解決手段】半導体集積回路のレイアウト設計方法は、第1の配線ピッチで配線を行う高速配線処理と、第1の配線ピッチより狭い第2の配線ピッチで配線を行う通常配線処理と、を有する。高速配線処理は、所定の高速バス配線上の複数のネットを第1の配線ピッチで略平行、かつ、略等長となるように自動配線を行う。通常配線処理は、高速配線処理より前に実行されない。

(もっと読む)

半導体装置

【課題】配線及びビア間接続の信頼性を向上させた半導体装置を提供する。

【解決手段】実施形態に係る半導体装置は、半導体基板と、前記半導体基板上の異なる高さに配置され、配線が形成された複数の配線層と、前記配線層の積層方向に延びる柱状に形成され、異なる複数の前記配線層の配線間を電気的に接続するビアとを備え、前記配線の一部は、前記ビアの中間部において前記ビアに接触する中間配線であり、所定の前記配線層の中間配線及びその他の所定の前記配線層の中間配線は、それぞれ前記ビアを前記積層方向に直交する方向で貫通し、且つ、前記ビア内において相互に交差していることを特徴とする。

(もっと読む)

マクロ用レイアウト検証装置及び検証方法

【課題】マクロのレイアウト情報に基づいて、当該マクロが使用されるLSIのレイアウト設計時に発生する可能性がある設計規則違反を予め検出する。

【解決手段】マクロ用レイアウト検証装置は、マクロの端子にビアコンタクトを配置したと仮定する手段と、ビアコンタクトとマクロ内レイアウトとの関係が設計規則に違反するか否かを判定する手段と、を具備する。

(もっと読む)

集積回路デバイス

【課題】プロセス寸法の縮小に伴う光相互作用の予測品質の低下を抑止する。

【解決手段】ゲートレベル仮想格子の、連続的に隣接して配置された少なくとも3本の仮想ラインのそれぞれは、その上に定義された少なくとも1つの線形導電体形状を有し、ゲートレベル仮想格子の少なくとも3本の仮想ラインの第1の仮想ラインは、その上に定義され、第1の終端−終端間スペーシングで分離された2つの線形導電体セグメントを有し、ゲートレベル仮想格子の少なくとも3本の仮想ラインの第2の仮想ラインは、その上に定義され、第2の終端−終端間スペーシングで分離された他の2つの線形導電体セグメントを有し、第1の仮想ラインに沿って測定された第1の終端−終端間スペーシングの寸法は、第2の仮想ラインに沿って測定された第2の終端−終端間スペーシングの寸法に等しく、ゲートレベル仮想格子の仮想ラインは、いかなる導電体形状によっても占有されない。

(もっと読む)

半導体集積回路のレイアウト設計方法

【課題】半導体集積回路のレイアウト設計において、幅が広い第1の配線と幅が狭い第2の配線との間に無駄なスペースが発生することによる配線性の悪さを改善する。

【解決手段】このレイアウト設計方法は、回路情報に基づいて、レイアウト領域において複数の横ラインと複数の縦ラインとが交差する格子点上に、複数の回路素子の接続点を配置するステップ(a)と、回路情報及び複数の回路素子の配置に基づいて、いずれかの横ライン又は縦ラインの位置を始点として、第1の方向に格子間隔よりも大きい所定の幅を有する第1の配線を配置するステップ(b)と、ステップ(b)において配置された第1の配線に第1の方向と反対の第2の方向において隣接する横ライン又は縦ライン上に、最小幅を有する第2の配線を配置するステップ(c)とを含む。

(もっと読む)

回路設計支援装置、回路設計支援方法および半導体集積回路

【課題】配線の遅延特性のばらつきを抑制すること。

【解決手段】回路設計支援装置1は、設定部1aと生成部1bとを有している。設定部1aは、半導体集積回路モデル2の層2a、2bそれぞれに、積層方向および面方向に隣接するユニット3の配線方向が互いに異なる方向に配線が生成される複数の矩形のユニット3を設定する。生成部1bは、ユニット3の境界で異なる層のユニット3に跨る配線を生成する。

(もっと読む)

半導体装置及びそのレイアウト方法

【課題】良好な伝送性能と小さい配置面積を両立可能なデータバスを備える半導体装置を提供する。

【解決手段】本発明の半導体装置は、配線層M1、M2と、複数のデータ入出力端子と、N本のデータ線(DU、DL)を含むデータバスとを備え、N本のデータ線は所定の配線長の長短に応じた2種類のデータ線群を含む。配線層M1、M2にはデータ線(DL、DU)の各々に隣接する複数のシールド線(Sa、Sb、Sc)が配置され、各データ線(DL、DU)は、配線層M1、M2の積層方向で互いに重ならない位置に配置される。このような配線構造により、各データ線(DL、DU)の間のカップリング容量を抑え、データバスのクロストークを防止することができる。

(もっと読む)

キャパシタおよび半導体装置

【課題】微細化されても高精度を維持できるキャパシタを提供する。

【解決手段】キャパシタは、平面上に交互に配列した、直線状で第1の長さを有し第1の方向に延在する第1の電極パターンと、直線状で前記第1の長さより短い第2の長さを有し、前記第1の方向に延在する第2の電極パタ―ンと、前記第1の電極パターンに第1の電圧を、第1のビアプラグを介して供給する第1の配線パタ―ンと、前記第2の電極パターンに第2の電圧を、第2のビアプラグを介して供給する第2の配線パタ―ンと、を備え、前記第1および第2の電極パターンをそれぞれの前記第1の方向で比較した場合、前記第1の電極パターンの第1の端部が、前記第1の端部に対応する前記第2の電極パターンの第2の端部よりも突出しており、前記第1の電極パターンの前記第1の端部に対向する第3の端部が、前記第3の端部に対応する前記第2の電極パターンの第4の端部よりも突出している。

(もっと読む)

1 - 20 / 319

[ Back to top ]