Fターム[5F064EE22]の内容

ICの設計・製造(配線設計等) (42,086) | 配線 (13,054) | 配線パターン (7,249) | 多層配線 (2,699)

Fターム[5F064EE22]の下位に属するFターム

Fターム[5F064EE22]に分類される特許

561 - 566 / 566

ナノメートルスケールの再構成可能な抵抗器クロスバースイッチを用いたコンピューティングのアーキテクチャ及び方法

コンピューティングのアーキテクチャは、ナノメートルスケールのクロスバースイッチ(100)を含み、これらナノメートルスケールのクロスバースイッチ(100)は、ナノメートルスケールのクロスバースイッチ(100)において論理値をインピーダンスとして符号化する一連のパルスに応答して論理関数を実行するように構成されている。  (もっと読む)

(もっと読む)

半導体装置

【課題】 発熱した半導体素子を効率良く冷却したり、その半導体素子から伝わる熱を速やかに外部に放熱できる半導体装置を提供する。

【解決手段】 半導体装置は、主表面1aを有する半導体基板1と、主表面1a上に形成され、主表面1aに設けられた半導体素子を覆う層間絶縁膜2と、層間絶縁膜2に形成され、冷却用流体が流れる冷却路3とを備える。冷却路3は、層間絶縁膜2の内部を循環するように形成されている。冷却路3は、冷却用流体が供給される一方端4と、冷却用流体が排出される他方端5とを含む。

(もっと読む)

パッド下に素子を備える手法によるウェハの有効利用

半導体構造(20)のパッドエリア(21)下に能動素子(25)を組み込むことにより、シリコンエリアのより効率的な利用を可能とする。パッドエリア(21)は、上方に第1の金属層(23)を備えた基板(22)を含む。第2の金属層(26)は第1の金属層(23)の下とする。能動素子(25)は基板内であって、第2の金属層(26)の下に備えられる。誘導体層(24)は第1の金属層(26)と第2の金属層(23)とを分離する。誘導体層(24)内のビア(27)は第1の金属層(23)と第2の金属層(26)とを電気的に接続する。ビア(27)は能動素子(25)と接続する。隣接金属層(424、425、426)を第1の金属層(23)と第2の金属層(26)の間に配置してもよい。  (もっと読む)

(もっと読む)

製造を容易にする設計

【課題】製造容易性を改善するために、既存の超小型装置設計を変更する技術を提供する。

【解決手段】これらの技術により、設計者は、設計に於けるデータに関連した製造基準を受領する。次に、関連した設計データが識別されて、超小型装置設計者へ供給され、該設計者は、製造基準に基づいて設計変更を選択することが出来る。このようにして、設計者は、超小型装置の元の設計に於いて、半導体ファンドリからの製造基準を直接的に包含させることが出来る。

(もっと読む)

半導体装置とその製造方法およびモノリシックマイクロ波集積回路

【課題】 強度低下や寸法増大を抑えながら、バイアホールの接地インダクタンスを低減できる半導体装置とその製造方法およびMMICを提供する。

【解決手段】 このマイクロ波帯用増幅器GaAsMMICは、その接地電極8が、3個のバイアホール11からなるバイアホール群12を有し、この3個のバイアホール11は、その内側に充填されたメッキ金属10aが近接されて形成され、その相互作用によって高周波的な電磁界結合が発生して、接地インダクタンスが低減された。

(もっと読む)

LSIの配線構造及びその設計方法

【課題】 配線容量C及び配線遅延RCの低減の可能なLSIの配線構造及びその設計方法を提供する。

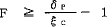

【解決手段】プロセスばらつき量を推定しδPとし、配線容量変動ΔC/Cの許容範囲を設定しδCとし、フリンジ容量CFと平行平板容量CPからフリンジ容量比F=CF/CPを評価して、以下の式

【数1】

を満たすように、前記配線構造が決定される。

(もっと読む)

561 - 566 / 566

[ Back to top ]