Fターム[5F064EE24]の内容

ICの設計・製造(配線設計等) (42,086) | 配線 (13,054) | 配線パターン (7,249) | 多層配線 (2,699) | 固定配線と通過用配線の組み合わせ (44)

Fターム[5F064EE24]に分類される特許

1 - 20 / 44

半導体集積回路

【課題】電荷転送効率が高い転送トランジスタを備える半導体集積回路を提供することを目的とする。

【解決手段】実施形態に係る半導体集積回路は、ゲート電極を有し、当該ゲート電極及び一の拡散層が第1配線でダイオード接続された転送トランジスタと、クロック信号が供給されるクロック信号線とを備え、前記クロック信号線の一部である第1部分クロック信号線の少なくとも一部が前記ゲート電極上に形成されていることを特徴とする。

(もっと読む)

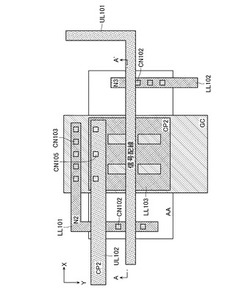

半導体装置の配線構造及びそれを備えた半導体装置

【課題】信号配線が電源配線と長距離に亘って並走することを回避して、信号配線の寄生容量を低減してノイズの影響を低減する半導体装置の配線構造及びそれを備えた半導体装置を提供すること。

【解決手段】第1方向X1に延びる複数の第1配線1Vから構成される第1配線層110と、第1配線層110の上に配設され、第1方向X1に交差する第2方向X2に延びる複数の第2配線2Vから構成される第2配線層120とを備え、第1配線層110および第2配線層120は、第1方向X1および第2方向X2により規定される平面内に設定された配線領域R内に配設され、第1配線1Vは、配線領域Rの第1方向X1における一端から他端までの全長よりも短い長さでそれぞれ形成され、第2配線2Vは、配線領域Rの第2方向X2における一端から他端までの全長よりも短い長さでそれぞれ形成されている半導体装置100の配線構造。

(もっと読む)

半導体集積回路のレイアウト設計方法、プログラム、及びレイアウト設計装置

【課題】チップサイズを縮小可能な半導体集積回路のレイアウト設計方法、プログラム、及びレイアウト設計装置を提供すること。

【解決手段】チップ内にY方向メタルデータを持つプリミティブセルが存在するか判定する工程(ステップB1)と、プリミティブセルが上下に隣接しているか判定する工程(ステップB3)と、各プリミティブセル内のY方向メタルデータを有する層が同じか判定する工程(ステップB4)と、各プリミティブセルのうち移動可能なスペースがあるプリミティブセルがあるか判定する工程(ステップB5)と、各判定を満たす場合に、各プリミティブセルの種類が同じか否かを判定する工程(ステップB6)と、各プリミティブセルの種類に応じてプリミティブセルのX座標の配置位置調整を行う工程(ステップB7、8)と、プリミティブセルの位置を固定する工程(ステップB9)と、を含む。

(もっと読む)

半導体集積回路のレイアウト設計装置および半導体集積回路のレイアウト設計方法、制御プログラム、可読記録媒体、半導体集積回路

【課題】大規模特殊マクロセルのコーナー部近辺の配線を更に高密度に行い、チップサイズを更に縮小しかつチップコストをも低減する。

【解決手段】大規模特殊マクロセル2〜4とスタンダードセルを含む半導体集積回路において、大規模特殊マクロセル2〜4のコーナー部近辺(コーナー領域)の配線を、水平配線および垂直配線をコンタクトを設けることなく同一層で効率よく平行に配置した水平・垂直配線乗換え専用セル5を用いることにより、大規模マクロセル2〜4のコーナー部近辺の配線を更に高密度に行う。

(もっと読む)

半導体集積回路装置の設計方法およびプログラム

【課題】タイミング検証における収束時間を短くしてレイアウト設計の効率化を図る。

【解決手段】ハードマクロとハードマクロを跨ぐ通過用配線とを含み、ハードマクロ内に含まれる複数の交点セル配置領域に関し、通過用配線が交点セル配置領域間を繋ぐ第1の配線と交点セル配置領域内を第1の配線に接続可能となるように繋ぐ第2の配線とを含んで構成される半導体集積回路装置における設計方法である。この設計方法は、全ての交点セル配置領域に関して第1の配線のみを配線した場合(図7のステップS23)のハードマクロにおける第1のタイミング検証を行うステップ(図7のS25)と、全ての交点セル配置領域に関して第2の配線を第1の配線に最大限接続するようにさらに配線した場合(図7のステップS26)のハードマクロにおける第2のタイミング検証を行うステップ(図7のS27)と、を含む。

(もっと読む)

半導体集積回路装置

【課題】スタンダードセルを小型化することのできる技術を提供する。

【解決手段】電源電位Vddを供給し、第1方向に沿って形成された第1タップと、電源電位Vssを供給し、第1方向と交差する第2方向に第1タップと対向して配置され、第1方向に沿って形成された第2タップと、第1タップと第2タップとの間に形成されたスタンダードセル3において、第2方向における第1タップの中心と第2方向における第2タップの中心との間のセルの高さ(距離L)を[(整数+0.5)×第2層目の配線の配線ピッチ]または[(整数+0.25)×第2層目の配線の配線ピッチ]とする。

(もっと読む)

スタンダードセルおよびそれを用いた自動配置配線方法

【課題】半導体装置設計時の自動配置配線における配線ショートによるセル再配置を抑制する。

【解決手段】本発明のスタンダードセルおよびそれを用いた自動配置配線方法は、回路素子が配置される矩形の素子領域11と、素子領域11の対向する2辺と同じ幅で対向する2辺に近接して設けられ、上層配線が配置される矩形の追加配線領域12a、12bを有する。

(もっと読む)

半導体集積回路

【課題】スタンダードセル方式のCMOS半導体集積回路にて、近接位置にある論理ゲートセル間の配線接続においても上層配線の配線資源を消費していたことにより、配線資源不足で論理ゲートセルの敷詰め密度を上げられず、レイアウト面積の増大を招いていた。

【解決手段】論理ゲートセルの端子構造を特別なものとし、論理ゲートセル同士を特定の近接位置に配置したときに、第一および第二の金属配線層のみで配線接続を完結することにより、上層の配線資源を増加させることでレイアウト面積を削減する。

(もっと読む)

半導体集積回路

【課題】マクロセルの集積度を低下させることなく、しかも、マクロセルを迂回して配線する必要もなく、配線効率や動作速度を向上させることができる半導体集積回路を提供する。

【解決手段】マクロセルは、そのファンクションを構成するための配線である内部配線が、最上層側の配線層と最下層側の配線層を用いて形成される。また、最上層側の配線層と最下層側の配線層との間の中間層に、マクロセルのファンクションを構成するための配線ではない外部配線が形成される配線層が設けられている。

(もっと読む)

半導体集積回路装置

【課題】マクロセル上を通過する比較的長い信号配線を形成した場合においてもクロストークノイズの影響を低減し、正常に動作可能な半導体集積回路装置を提供する。

【解決手段】本発明による半導体集積回路装置は、マクロセルが形成されている領域上を通過するように伸長している信号配線に、当該マクロセルとこれに近接する入出力回路との間に形成されたバッファリングセルが接続されている。

(もっと読む)

半導体集積回路

【課題】ESD保護回路上の接続配線の存在に起因する、ESD保護回路近傍における信号配線の混雑を緩和する。

【解決手段】ESD保護回路10に接続される接続配線13,14,15,16は、各配線層の配線優先方向に一致する方向に配置されている。このため、接続配線15が横方向に延びるように配置された配線層には、横方向に延びる信号配線17を配置でき、接続配線14が縦方向に延びるように配置された配線層には、縦方向に延びる信号配線18を配置できる。すなわち、ESD保護回路10上の領域において、接続配線が存在するにもかかわらず、信号配線を横方向にも縦方向にも配置可能になる。

(もっと読む)

セルデータの検証装置、方法、およびプログラム

【課題】個々のセルデータ自体の自動配線への適合性を評価する。

【解決手段】電子装置の他の部分と配線によって接続され、前記電子装置の機能を実現するセルを定義するセルデータの検証装置である。本検証装置は、セルを電子装置の他の部分と接続する端子の定義を含むセルデータを入力する手段と、セルデータの電子装置内での配置を模擬した検証用の配置情報を入力する手段と、配置情報で配置されるセルの端子と接続されるべき相手端子の定義データを生成する手段と、セルデータを配置情報にしたがって配置するとともに、相手端子の定義データを付加したレイアウトデータを作成するレイアウト手段と、自動配線システムにセルデータとレイアウトデータとを入力することによって相手端子から配置されたセルの端子に至る配線データを発生させる、自動配線を起動する手段と、自動配線システムからの自動配線の結果を報知する報知手段とを備える。

(もっと読む)

ソフトマクロを用いたレイアウト設計方法、ソフトマクロのデータ構造及びソフトマクロライブラリの作成方法

【課題】チップの面積増大を抑制し、また、チップレイアウト時のタイミング収束のために繰り返しレイアウトする回数と設計工数を削減する。

【解決手段】相対的な位置が決まっている複数の相対配置位置決定済セル(43)(44)を示す相対配置位置決定済セル情報(31)と、相対的な位置を示す相対位置情報(32)と、複数の相対配置位置決定済セル(43)(44)に対応して配置位置が決まっている配線(45)を示す配置位置決定済配線情報(33)(34)とを有するソフトマクロ(14)を構成する。そして、ネットリスト(11)に基づいて、ICチップにおける配置位置と配線とを決定するときに、相対配置位置決定済セル(43)(44)と配線(45)のレイアウトを変更しないソフトマクロ(14)を構成する。

(もっと読む)

半導体集積回路装置

【課題】IOスロットを無駄にすることなく、内部回路に対して電源供給することが可能な半導体集積回路装置を提供する。

【解決手段】半導体集積回路装置は、配線層を下から第1の共通配線層101a、カスタマイズ層102、第2の共通配線層101bの3層構造とした。第2の共通配線層101bには、外部から電源が供給される電源パッド1aと接続される内部電源ラインが形成されている。内部電源ラインは、電源パッド1aと同一層に形成されるとともに、汎用ロジックセルにより構成される内部回路領域10にまで延在している。

(もっと読む)

集積回路作製装置およびその方法、並びにプログラム

【課題】複数の論理回路を組にしたセルを所定の配列形態をもって配置し、多層配線化する集積回路の作製において、配線接続の変更が容易に実行できる集積回路作製装置およびその方法、並びにプログラムを提供する。

【解決手段】複数の論理回路のうち、初期論理値の変更が予測される第1の順序回路を第2の順序回路に置換する置換部と、置換部によって置換された第2の順序回路の配置後、当該順序回路の所定端子が配線接続可能な複数の配線層のうち、いずれか一の配線層に配線禁止領域を設定する配線禁止領域設定部と、集積回路の設定途中で、置換された第2の順序回路の初期論理値を変更する場合に、当該順序回路の所定端子を配線禁止領域の配線層にて配線接続する配線部とを有する。

(もっと読む)

版数情報保持回路、及び、半導体集積回路

【課題】任意の初期版数からの版数変更が可能な版数情報保持回路を有する半導体集積回路を提供する。

【解決手段】初期版数情報13は、初期版数を出力する。加算器20は、初期版数情報13が出力する初期版数に1を加算した値を出力する。セレクタ21は、初期版数と、加算器20が出力する初期版数+1とを入力し、そのうちの何れかを出力する。セレクタ21は、セレクト条件保持FF12が0クランプソースに接続されているときは、初期版数を出力する。また、セレクト条件保持FF12が1クランプソースに接続されているときは、加算器20より入力する初期版数+1を出力する。HWレビジョン出力制御部22は、セレクタ21が出力する値を、版数値を使用する論理部や、半導体集積回路外部に出力する。

(もっと読む)

半導体装置

【課題】半導体装置を高集積化することのできる技術を提供する。

【解決手段】スタンダードセルCLは、n型ウエル2nに設けられ、金属シリサイド膜で覆われたp+型拡散層3pおよびn+型拡散層4nを有している。p+型拡散層3pはMISトランジスタのソース/ドレインを構成し、n+型拡散層4nはタップTP1を構成する。p+型拡散層3pは、コンタクト7pを介して配線層6aと電気的に接続されており、n+型拡散層4nは、コンタクト7を介して配線層6と電気的に接続されている。また、p+型拡散層3pがn+型拡散層4nと接触している。MISトランジスタのソースノードに給電される電源電位が拡散層と配線層の2層を用いて行われる。

(もっと読む)

クロック供給回路及びその設計方法

【課題】配線混雑を抑制しつつ、各配線層の配線の出来具合に起因するクロックスキューを抑制できるクロック供給回路を提供する。

【解決手段】本発明に係るクロック供給回路は、クロックツリー構造を有し、クロック信号を複数の動作素子216〜223に供給するクロック供給回路200であって、前記クロックツリー構造を構成する複数の駆動素子201〜215と、前段の駆動素子の出力と次段の複数の駆動素子又は動作素子とをそれぞれ接続する複数の接続配線224〜238とを備え、複数の接続配線224〜238は、基準配線層で形成される複数の第1配線224〜237と、前記基準配線層を使用する回路ブロック239上に存在する第2配線238とを含み、第2配線238の回路ブロック239上の配線は、前記基準配線層より上層の所定の配線層で形成される。

(もっと読む)

半導体集積回路のレイアウト設計方法

【課題】高集積化を実現し、ノイズの影響を受けにくい半導体集積回路を開発する際、設計者に負担がかからないように、ハードマクロ(30)を有する半導体集積回路を設計すること。

【解決手段】コンピュータ(1)は、ハードマクロ(30)内の所定領域(31)に対して予め設定されている配線を許容するための条件(23)を取得し(S2、S3)、半導体集積回路を表すレイアウトデータ(7)上に配置される配線の中から、所定領域(31)上を通過する通過配線(40)を検索する(S10)。検索された通過配線(40)の中から、条件(23)を満たす正常通過配線(41)をハードマクロ(30)上に通過させ、条件(23)を満たさない違反通過配線(42)をハードマクロ(30)から迂回させて配線する。この場合、設計者は、条件(23)をコンピュータ(1)に与えればよく、設計者にかかる負担が軽減する。

(もっと読む)

半導体装置の設計方法

【課題】要求特性に応じた性能を発揮する半導体装置を提供することができる半導体装置の設計方法を提供すること。

【解決手段】1つのCMOS世代において、トランジスタ特性に関するパラメータ(トランジスタ・パラメータ5,7)と、前記トランジスタ特性に応じた配線特性に関するパラメータ(配線パラメータ6,8)とを有するデバイス・パラメータのセットを複数設定し、前記複数のセットのなかから、設計対象となる半導体装置の要求特性に応じたセットを選択し、設計を行う。

(もっと読む)

1 - 20 / 44

[ Back to top ]