Fターム[5F064EE47]の内容

ICの設計・製造(配線設計等) (42,086) | 配線 (13,054) | 配線(又は配線間)の物理的性質 (2,766) | 遅延時間 (920)

Fターム[5F064EE47]に分類される特許

1 - 20 / 920

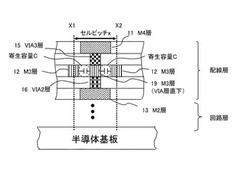

半導体装置の配線構造セルおよび半導体装置のレイアウト設計タイミング調整方法

【課題】複数の動作条件においてもタイミング制約を満たすように遅延時間を調整することを可能にする。

【解決手段】本発明に係る半導体装置の配線構造セルHSCは、M3層に、プロセス基準値bを満たす矩形に形成されたM3層19と、M3層19からプロセス基準値aを満たすよう離間し、口字型に形成されたM3層12と、M3層19の上にプロセス基準値を満たす矩形に形成されたVIA3層15と、M4層にVIA3層15に接して、プロセス基準値cを満たす幅で伸長した矩形に形成されたM4層11と、M3層19の下にVIA3層15と同じ平面形状に形成されたVIA2層16と、M2層にVIA2層16に接して、M4層11と同じ平面形状に形成されたM2層13と、を有するものである。

(もっと読む)

半導体集積回路のレイアウト設計方法

【課題】SETUP時間とHOLD時間のどちらも満足させるタイミングの調整が可能な技術を提供する。

【解決手段】半導体集積回路の配置配線レイアウトを決定した後に、所定の信号線を伝搬するデータのタイミング情報に基づいて、タイミング違反を有する違反データの遅延情報を抽出する。その抽出された遅延情報に基づいて、タイミング違反を解消するための追加すべき容量値を算出する。また、違反データを伝搬する配線のレイアウト配置情報に基づいて、違反データを伝搬する配線の近傍の電源容量セルを検出する。また、算出された容量値に基づいて、検出された電源容量セルを、電源容量セルとレイアウト外形・電源/GND配線配置位置が同じ調整容量セルに置き換える。そして、置き換えた調整用容量セルのゲートと違反データを伝搬する配線とを接続して再配線を実行する。

(もっと読む)

クロック分配回路

【課題】フィードバックパスのバラツキの影響を最小限に抑え、クロックの位相の調整を高精度に行うことができるクロック分配回路を提供する。

【解決手段】クロック分配回路21は、クロック信号を生成するクロック生成回路、前記クロック信号が分配されるクロック分配網22、前記クロック分配網の分岐点N1を通じて分配されるクロック信号で動作する順序回路26、を有する。クロック分配回路は更に、前記分岐点から分岐した前記クロック信号をフィードバック信号として入力し、該入力したフィードバック信号とリファレンスクロック信号とに基づいて、前記クロック信号を前記クロック分配網へ出力するクロック生成回路を有する。前記分岐点は、前記クロック分配網の順序回路の前段のクロックドライバ25のうち、前記クロック生成回路の近傍にあるクロックドライバに設けられる。

(もっと読む)

省面積及び省電力のスタンダードセル方法

【課題】省面積及び省電力のための半導体集積回路の設計方法を提供する。

【解決手段】主回路217と適応電圧用調整回路を含む半導体集積回路であって、適応電圧調整用回路は、クロック信号を受け取るように構成された整合回路211と、整合回路211の出力を受け取り、また、クロック信号を受け取るように構成された位相検出器213と、電源電圧を増加又は減少させるように構成された電圧レギュレータ215とを含み、主回路217は電圧レギュレータ215から電源電圧を受け取るように構成され、整合回路211は電源電圧を受け取って、電源電圧における増加又は減少に基づいて、信号伝搬における遅延を調整するように構成される。

(もっと読む)

レイアウト装置及びレイアウト方法

【課題】クロックツリーにおけるクロックスキューの調整において、精度の確保とデューティ保持とを両立させる。

【解決手段】レイアウト装置(10)において、MOSトランジスタ1段で形成された第1セルと、MOSトランジスタ複数段で形成された第2セルとがライブラリ化されたテーブルを設ける。また、上記レイアウト装置には、上記第1セルと上記第2セルとの組み合わせによるコンビネーションチェーンを上記クロックツリーに挿入することで、上記クロックツリーにおける異なるクロック系統間のクロックスキューを調整可能な演算処理部(12)を設ける。上記コンビネーションチェーンによってクロックスキューの調整を行うことで、個々の第1セルでの遅延誤差が伝播されるのを抑制し、遅延計算における遅延誤差の低減を図る。また、第1セルはMOSトランジスタ1段で形成され、そこで論理反転されるため、デューティ保持の観点で有利とされる。

(もっと読む)

論理回路の故障検出方法、テスト回路挿入方法、テスト回路挿入装置および半導体集積回路

【課題】 論理ゲートの一方の入力を含む信号パスの遅延故障と、論理ゲートの他方の入力を含む信号パスの遅延故障とを、1つの制御点により検出する。

【解決手段】 第1および第2ユーザロジックと、第1ユーザロジックの出力に接続される第1入力を有する第1論理ゲートと、第1論理ゲートの出力に接続された第3ユーザロジックと、第2ユーザロジックと第1論理ゲートとの間に挿入された制御点とを有する。制御点は、第1または第3ユーザロジックの第1スキャンフリップの1つのデータ出力がデータ入力に接続された第2スキャンフリップフロップと、一対の入力が第2スキャンフリップフロップのデータ出力および第2ユーザロジックの出力にそれぞれ接続され、出力が第1論理ゲートの第2入力に接続された第2論理ゲートとを有する。

(もっと読む)

半導体装置および電源供給方法

【課題】消費電力を低減することが可能な半導体装置および電源供給方法を提供することである。

【解決手段】本発明にかかる半導体装置は、内部回路3に電源を供給する電源供給部4と、内部回路3の複数の場所における特性をモニタする複数のモニタ部1_1〜1_Nと、複数のモニタ部1_1〜1_Nから出力された信号C_1〜C_Nに基づき算出されたモニタ値C_AVEと、設定された比較値COMPとの比較結果に応じて電源供給部4を制御する制御部2と、を備える。制御部2は、複数のモニタ部1_1〜1_Nにおける特性のばらつきに応じて比較値COMPを設定する。

(もっと読む)

半導体装置の設計方法、半導体装置の設計プログラム、半導体装置の設計装置

【課題】IRドロップの制約を満たしつつチップレイアウトを小型化できる半導体装置の設計方法、半導体装置の設計プログラム、半導体装置の設計装置を提供すること。

【解決手段】本発明の一態様である半導体装置の設計方法は、複数の電源用パッド及び信号用パッドを、半導体チップ上のチップコアの周囲に配置する。そして、複数の電源用パッド及び信号用パッドの数から決まるチップサイズSpと、チップコアの大きさから決まるチップサイズScと、を比較する。その後、Sp≧Scであれば、IRドロップが制約値を満たす限り、配置した複数の電源用パッドのうちの1又は2以上の電源用パッドを削除する。

(もっと読む)

半導体装置、パラメータ最適化方法、及びプログラム

【課題】トランジスタの容量の各成分や配線容量を分離してパラメータを最適化することが可能な半導体装置、パラメータ最適化方法、及びプログラムを提供すること。

【解決手段】MOSトランジスタから構成されたプリミティブゲート回路11aを奇数段でリング状に結合した第1リングオシレータ部11の各前記プリミティブゲート回路の出力部と電気的に接続された負荷部12となる第1配線を有する配線負荷パターンと、第2リングオシレータ部の各プリミティブゲート回路の出力部が第2配線を介して負荷部となるMOSトランジスタのゲートに電気的に接続された複数のゲート負荷パターンと、第3リングオシレータ部の各プリミティブゲート回路の出力部が第3配線を介して負荷部となる拡散層に電気的に接続された複数の拡散層負荷パターンと、を備え、複数のゲート負荷パターンは、パターンごとに容量負荷が異なり、複数の拡散層負荷パターンは、パターンごとに容量負荷が異なる。

(もっと読む)

集積回路

【課題】電力消費量の増大を抑制しつつ、タイミング信号のスキューを低減する。

【解決手段】主クロック分配回路は、タイミング信号を複数の主タイミング信号に分岐して分配する。副クロック分配回路は、タイミング信号の分配が指示された場合にはタイミング信号を複数の副タイミング信号に分岐して分配する。最小遅延タイミング信号出力部は、複数の主タイミング信号のいずれかと複数の副タイミング信号のいずれかとのうち先に分配された信号を最小遅延タイミング信号として出力する。同期動作回路は、最小遅延タイミング信号に同期して動作する。測定部は、複数の主タイミング信号のいずれかの遅延のばらつきを示す値を測定する。クロック分配回路制御部は、測定された値の示す前記ばらつきが前記所定値以上であるときに副分配回路に前記タイミング信号の分配を指示する。

(もっと読む)

半導体装置

【課題】少しの設計方法の変更で設計できる、一層低消費電力化した半導体装置の実現。

【解決手段】複数の電源供給領域23と、複数の電源供給領域に供給する電源の電圧を切り替える複数の電源切替ユニットSWA,SWBと、を有し、複数の電源供給領域に含まれる回路要素を組み合わせて少なくとも1つの機能ブロックが形成され、少なくとも1つの機能ブロックは、内部に異なる電圧で動作する回路要素を含む半導体装置。

(もっと読む)

集積回路の配線方法、集積回路の配線プログラム及びそれを記憶した記憶媒体

【課題】 要求性能を満たすとともに、消費電力を削減することができる配線方法を提供すること。

【解決手段】 本発明の実施形態による集積回路の配線方法は、所定の動作周波数を満たすように第1の配線を求め、前記所定の動作周波数と前記第1の配線のクリティカルパスとを用いて最大迂回配線長を算出し、集積回路の配線を複数の群に分けた場合に、配線群に含まれる前記第1の配線を、前記第1の配線を含む他の配線群内の配線を用いて迂回させることで第2の配線を求め、前記第2の配線と前記第1の配線との差分が前記最大迂回配線長以下ならば、前記第2の配線によって前記第1の配線を更新し、前記第2の配線と前記第1の配線の差分が前記最大迂回配線長よりも大きければ、前記第1の配線を更新しないことを特徴としている。

(もっと読む)

クロック・ネットワーク・メタ合成のためのシステムおよび方法

【課題】クロック到着時間の同時性を保証するクロック分配ネットワークの設計を容易にする。

【解決手段】クロック・ネットワークを構築する方法は、クロック・ネットワークについての設計仕様を受け取る段階を含む。本方法はさらに、前記設計仕様に基づいて前記クロック・ネットワークのトポロジーを決定する段階を含む。本方法はさらに、決定されたトポロジーに基づいて前記クロック・ネットワークについての設計パラメータを決定し、前記設計パラメータを含むクロック・ネットワーク合成ツール仕様ファイルを生成することを含む。本方法はまた、前記仕様ファイルを使って、前記クロック・ネットワークが前記決定されたトポロジーを含み、前記クロック・ネットワークがクロック発生器から前記クロック・ネットワークのエンドポイントまでクロック信号を同期的に分配するよう、前記クロック・ネットワークを合成することを含む。

(もっと読む)

フロアプラン作成情報生成方法、フロアプラン作成情報生成プログラム、フロアプラン作成情報生成装置、フロアプラン最適化方法、フロアプラン最適化プログラム及びフロアプラン最適化装置。

【課題】フロアプラン設計におけるイタレーションを防ぎ、設計期間を短縮する。

【解決手段】複数の回路モジュールの接続情報を含むネットリストと、前記複数の回路モジュールにグループを設定するためのグループ設定情報と、を記憶部に記憶し、ネットリスト及びグループ設定情報に基づき、複数の回路モジュールにグループを設定し(S21)、設定されたグループ間におけるタイミング制約を満たす距離を算出し(S23)、算出されたグループ間の距離を含み、フロアプランを作成するためのフロアプラン作成情報を生成する(S25)。

(もっと読む)

半導体集積回路設計方法

【課題】LSIに搭載された複数のマクロ間のクロックスキューを低減する設計方法を提案する。

【解決手段】本発明の半導体集積回路設計方法は、複数の下層回路を含む集積回路の回路情報に基づいて、下層回路に含まれるフリップフロップにクロックを供給する論理回路の出力をクロックポイントとして抽出し、抽出したクロックポイントを出力とする論理回路の回路構成を認識し、抽出したクロックポイントのうち、第1下層回路からクロックポイントを選択し、第2下層回路からクロックポイントを選択し、それぞれのクロックポイントを出力とする論理回路の回路構成を比較し、比較結果が一致した場合、選択された2つクロックポイントを出力する論理回路の一方を削除すると共に、削除した一方のクロックポイントを他方の論理回路の出力とすることにより、2つのクロックポイントを共通化する。

(もっと読む)

配置配線装置

【課題】効率的にIR−Dropを防止することが可能な配置配線装置を提供すること。

【解決手段】複数のセルを配置した後、セル間の隙間が所定の大きさよりも小さい場合にはセル間の隙間が所定の大きさ以上となるようにセルの配置を変更する(S17)。そして、配置された複数のセルの間に容量セルを挿入し(S15)、配置された複数のセルの配線を行なう(S14,S16)。したがって、効率的にIR−Dropを防止することが可能となる。

(もっと読む)

遅延時間計算プログラム、装置及び方法

【課題】遅延時間計算プログラム、装置及び方法において、回路におけるネットの遅延時間を高精度に計算することを目的とする。

【解決手段】回路内のネットの遅延時間を計算する遅延時間計算処理は、ネットが第1の条件を満たす場合にネットの遅延時間を計算するための第1の遅延計算手順を選択する第1の手順と、第1の手順で第1の遅延計算手順が選択されない場合、第2の条件をネットが満たすか否かに応じて、第1の遅延計算手順及びネットの遅延時間を計算するための第2の遅延計算手順のいずれか一方を選択する第2の手順と、第1の手順或いは第2の手順のいずれかで選択された遅延計算手順によりネットの遅延時間を計算する第3の手順を含むように構成する。

(もっと読む)

クロック設計方法、クロック設計プログラム

【課題】半導体集積回路のクロック設計において、異なる2種類のクロック間の「セル遅延と配線遅延の比率α」の差を抑制する。

【解決手段】半導体集積回路は、第1クロック(CLK1)が供給される第1素子群と、第1クロック(CLK1)と異なる第2クロック(CLK2)が供給される第2素子群と、を備える。クロック設計方法は、第1クロック(CLK1)に関するクロックツリーシンセシスを実施することによって、第1クロックツリー構造10を作成するステップと、第1クロックツリー構造10の少なくとも一部を流用することによって、第2素子群に第2クロック(CLK2)を供給する第2クロックツリー構造20を作成するステップと、を含む。

(もっと読む)

電源電圧設定方法及び電源電圧設定プログラム

【課題】チップごとに適正な電源電圧を設定する。

【解決手段】チップのレイアウトデータ20からクリティカルパスのゲート遅延と配線遅延の遅延比を抽出する(ステップS1,S2)。チップのモニタ回路で実測されたゲート遅延及び配線遅延を、その遅延比に基づき合成して第1遅延値を生成し(ステップS3)、モニタ回路のシミュレーションで得られるゲート遅延及び配線遅延を、その遅延比に基づき合成して第2遅延値を生成する(ステップS4,S5)。このようにゲート遅延、配線遅延、クリティカルパスでの遅延比が考慮された第1遅延値及び第2遅延値に基づいて、チップに適用するチップ電源電圧を設定する(ステップS7)。

(もっと読む)

半導体集積回路設計支援装置、半導体集積回路設計方法およびプログラム

【課題】レイアウト設計において、複数のI/Oバッファセルを2列以上に配列する場合、I/Oバッファ領域の近傍にリピータを挿入する領域を確保し、手戻りをできるだけ抑えることができる、半導体集積回路設計支援装置、半導体集積回路設計方法およびプログラムを提供する。

【解決手段】リピータを含まないフィルセル(FC)と、リピータを含むフィルセル(FCR)とが用いられる。フィルセル(FC)は、同列で互いに隣接したI/Oバッファセル(Bm=1、n、Bm=1、n+1など)間に配置される。なお、複数のI/Oバッファセルは、2列に配置されている。I/Oバッファセルからプリミティブセルまでの配線長に基づいて、すでに配置されているフィルセル(FC)が、リピータを含むフィルセル(FCR)に置換される。

(もっと読む)

1 - 20 / 920

[ Back to top ]