Fターム[5F064FF24]の内容

ICの設計・製造(配線設計等) (42,086) | 切り換え、選択 (3,709) | 切り換え、選択部分の素子 (1,619) | トランジスタ (97) | FET (85)

Fターム[5F064FF24]に分類される特許

1 - 20 / 85

半導体装置

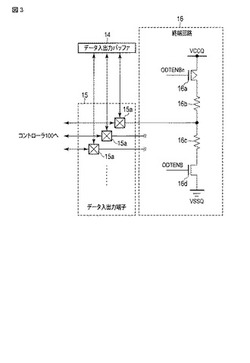

【課題】高品質な半導体装置を提供する。

【解決手段】第1の絶縁膜111、第1の電極112、第2の絶縁膜113、及び第2の電極114を含むゲート構造を有するメモリセルMCが複数設けられた記憶部11と、少なくとも外部100からのデータを受信し、記憶部にデータを供給する端子15と、第1の絶縁膜、第1及び第2の電極とを含むゲート構造を有し、電流経路の一端に第1の電圧が印加される第1導電型の第1のトランジスタ16a、一端が第1のトランジスタの電流経路の他端に接続され、他端が端子に接続される第1の抵抗素子16b、一端が端子及び第1の抵抗素子の他端に接続される第2の抵抗素子16c及び、ゲート構造を有し、電流経路の一端が第2の抵抗素子の他端に接続され、電流経路の他端に第2の電圧が印加される第2導電型の第2のトランジスタ16dを含む第1の回路16と、を備える。

(もっと読む)

半導体集積回路装置

【課題】過電圧がLSIの電源端子に印加されたことを確認できるようにする。

【解決手段】半導体集積回路装置(10)は、内部回路(11)と、上記内部回路に電源電圧を供給するための電源端子(15,16)とを含む。このとき、上記内部回路の電源電圧として想定されるレベルを越える電圧(過電圧)が上記電源端子に印加された事実を記録するための過電圧印加情報記録回路(12)を設ける。過電圧印加情報記録回路には、過電圧が上記電源端子に印加された事実が記録されているため、それに基づいて、過電圧がLSIの電源端子に印加されたことを確認することができる。

(もっと読む)

半導体集積回路装置

【課題】電源遮断領域の信号配線の自由度を低下させないで、電源遮断用スイッチから電源遮断領域に至る電圧伝達経路における電圧降下を抑える。

【解決手段】半導体集積回路装置(80)は、電源遮断用スイッチ(90)と電源遮断領域(763)とが形成された半導体チップ(22)とを含む。半導体チップは基板(21)に結合される。上記電源遮断領域の外側に上記電源遮断用スイッチを配置することで、電源遮断領域内の配線チャネル数の低減を回避する。そして上記基板には、上記半導体チップ内から上記電源遮断用スイッチを介して上記半導体チップの外に伝達された電源電圧を再び上記半導体チップ内に伝達して上記電源遮断領域へ給電するための基板側給電路(30)を形成することで、上記電源遮断用スイッチと上記電源遮断領域との間の電圧降下を抑える。

(もっと読む)

半導体装置

【課題】プログラマブルなアナログデバイスを提供する。また、電源電位の供給が遮断されたときでもデータの保持が可能で、且つ、低消費電力化が可能なアナログデバイスを提供する。

【解決手段】アナログ素子を含むユニットセルにおいて、ユニットセルのスイッチとして、第1乃至第4のトランジスタを用い、第1のトランジスタと第2のトランジスタとが接続された第1のノード、及び、第3のトランジスタと第4のトランジスタが接続された第2のノードの電位を制御することで、ユニットセルの出力を導通状態、非導通状態、又はアナログ素子を介した導通状態のいずれかに切り替える半導体装置を提供する。

(もっと読む)

半導体装置

【課題】FETの駆動力性能や遮断性能などを向上できる半導体装置を提供する。

【解決手段】半導体装置は、半導体基板と、前記半導体基板上に形成され、オフ状態とオン状態とで閾値電圧を可変させるFETからなる半導体素子と、を備える。前記半導体素子は、前記半導体基板のチャネル形成箇所の上方に形成される絶縁膜と、前記絶縁膜の上方に配置されるゲート電極と、前記絶縁膜と前記ゲート電極との間に介挿され、前記チャネルとの間よりも、前記ゲート電極との間で、より多くの電子の授受を行なうチャージトラップ膜と、を有する。

(もっと読む)

半導体装置及びその製造方法

【課題】半導体装置の製造後におけるチャージ蓄積用素子からのチャージの放電を防止してデバイス機能素子のチャージダメージを低減する半導体装置及びその製造方法を提供する。

【解決手段】 半導体基板上に形成されたデバイス機能素子と、半導体基板上に形成されたチャージ蓄積用素子と、半導体基板上に形成され、デバイス機能素子とチャージ蓄積用素子との間に接続され、電気的に書き換え可能な不揮発性メモリトランジスタにより形成された分離用素子とを有する。

(もっと読む)

半導体装置

【課題】ドライバの故障による出力異常を救済することが可能な故障検出救済回路を含んだ半導体装置を提供すること。

【解決手段】故障検知部1は、ドライバ10の出力の期待電位の逆電位となるようにドライバ10の出力にプルアップ抵抗15またはプルダウン抵抗18を接続し、ドライバ10の入力電位と出力電位とを比較することによりドライバ10の故障を検出する。故障救済部2は、故障検知部1によってドライバ10の故障が検出された場合に、期待電位と同電位となるようにドライバ10の出力にプルアップ抵抗26またはプルダウン抵抗29を接続してドライバ10の故障を救済する。したがって、ドライバ10の故障による出力異常を救済することが可能となる。

(もっと読む)

半導体装置

【課題】半導体装置の電源線および接地線の高抵抗化を抑制する。

【解決手段】第1の方向に延伸された第1の回路セル列及び第2の回路セル列と、第1の方向に延伸され、第1の回路セル列上に配置され、第1の電源線には第1の電源電位が供給される、第1及び第2の電源線と、第1の方向に延伸され、第2の回路セル列上に配置され、第2の電源電位が供給される第3の電源線と、第2の電源線と第3の電源線との間に接続され、導通状態において第2の電源線と第3の電源線とを接続して第3の電源線から第2の電源線に第2の電源電位を供給し、非導通状態において第2の電源線と第3の電源線とを電気的に切り離す第1のトランジスタと、第1の回路セル列に配置され、第1の電源線から供給される第1の電源電位と第2の電源線から供給される第2の電源電位との間の電源電圧で動作する第1の回路素子とを備える。

(もっと読む)

不揮発性半導体記憶装置

【課題】レイアウト面積の増大を抑制しつつ、容量を拡張することが可能な不揮発性半導体記憶装置を提供する。

【解決手段】メモリセルに複数のアンチヒューズ素子F1、F2を設け、各アンチヒューズ素子F1、F2の電界効果トランジスタのゲートを互いに接続することで、アンチヒューズ素子F1、F2の一端をノードAに共通に接続し、メモリセルを多値化する。

(もっと読む)

不揮発プログラマブルロジックスイッチ

【課題】 誤動作を防ぐとともに、サイズが小さい不揮発プログラマブルロジックスイッチを提供すること。

【解決手段】 本発明の実施形態による不揮発プログラマブルロジックスイッチは、制御ゲートが第1の配線に接続され、第1のソースドレイン端が第2の配線に接続され、電荷を蓄積する膜を有する第1のメモリセルトランジスタと、制御ゲートが前記第1の配線に接続され、第3のソースドレイン端が前記第1のメモリセルトランジスタの第2のソースドレイン端に接続され、第4のソースドレイン端が第3の配線に接続され、電荷を蓄積する膜を有する第2のメモリセルトランジスタと、前記第1のメモリセルトランジスタの前記第2のソースドレイン端と前記第2のメモリセルトランジスタの前記第3のソースドレイン端にゲート電極が接続されたパストランジスタと、前記パストランジスタのウェルに基板電圧を印加する第1の基板電極を有する。

(もっと読む)

半導体装置およびその動作方法

【課題】省面積化を図ることが可能な半導体装置およびその動作方法を提供する。

【解決手段】各記憶素子21は、P型の半導体層211Pと、半導体層211P内で互いに分離するように配設されたN型の半導体層212N,213Nと、半導体層212Nと電気的に接続された電極215Aと、半導体層213Nと電気的に接続された電極215Bとを有する。駆動対象の記憶素子21に対して、電極215Aと電極215Bとの間に所定の閾値以上の電圧V1を印加して、半導体層212Nと半導体層213Nとの間の領域にそれらの半導体層同士を電気的に繋ぐ導電パスであるフィラメント210を形成することにより、情報の書き込み動作を行う。

(もっと読む)

半導体装置およびその製造方法

【課題】電気ヒューズまたはアンチヒューズの保持特性を高める。

【解決手段】半導体装置100は、半導体基板と、該半導体基板の上部に設けられた電気ヒューズ200とを備える。電気ヒューズ200は、直列に接続された第1のヒューズリンク202および第2のヒューズリンク204と、第1のヒューズリンク202の一端および他端にそれぞれ設けられた第1の電流流入/流出端子(第1の端子206)および第2の電流流入/流出端子(第2の端子208)と、第2のヒューズリンク204の一端および他端にそれぞれ設けられた第3の電流流入/流出端子(第2の端子208)および第4の電流流入/流出端子(第3の端子210)とを含む。

(もっと読む)

半導体装置のトリミング方法、及びトリミング制御回路

【課題】スイッチ素子の製造バラツキを排除し、より均一で確実な溶断が行える半導体装置のトリミング方法、及びトリミング制御回路を提供すること。

【解決手段】電位が異なる第1電源(電源端子c)と第2電源(接地端子d)との間にて直列接続された第1スイッチ素子S1〜S3およびフューズF1〜F3を内蔵した半導体装置101における第1スイッチ素子S1〜S3をオン制御することでフューズF1〜F3に電圧を印加してフューズF1〜F3を溶断する半導体装置101のトリミング方法であって、第1スイッチ素子S1〜S3をターンオン制御することにより、第1電源(電源端子c)からフューズF1〜F3を溶断させない第1電圧値を所定時間印加するステップと、第1電圧値の印加が完了した後、第1電源(電源端子c)からフューズF1〜F3を溶断させる第2電圧値を印加するように切り替えるステップと、を含む。

(もっと読む)

半導体装置及びその駆動方法

【課題】現行プロセスを用いて追加工程なしに製造でき、高い信頼性を有する多値化された電気ヒューズを有する半導体装置を提供する。

【解決手段】第1フィラメントFS1と、第1フィラメントFS1に接続された第2フィラメントFS2とを有する電気ヒューズ素子を有し、第1フィラメントFS1の第2フィラメントFS2との接続端と反対の端部に接続された第1フィラメントFS1と第2フィラメントFS2の直列抵抗を読み出す直列読み出し部RDSとを有する構成とする。

(もっと読む)

集積回路、集積回路設計装置及び集積回路設計方法

【課題】電圧が供給される電源の数が増大するのを抑えることが可能な集積回路を提供する。

【解決手段】開示の集積回路は、第1及び第2の電源配線と、フリップフロップ回路と、スイッチ素子とを備える。第1及び第2の電源配線は共通の電源に接続されている。フリップフロップ回路は、集積回路に対する電源からの電圧供給が停止された場合であっても、データを保持することが要求される。当該フリップフロップ回路は、第1の電源配線に接続されている。スイッチ素子は、例えばトランジスタスイッチであり、電源から電圧を供給するか否かを切り替えるためのものである。スイッチ素子は第2の電源配線に設けられている。

(もっと読む)

半導体集積回路及び半導体集積回路の電源スイッチ制御方法

【課題】電源スイッチを非導通状態から導通状態に遷移させる時間を最適化できる半導体集積回路及びその電源スイッチ制御方法を提供する。

【解決手段】共通電源配線と、第1の回路と、それぞれ電源スイッチ制御信号に基づいて導通、非導通が制御され共通電源配線と第1の回路との間を並列に接続する複数の電源スイッチと、電源スイッチ制御信号と複数の電源スイッチとの間に接続され電源スイッチ制御信号が非導通状態から導通状態に遷移するときに電源スイッチ制御信号の遷移をそれぞれ異なった遅延時間だけ遅延させて複数の電源スイッチに伝え複数の電源スイッチをそれぞれ時間をずらして非導通状態から導通状態に遷移させる遅延回路と、各遅延回路の遅延時間の増減を制御する遅延時間制御部と、を備える。

(もっと読む)

プログラマブル論理集積回路

【課題】 異なったLVTTL I/O規格に対して互換性を持つように集積回路の各I/Oを個別に再構成する回路を提供する。

【解決手段】 上述課題は1つのI/O電源電圧のみを用いて達成でき、この電圧は特定の用途に要求されるI/O電圧のうち最も高いものである。回路はI/Oセルの出力電圧を、適合されるべきLVTTL規格のVOHよりも高く最高VIHよりも低くなるように調節することによって動作する。I/Oセルは、I/O電源電圧とパッドの間に接続されるプルアップトランジスタと、該パッドの電圧と対応の規格に応じた基準電圧とを差動増幅する差動増幅器と、差動増幅器の出力信号と出力制御信号とにプルアップトランジスタを選択的にオン状態とするロジックゲートを備える。各I/Oセルは別個に再構成可能であるため、任意のI/Oを任意のLVTTL仕様に適合させることができる。

(もっと読む)

アンチヒューズ素子のプログラム方法および半導体装置

【課題】書込前後の電流値の比を大きくして、アンチヒューズ素子の書込状態を精度よく判定する。

【解決手段】トランジスタにより構成されているアンチヒューズ素子101のプログラム方法は、ゲート電極112に所定のゲート電圧を印加して、ゲート絶縁膜110を破壊するとともに、不純物拡散領域104aおよび不純物拡散領域104bの少なくとも一方の表面に形成されたシリサイド層106aまたはシリサイド層106bを構成するシリサイド材料をゲート絶縁膜110中に移動させて、ゲート電極112と不純物拡散領域104aおよび不純物拡散領域104bの少なくとも一方とをシリサイド材料122を介して電気的に接続する工程を含む。

(もっと読む)

半導体装置の製造方法及び半導体装置

【課題】迅速かつ精度よくパルス幅エラーを解消することが可能な半導体装置の製造方法を提供する。

【解決手段】半導体装置の設計工程において、クロック信号の立ち上がり及び立ち下がりの遅延量を別々に調整することでクロック信号のパルス幅を調整するパルス幅調整回路を含む回路ブロックを配置し(ステップS2)、パルス幅を検査し(ステップS7,S8)、パルス幅に異常が検出された場合、パルス幅調整回路によりパルス幅を調整する(ステップS9)。

(もっと読む)

半導体装置

【課題】異なる電圧で動作する回路を備えた半導体装置において、面積の増加を抑制することのできる半導体装置を提供する。

【解決手段】半導体装置は、外部端子10に接続され、該外部端子から入力される第1電圧で動作する第1回路20と、外部端子に抵抗素子を介して接続され、第1電圧より絶対値が小さい第2電圧で動作する第2回路40と、抵抗素子と第2回路との間の第1ノードに接続され、制御信号により導通と非導通とのいずれか一方が選択される分圧素子と、を具備する。分圧素子は、第1電圧が外部端子に印加され第1回路を動作させる場合、制御信号により導通状態が選択される。

(もっと読む)

1 - 20 / 85

[ Back to top ]