Fターム[5F064FF28]の内容

ICの設計・製造(配線設計等) (42,086) | 切り換え、選択 (3,709) | 切り換え、選択部分の素子 (1,619) | フューズ (1,286) | 接続するもの (150)

Fターム[5F064FF28]に分類される特許

1 - 20 / 150

半導体ウエハ、半導体装置、および、半導体装置の製造方法

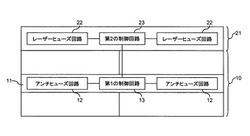

【課題】半導体チップのチップ面積の削減を図るとともに、半導体チップへの入力を記憶させる時間を短縮する。

【解決手段】本発明の半導体ウエハ1は、チップ領域10に形成され、絶縁膜を有し、電圧の印加による絶縁膜の絶縁破壊により導通状態となる複数のアンチヒューズ14を有するアンチヒューズ回路12と、チップ領域10を区画するダイシング領域20に複数のアンチヒューズ14の各々に対応して形成され、配線を有し、レーザー照射による配線の切断により非導通状態となる複数のレーザーヒューズ24を有するレーザーヒューズ回路22と、複数のアンチヒューズ14のうち、半導体チップへの入力に応じて非導通状態とされたレーザーヒューズ22に対応するアンチヒューズ14の有する絶縁膜に、電源からの電圧を印加させて、そのアンチヒューズ14を導通状態とする制御回路13と、を有する。

(もっと読む)

ヒューズ、半導体装置、半導体装置の製造方法

【課題】高電圧が不要で安定した状態を得ること。

【解決手段】半導体装置10に形成されたヒューズ素子11は、概略的に、拡散領域22と、拡散領域22と一部重なるように拡散領域22より上方に形成された導電体25を含む。半導体装置10の半導体基板21には、拡散領域22が形成されている。半導体基板21には素子分離領域23が形成されている。拡散領域22を含む半導体基板21上には絶縁膜24が形成されている。絶縁膜24上には、導電体25が形成されている。導電体25上には、カバー膜26が形成されている。カバー膜26は、導電体25の上面及び側面を覆うように形成されている。カバー膜26は、絶縁膜24より高い引っ張り応力を持つ。

(もっと読む)

カップリングチャネルを使用したアンチヒューズメモリ及びその操作方法

【課題】カップリングチャネルを使用したアンチヒューズメモリ及びその操作方法を提供する。

【解決手段】カップリングチャネルを使用したアンチヒューズメモリは、第1導電型の基板と、第2導電型のドープ領域と、カップリングゲートと、ゲート誘電層と、アンチヒューズゲートと、アンチヒューズ層と、を含む。基板中に隔離構造を有する。ドープ領域が基板中に設置され、且つドープ領域及び隔離構造の間にチャネル領域を定義する。カップリングゲートがドープ領域及び隔離構造の間の基板上に設置され、且つカップリングゲートとドープ領域と隣り合う。ゲート誘電層がカップリングゲート及び基板の間に設置される。アンチヒューズゲートがカップリングゲート及び隔離構造の間の基板上に設置され、アンチヒューズゲート及びカップリングゲートの間に間隔を有する。アンチヒューズ層がアンチヒューズゲート及び基板の間に設置される。

(もっと読む)

半導体装置および判定方法

【課題】ヒューズの切断または非切断をより正しく判定することが可能な半導体装置および判定方法を提供する。

【解決手段】半導体装置は、ヒューズの切断または非切断の判定を行う半導体装置であって、多数のヒューズと、多数のヒューズのうち切断状態である切断ヒューズの数が所定の切断閾値を超える場合には、ヒューズの切断を示す切断信号を出力し、切断ヒューズの数が切断閾値よりも小さい場合には、ヒューズの非切断を示す非切断信号を出力する判定回路と、を含む。

(もっと読む)

半導体装置

【課題】ウエハーテストにおいて、キャリブレーション動作の評価を、容易、かつ高精度に行うことができる半導体装置を提供する。

【解決手段】キャリブレーション端子ZQを駆動するレプリカバッファ(131)と、レプリカバッファの出力インピーダンスを変化させる際に目標となるインピーダンスが設定され、キャリブレーション端子ZQに接続される可変インピーダンス回路(170)と、を備える。

(もっと読む)

不揮発性半導体記憶装置

【課題】レイアウト面積の増大を抑制しつつ、容量を拡張することが可能な不揮発性半導体記憶装置を提供する。

【解決手段】メモリセルに複数のアンチヒューズ素子F1、F2を設け、各アンチヒューズ素子F1、F2の電界効果トランジスタのゲートを互いに接続することで、アンチヒューズ素子F1、F2の一端をノードAに共通に接続し、メモリセルを多値化する。

(もっと読む)

半導体装置およびその動作方法

【課題】省面積化を図ることが可能な半導体装置およびその動作方法を提供する。

【解決手段】各記憶素子21は、P型の半導体層211Pと、半導体層211P内で互いに分離するように配設されたN型の半導体層212N,213Nと、半導体層212Nと電気的に接続された電極215Aと、半導体層213Nと電気的に接続された電極215Bとを有する。駆動対象の記憶素子21に対して、電極215Aと電極215Bとの間に所定の閾値以上の電圧V1を印加して、半導体層212Nと半導体層213Nとの間の領域にそれらの半導体層同士を電気的に繋ぐ導電パスであるフィラメント210を形成することにより、情報の書き込み動作を行う。

(もっと読む)

半導体装置およびその動作方法

【課題】省面積化を図ることが可能な半導体装置およびその動作方法を提供する。

【解決手段】各記憶素子21は、P型の半導体層211Pと、半導体層211P内で互いに分離するように配設されたN型の半導体層212N,213Nと、半導体層211P上の半導体層212N,213N間に対応する領域に設けられた下層側の誘電体膜216および上層側の導電体膜217と、半導体層212Nと電気的に接続された電極215Aと、半導体層213Nと電気的に接続された電極215Bと、導電体膜217と電気的に接続された電極215Cとを有する。駆動対象の記憶素子21に対して、電極215B,215C間に所定の閾値以上の電圧V1を印加して、誘電体膜216の少なくとも一部分を絶縁破壊させて導電体膜217,半導体層213N間に電流を流し、半導体層212N,213N間の領域にフィラメント210を形成することにより、情報の書き込み動作を行う。

(もっと読む)

一方向性アンチヒューズ素子及びこれを用いた発光ダイオードユニット

【課題】1列に直列接続された各発光ダイオード(LED)素子の各々にそれぞれ1つのアンチヒューズ素子が並列接続されているLEDユニットにおいて、電源を誤って逆方向に接続した場合にも、LEDユニットを保護する一方向性アンチヒューズ素子を提供する。

【解決手段】1はカソード電極端子Kに接続されたカソード電極層、2はp型不純物層21及びn型不純物層22よりなる半導体層、3は絶縁層、4はボンディングワイヤ5によってアノード電極端子Aに接続されたアノード電極層、6は封止樹脂層である。カソード電極端子Kとアノード電極端子Aとの間に順方向電圧が印加された場合のみ、一方向性アンチヒューズ素子はアンチヒューズとして作用する。カソード電極端子Kとアノード電極端子Aとの間に逆方向電圧が印加された場合には、一方向性アンチヒューズ素子はアンチヒューズとして作用しない。

(もっと読む)

半導体装置

【課題】回路特性を調整するためのトリミング時間を短縮する。

【解決手段】切断ポイントが座標Y1に配列されたラダーヒューズLFAと、切断ポイントが座標Y2に配列されたラダーヒューズLFBとを備える。回路特性を調整するための補正データが第1の範囲内にある場合はラダーヒューズLFA,LFBの両方に対してトリミング動作を行い、回路特性を調整するための補正データが第2の範囲内にある場合はラダーヒューズLFAに対してトリミング動作を行うことなく、ラダーヒューズLFBに対してトリミング動作を行う。これにより、補正データが第2の範囲内である場合には、ラダーヒューズLFAに対してレーザ照射する必要がない。このため、例えば量産段階で必要となる調整範囲をラダーヒューズLFBに割当てれば、1回のスキャンでトリミングを完了することが可能となる。

(もっと読む)

半導体装置

【課題】電源ノイズを一層効果的に解消する技術を提供する。

【解決手段】半導体装置1は、所定動作を実行するための内部回路6と、内部回路6に対して高電位電圧を供給するための電源ライン7と、内部回路6に対して低電位電圧を供給するためのグラウンドライン8と、ウェハテスト用電極パッド9と、ウェハテスト用電極パッド9を内部回路6に接続するための電気線10と、電気線10を内部回路6に対して非導通状態にすると共に、電気線10を電源ライン7とグラウンドライン8のうち何れか一方に対して選択的に導通状態とする接続切替部11と、を備える。

(もっと読む)

半導体装置およびその製造方法

【課題】電気ヒューズまたはアンチヒューズの保持特性を高める。

【解決手段】半導体装置100は、半導体基板と、該半導体基板の上部に設けられた電気ヒューズ200とを備える。電気ヒューズ200は、直列に接続された第1のヒューズリンク202および第2のヒューズリンク204と、第1のヒューズリンク202の一端および他端にそれぞれ設けられた第1の電流流入/流出端子(第1の端子206)および第2の電流流入/流出端子(第2の端子208)と、第2のヒューズリンク204の一端および他端にそれぞれ設けられた第3の電流流入/流出端子(第2の端子208)および第4の電流流入/流出端子(第3の端子210)とを含む。

(もっと読む)

ヒューズ回路

【課題】ヒューズ回路の2つの出力側にそれぞれ所期の論理値に設定された論理信号出力する。

【解決手段】ヒューズ回路10は、電圧源VDDと、第1主電極、第2主電極、及び制御電極を有する第1及び第2のトランジスタQ11,Q12と、電圧源と第1のトランジスタのソースSとの間に直列に配置される第1の電気ヒューズRf1と、電圧源と第2のトランジスタのソースとの間に直列に配置される第2の電気ヒューズRf2を備える。さらに、第1,第2の電力供給回路Q13,Q14と、第1及び第2のトランジスタのドレインD側から論理値出力を取り出す第1及び第2の出力X,Yを備える。

(もっと読む)

半導体装置及びその制御方法

【課題】様々な導通状態にある複数の電気ヒューズを有する半導体装置において、複数の電気ヒューズによりプログラミングされた結果を誤判定なく読み出すことのできる半導体装置及び半導体装置の制御方法を提供する。

【解決手段】其々がプログラム状態又は非プログラム状態である複数のヒューズ素子と、複数のヒューズ素子のプログラム状態又は非プログラム状態に対応する判定結果信号FLDa,FLDbを其々出力する複数のヒューズ判定回路92a,92bと、第1のタイミング信号LOAD_ENDを共通に受け、第1のタイミング信号LOAD_ENDに同期して複数の判定結果信号FLDa,FLDbを其々ラッチ及び出力する複数のラッチ回路93a,93bとを備える。

(もっと読む)

半導体装置及びその制御方法

【課題】様々な導通状態にある電気ヒューズを其々誤判定なく読み出すことのできる半導体装置及び半導体装置の制御方法を提供する。

【解決手段】選択トランジスタ903を介して検出ノードAに接続された電気ヒューズ902と、選択トランジスタ903をオフさせた状態で検出ノードAをプリチャージするプリチャージトランジスタ904と、選択トランジスタ903をオンさせ、プリチャージトランジスタ904をオフさせた状態で、検出ノードAにバイアス電流を流すバイアストランジスタ905と、検出ノードAにバイアス電流が流れている状態で検出ノードAの電位を検出する検出回路906とを備え、バイアストランジスタ905は、バイアス電流の量を段階的又は連続的に減少させる。

(もっと読む)

半導体装置

【課題】ゲート電極へのチャージアップの有無を解析する手法を用いても、書き込まれた情報を解析することができないようにするアンチヒューズをメモリ素子として有する半導体装置を提供する。

【解決手段】基板10は第1導電型、例えばp型の半導体基板(例えばシリコン基板)である。アンチヒューズは、ゲート電極120及び第2導電型拡散層130を有している。第2導電型拡散層130は基板10に形成されており、例えばn型である。第1コンタクト122はゲート電極120に接続している。第2コンタクト142は第1コンタクト122と同一層に形成されており、基板10のうち第2導電型拡散層130が形成されていない領域に接続している。第2コンタクト142は第1コンタクト122に隣接している。

(もっと読む)

半導体装置

【課題】アンチヒューズにおいて、電極へのチャージアップの有無を解析する手法を用いても、書き込まれた情報を解析することができないようにする。

【解決手段】アンチヒューズ12は、ゲート絶縁膜、ゲート電極114、及び第1拡散層116を有している。第2拡散層126は、素子分離膜102を介して第1拡散層116と離間しており、第1拡散層116と同一導電型を有している。ゲート配線124はゲート電極114と一体として形成されており、素子分離膜102上を延伸している。共通コンタクト220は、ゲート配線124と第2拡散層126を接続している。そしてゲート電極114は、第1拡散層116と同一導電型の不純物が導入された半導体、例えばポリシリコンにより形成されている。また第2拡散層126は、共通コンタクト220のみに接続している。

(もっと読む)

半導体集積回路及び制御方法

【課題】LSIの機能増加に伴い外部端子数が増加傾向にある。更に、回路の微細化が進み、パッケージサイズも小型化が進んでいる。このため、LSIの外部端子数の削減が求められている。

【解決手段】本発明は、複数の外部記憶デバイスから1つを選択して、実行プログラムをロードする半導体集積回路であって、複数の内蔵ヒューズ回路を備えるヒューズ部と、前記内蔵ヒューズ回路が示す値に応じて選択した外部記憶デバイスからの実行プログラムをロードする処理部と、を有する半導体集積回路である。

(もっと読む)

半導体装置

【課題】面積を抑えたアンチヒューズ素子を備えた半導体装置を提供する。

【解決手段】半導体装置は、基板10と、第1絶縁膜11と、シリサイド膜12bを含む導電膜12と、コンタクト15と、を具備する。第1絶縁膜は、基板上に形成されている。導電膜は、第1絶縁膜上に形成されている。コンタクトは、基板上に形成され、第2絶縁膜14を介して導電膜に隣接して配置され、シリサイド膜と短絡している。

(もっと読む)

半導体装置及びその製造方法

【課題】メモリセル領域の周辺に金属電極を有するアンチフューズを製造歩留り良く形成する。

【解決手段】MOSトランジスタを備えたメモリセルを有するメモリセル領域と、アンチフューズを備えた周辺回路領域とを有する半導体装置において、メモリセルを構成するコンタクトプラグ又はビット配線と同層に形成される周辺回路のコンタクトプラグ又は配線を用いて、アンチフューズの電極を形成する。

(もっと読む)

1 - 20 / 150

[ Back to top ]