Fターム[5F064FF32]の内容

ICの設計・製造(配線設計等) (42,086) | 切り換え、選択 (3,709) | 切り換え、選択部分の素子 (1,619) | フューズ (1,286) | 材料が特定されているもの (479) | 金属 (257)

Fターム[5F064FF32]の下位に属するFターム

高融点金属 (62)

Fターム[5F064FF32]に分類される特許

1 - 20 / 195

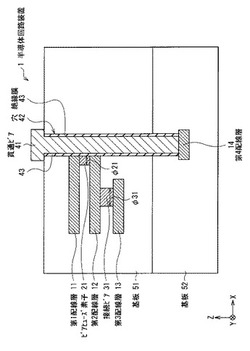

半導体回路装置およびその製造方法

【課題】ビアヒューズ素子の径を小さくし、ビアヒューズ素子を低電流で溶断することが可能な半導体回路装置およびその製造方法を提供する。

【解決手段】一方向に配置された複数の配線層と、前記複数の配線層のうちの少なくとも2つの前記配線層の間に設けられたビアヒューズ素子と、前記複数の配線層の配置方向に直交する平面内において前記ビアヒューズ素子に隣接する穴と、前記穴内に設けられた貫通ビアとを備えた半導体回路装置。

(もっと読む)

半導体装置

【課題】抵抗体とヒューズ素子が並列に接続された半導体装置において、ヒューズ素子切断時に抵抗体への損傷がなく、抵抗体とヒューズ素子とを積層すること。

【解決手段】半導体基板上に第1の絶縁膜を介して形成された抵抗体を設け、抵抗体の上に第2の絶縁膜を介して形成された遮光層を設け、遮光層の上に第3の絶縁膜を介して形成されたヒューズ素子のヒューズ部を有し、抵抗体と遮光層とヒューズ部を重畳した半導体装置とする。

(もっと読む)

半導体集積回路装置

【課題】過電流に対して内部回路を保護する半導体集積回路装置を提供することを目的としている。

【解決手段】多層配線構造を有する半導体集積回路装置であって、半導体集積回路装置の内部にある内部回路と半導体集積回路装置の外部にある外部回路とを接続するために半導体集積回路装置の内部に設けられたパッドパターンにおいて、第1の配線層と、第1の配線層が形成されている層とは別の層に形成されている第2の配線層と、第1の配線層と第2の配線層を接続するビアと、を備え、第2の配線層にヒューズパターンが形成されており、ヒューズパターンを経由して内部回路と外部回路とを電気的に接続する。

(もっと読む)

半導体装置

【課題】レーザートリミングの際に半導体基板のダメージを極力抑えながら導電体を溶断することが可能な半導体装置を提供する。

【解決手段】半導体基板10上にLOCOS絶縁膜11を覆う第1の絶縁膜12が形成され、第1の絶縁膜12上には、LOCOS絶縁膜11の平坦部11F上を通って、レーザートリミングにより溶断される導電体20が形成されている。第1の絶縁膜12及び導電体20を覆って、LOCOS絶縁膜11の平坦部11Fと重畳する領域内に凸レンズ状の凸部13Cを有した第2の絶縁膜13が形成されている。レーザートリミングの際、LOCOS絶縁膜11の平坦部11Fの両側の傾斜部11Sでは、レーザー光が半導体基板10の表面に斜めに入射するように反射されるため、半導体基板10のダメージを回避できる。また、第2の絶縁膜13の凸部13Cは、レーザー光を屈折させて導電体20に集光させる。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】チップ面積を増大させることなく、針ずれに起因する誤測定や誤検査を防止することができる、半導体装置および半導体装置の製造方法を提供する。

【解決手段】半導体装置は、内部回路と、内部回路と電気的に接続されるとともに、検査装置に接続された複数の探針がそれぞれ接触する複数のパッドを備える。少なくとも2つのパッド2a、2bの間に、当該2つのパッド2a、2bを電気的に接続するとともに、所定の電流を印加することにより、恒久的に、電気的に切断されるヒューズ素子4が設けられる。パッド2a、2bの間の抵抗値を測定することで、針ずれの有無を検知することができる。その後、ヒューズ素子を切断し、内部回路の検査が実施される。

(もっと読む)

I/O積層体を含むシステム及びこのシステムを製造する方法

【課題】入出力(I/O)積層体を含むシステムを提供する。

【解決手段】入出力(I/O)積層体を含むシステム及びこのシステムを製造する方法が記述されている。一実装において、本方法は、I/O素子を含むと共に論理素子を含まないI/Oダイを積層するステップを有する。又、一実装において、本方法は、I/Oダイに対して集積回路ダイを積層するステップを更に含む。集積回路は、論理素子を含み、且つ、I/O素子を含まない。集積回路ダイからI/Oダイを分離することにより、それぞれのダイの独立的な開発や従来のダイのものとの比較におけるI/OダイのI/O基板上のI/O素子用の相対的に大きな空間などの様々な利益が得られる。空間の増大により、多数の論理素子を集積回路ダイの基板の同一の表面積内に収容する集積回路ダイの新しいプロセス世代が可能となる。

(もっと読む)

ランダム・アクセス電気的プログラム可能なEヒューズROM

【課題】ランダム・アクセス電気的プログラム可能なeヒューズROMを提供する。

【解決手段】1回プログラム可能な読み出し専用メモリ(OTPROM)が、アグレッシブにスケール縮小された、シリサイド移動可能なeヒューズの2次元配列において実施される。ワード・ライン選択は、VDDにおいて動作するデコード論理によって実施され、一方ビット・ライン・ドライブは、VDDとプログラミングのためのより高い電圧VPとの間でスイッチ切替えされる。OTPROMは、それゆえコストを加算することなしに他の技術と適合可能で、統合することができ、そして、ヒューズ・プログラミングの間、電圧降下を最小にする高電流経路の最適化をサポートする。プログラム可能参照を有する差動センス増幅器は、センス・マージンを改善するために使用され、個々のヒューズに設けられるセンス増幅器の代りに、ビット・ライン全体をサポートすることができる。

(もっと読む)

半導体装置およびその動作方法

【課題】省面積化を図ることが可能な半導体装置およびその動作方法を提供する。

【解決手段】各記憶素子21は、P型の半導体層211Pと、半導体層211P内で互いに分離するように配設されたN型の半導体層212N,213Nと、半導体層211P上の半導体層212N,213N間に対応する領域に設けられた下層側の誘電体膜216および上層側の導電体膜217と、半導体層212Nと電気的に接続された電極215Aと、半導体層213Nと電気的に接続された電極215Bと、導電体膜217と電気的に接続された電極215Cとを有する。駆動対象の記憶素子21に対して、電極215B,215C間に所定の閾値以上の電圧V1を印加して、誘電体膜216の少なくとも一部分を絶縁破壊させて導電体膜217,半導体層213N間に電流を流し、半導体層212N,213N間の領域にフィラメント210を形成することにより、情報の書き込み動作を行う。

(もっと読む)

半導体装置およびその製造方法

【課題】銅を主成分とする配線層を有し、かつヒューズの切断によって特性の悪化を招くことのない半導体装置およびその製造方法を提供する。

【解決手段】半導体装置は、銅を主成分とするメタル配線34と、メタル配線34よりも上層に形成された最上層配線5と、メタル配線34と最上層配線5との間を接続するためのプラグ9が形成されるプラグ形成層10に少なくとも一部が形成され、銅以外の金属材料を主成分とする導電性材料で形成されたヒューズ膜4とを含む。

(もっと読む)

半導体装置の製造方法

【課題】ヒューズ(FUSE)を備えた半導体装置の信頼性を向上する。

【解決手段】半導体基板11の主面上に形成にされた多層配線を構成する層M1〜M6のうちの層M4に設けられた電気溶断型の救済用のヒューズ4aおよび試験用のヒューズ4bと、ヒューズ4aの近傍であって層M2および層M6に設けられた一対の導電板10aと、ヒューズ4bの近傍であって層M3および層M5に設けられた一対の導電板10bとから構成する。ヒューズ4bと導電板10bとの間が、ヒューズ4aと導電板10aとの間より近いものとする。

(もっと読む)

半導体装置およびその製造方法

【課題】電気ヒューズまたはアンチヒューズの保持特性を高める。

【解決手段】半導体装置100は、半導体基板と、該半導体基板の上部に設けられた電気ヒューズ200とを備える。電気ヒューズ200は、直列に接続された第1のヒューズリンク202および第2のヒューズリンク204と、第1のヒューズリンク202の一端および他端にそれぞれ設けられた第1の電流流入/流出端子(第1の端子206)および第2の電流流入/流出端子(第2の端子208)と、第2のヒューズリンク204の一端および他端にそれぞれ設けられた第3の電流流入/流出端子(第2の端子208)および第4の電流流入/流出端子(第3の端子210)とを含む。

(もっと読む)

半導体装置

【課題】半導体装置の特性を向上させる。

【解決手段】本発明の半導体装置は、半導体基板の上方に形成された半導体素子と、半導体素子の上方に形成された第1絶縁膜と、第1絶縁膜上に形成されたアルミニウム(Al)を含有する第1導電性膜よりなるヒューズ素子Fと、を有する。さらに、第1絶縁膜上に形成され、第1導電性膜よりなる第1配線と、第1配線上に形成された第2絶縁膜と、を有し、ヒューズ素子Fのプログラム領域は、第2絶縁膜に設けられた開口部OA1から露出している。また、ヒューズ素子Fのプログラム期間およびヒューズ素子にプログラムされたデータの読み出し期間以外の期間において、ヒューズ素子Fの両端を接地電位に維持する。例えば、ヒューズ素子Fの一端は、接地電位に接続され、他端は、スイッチング素子を介して接地電位に接続されている。

(もっと読む)

ヒューズ回路

【課題】ヒューズ回路の2つの出力側にそれぞれ所期の論理値に設定された論理信号出力する。

【解決手段】ヒューズ回路10は、電圧源VDDと、第1主電極、第2主電極、及び制御電極を有する第1及び第2のトランジスタQ11,Q12と、電圧源と第1のトランジスタのソースSとの間に直列に配置される第1の電気ヒューズRf1と、電圧源と第2のトランジスタのソースとの間に直列に配置される第2の電気ヒューズRf2を備える。さらに、第1,第2の電力供給回路Q13,Q14と、第1及び第2のトランジスタのドレインD側から論理値出力を取り出す第1及び第2の出力X,Yを備える。

(もっと読む)

半導体記憶装置

【課題】 省スペースによって従来よりも多くの論理回路及びヒューズブロックを設けることができる半導体記憶装置を提供する。

【解決手段】 ヒューズ露出窓を介して外部に露出して互いに並置された複数のヒューズ片を各々が含む複数のヒューズブロックがゲートアレイの近傍において縦列に配置され、電源配線と接地配線とが当該ヒューズ片の並置方向に沿って延在しており、ヒューズブロックの配置のために当該ゲートアレイの近傍のスペースを活用した半導体記憶装置。

(もっと読む)

半導体装置及びその製造方法

【課題】ヒューズ配線を溶断する際に素子分離構造や半導体基板に与えるダメージを抑制することができる半導体装置を提供する。

【解決手段】半導体装置1は、半導体基板10と、半導体基板の主面の面内方向に互いに離間するように形成された一対の電極12A,12Bと、これら電極12A,12Bを被覆し、上面に凹部13cを有する下層絶縁膜13と、凹部13cに形成されたヒューズ配線20Cと、下層絶縁膜13及びヒューズ配線20Cを被覆する層間絶縁膜21と、層間絶縁膜21上に形成され、ヒューズ配線20Cの直上にレーザトリミング用の開口部1hを有する上層絶縁膜31とを備える。

(もっと読む)

半導体装置

【課題】周辺部を損傷させずに、電流を供給することによって切断され得る電気ヒューズ構造を有する半導体装置を提供する。

【解決手段】電気ヒューズ10は、電子回路とその電子回路のスペアとしての冗長回路との間に電気的に接続され、それらの回路が樹脂封止された後に、外部から電流が供給されることによって切断され得るものである。電気ヒューズ10は、ファイン層中に設けられており、主配線1およびバリア膜3からなる。主配線1およびバリア膜3のそれぞれの線膨張係数は、その周辺に設けられている絶縁層2,4,および5のそれぞれの線膨張係数よりも大きい。また、主配線1およびバリア膜3のそれぞれの融点は、絶縁層2,4,および5のそれぞれの融点よりも低い。

(もっと読む)

半導体装置の製造方法

【課題】半導体装置の製造方法において、ヒューズ層を覆う絶縁膜の膜厚を精度良く調整する。

【解決手段】半導体基板10上の第2の層間絶縁膜17上にヒューズ層18Tが形成され、ヒューズ層18Tは第3の層間絶縁膜20で覆われる。第3の層間絶縁膜20上には、キャップメタル24に覆われたパッド電極23が形成され、それらは第1及び第2のパッシベーション膜25,26に覆われる。次に、ヒューズ層18T上で開口する第1のレジスト層27をマスクとして、ヒューズ層18T上で第2のパッシベーション膜26から第3の絶縁膜の厚さ方向の途中までをエッチングする。その後、パッド電極23上で開口する第2のレジスト層30をマスクとして、パッド電極23上で第1及び第2のパッシベーション膜25,26及びキャップメタル層24をエッチングしてパッド電極23の表面を露出する。その後、保護膜32を形成する。

(もっと読む)

半導体装置

【課題】本発明は、工程を増やすこと無く、ヒューズカット時間を短縮することができる半導体装置を提供する。

【解決手段】半導体装置は、ヒューズ配線(10)と、加熱用配線(21、22)とを具備し、ヒューズ配線(10)と加熱配線(21、22)とに電圧を印加してヒューズ配線の溶断部を切断する。ヒューズ配線(10)は、回路素子を形成する配線層と同じ層に形成され、電気的に切断されうる溶断部を備える。加熱用配線(21、22)は、回路素子を形成する配線層と同じ層のうちのヒューズ配線(10)より上層の配線層に絶縁層を介して溶断部を複数回横断するように形成され、溶断部の配線幅より広い配線幅を有して溶断部を加熱する。

(もっと読む)

半導体装置、その製造方法およびプログラミング方法

【課題】プログラミングの通電を必要最小限とすることができ、ヒューズヴィアの切断不良による論理回路の歩留りの低下も改善することができる半導体装置を提供する。

【解決手段】ヒューズヴィアの切断の要否が未定の部分にはヴィア切断型電気ヒューズ3が形成されており、切断の必要が確定している部分にはヒューズヴィアが省略されたヴィア切断型電気ヒューズ5が形成されている。

(もっと読む)

半導体装置及びその製造方法

【課題】トリミング素子からのトリミング時の気化ガスの圧力によりトリミング素子の下部の層間絶縁膜にクラックが入るのを防止する。

【解決手段】層間絶縁膜2上にトリミング素子Tを形成する。トリミング素子Tの上を層間絶縁膜3aで被覆する。トリミング素子Tの斜め上方領域の層間絶縁膜3a上にクラック誘導体Gを形成する。トリミング素子T及びクラック誘導体Gはレーザー光の照射領域に配置される。レーザー光を照射すると、トリミング素子Tの周辺及びクラック誘導体Gの周辺の層間絶縁膜3a等に重畳して広く延在する高温領域6が形成され、該高温化した層間絶縁膜3a等の剛性が低下する。その結果、トリミング素子Tの上辺のコーナー部に気化ガスの圧力がかかりやすくなり、トリミング素子Tの下辺のコーナー部にかかる気化ガスの圧力が小さくなるので、トリミング素子Tの下側の層間絶縁膜2のクラック5発生を防止できる。

(もっと読む)

1 - 20 / 195

[ Back to top ]