Fターム[5F064FF52]の内容

ICの設計・製造(配線設計等) (42,086) | 切り換え、選択 (3,709) | 切り換え、選択実行方法 (1,017) | ソフトウェア(プログラム)によるもの (171)

Fターム[5F064FF52]に分類される特許

1 - 20 / 171

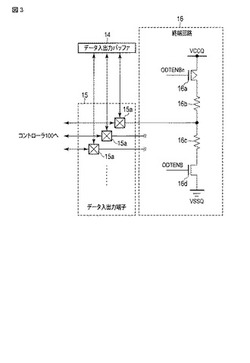

半導体装置

【課題】高品質な半導体装置を提供する。

【解決手段】第1の絶縁膜111、第1の電極112、第2の絶縁膜113、及び第2の電極114を含むゲート構造を有するメモリセルMCが複数設けられた記憶部11と、少なくとも外部100からのデータを受信し、記憶部にデータを供給する端子15と、第1の絶縁膜、第1及び第2の電極とを含むゲート構造を有し、電流経路の一端に第1の電圧が印加される第1導電型の第1のトランジスタ16a、一端が第1のトランジスタの電流経路の他端に接続され、他端が端子に接続される第1の抵抗素子16b、一端が端子及び第1の抵抗素子の他端に接続される第2の抵抗素子16c及び、ゲート構造を有し、電流経路の一端が第2の抵抗素子の他端に接続され、電流経路の他端に第2の電圧が印加される第2導電型の第2のトランジスタ16dを含む第1の回路16と、を備える。

(もっと読む)

再構成可能な集積回路ユニットを備えた論理回路及びその論路回路のエラー修正方法

【課題】エラー箇所の特定を実施する際に、システムを停止しないでエラー発生前の高信頼性までシステム性能を復帰させる。

【解決手段】同一動作を行う複数個の再構成可能な集積回路ユニットを備え、複数の該集積回路ユニットのそれぞれに複数のバンクを有する論理回路において、入力されたデータを、複数個の前記集積回路ユニットの各バンクに振り分けて入力する入力データ制御部と、複数個の集積回路ユニットの各バンクから出力されるデータを比較して、データ間の不一致を検出するエラー解析部と、エラー解析部から、データ間の不一致の通知を受けた場合に、複数個の集積回路ユニットの該当するバンクの再構成を行う構成情報制御部と、を備える。

(もっと読む)

半導体集積回路装置

【課題】電源遮断領域の信号配線の自由度を低下させないで、電源遮断用スイッチから電源遮断領域に至る電圧伝達経路における電圧降下を抑える。

【解決手段】半導体集積回路装置(80)は、電源遮断用スイッチ(90)と電源遮断領域(763)とが形成された半導体チップ(22)とを含む。半導体チップは基板(21)に結合される。上記電源遮断領域の外側に上記電源遮断用スイッチを配置することで、電源遮断領域内の配線チャネル数の低減を回避する。そして上記基板には、上記半導体チップ内から上記電源遮断用スイッチを介して上記半導体チップの外に伝達された電源電圧を再び上記半導体チップ内に伝達して上記電源遮断領域へ給電するための基板側給電路(30)を形成することで、上記電源遮断用スイッチと上記電源遮断領域との間の電圧降下を抑える。

(もっと読む)

電子回路網の信頼性を向上させるための装置および関連する方法

【課題】電子回路網の信頼性を向上させるための装置および関連する方法を提供すること。

【解決手段】上記装置は、装置の第1の構成に使用される第1のセットの回路要素と、装置の第2の構成に使用される第2のセットの回路要素とを含み、装置の第1の構成は、装置の信頼性を向上させるために、装置の第2の構成に切り替えられる。上記方法は、第1の構成に割り当てられた第1のセットの回路要素を使用することによって、第1の構成で集積回路(IC)を動作させることと、第2の構成に割り当てられた第2のセットの回路要素を使用することによって、第2の構成でICを動作させることとを含み、第1の構成でICを動作させた後に第2の構成でICを動作させるのは、ICの信頼性を向上させる。

(もっと読む)

半導体装置

【課題】FETの駆動力性能や遮断性能などを向上できる半導体装置を提供する。

【解決手段】半導体装置は、半導体基板と、前記半導体基板上に形成され、オフ状態とオン状態とで閾値電圧を可変させるFETからなる半導体素子と、を備える。前記半導体素子は、前記半導体基板のチャネル形成箇所の上方に形成される絶縁膜と、前記絶縁膜の上方に配置されるゲート電極と、前記絶縁膜と前記ゲート電極との間に介挿され、前記チャネルとの間よりも、前記ゲート電極との間で、より多くの電子の授受を行なうチャージトラップ膜と、を有する。

(もっと読む)

半導体装置および半導体装置の駆動方法

【課題】消費電力を抑えることができる、プログラムユニットを用いた半導体装置を提供する。また、信頼性の高い、プログラムユニットを用いた半導体装置を提供する。さらに集積度の高い、プログラムユニットを用いた半導体装置を提供する。

【解決手段】PLD等のロジックセル間の接続構造を変更する機能を有する半導体回路において、ロジックセル間を接続や切断、あるいはロジックセルへの電源の供給を、オフ電流またはリーク電流が小さい絶縁ゲート電界効果型トランジスタを用いたプログラムユニットによって制御する。プログラムユニットにはトランスファーゲート回路を設けてもよい。駆動電圧を下げるため、プログラムユニットには容量素子を設けて、その電位をコンフィギュレーション時と動作期間とで異なるものとしてもよい。

(もっと読む)

プログラマブルロジックデバイス

【課題】電源電位の供給が遮断されたときでもコンフィギュレーションデータの保持が可能で、電源投入後のプログラマブルスイッチの起動時間が短い、低消費電力化が可能なプログラマブルロジックデバイスを提供すること。

【解決手段】各論理ブロック間の配線接続を制御するプログラマブルスイッチのメモリ部のトランジスタに、トランジスタのオフ電流を十分に小さくすることができる材料、例えば、ワイドバンドギャップ半導体である酸化物半導体材料を用いて当該トランジスタを構成する。トランジスタのオフ電流を十分に小さくすることができる半導体材料を用いることで、電源電位の供給が遮断されたときでもコンフィギュレーションデータを保持することが可能となる。

(もっと読む)

半導体集積回路装置

【課題】容易にカスタマイズ対応可能な半導体集積回路装置を提供する。

【解決手段】アレイ型プロセッサ部(300)は、プロセッサエレメント(330)とプログラマブルスイッチ(320)とを備えるプロセッサユニット(310)をマトリクス状に配置する。プロセッサエレメント(330)は、複数ビット幅の第1演算器(332)と複数ビット幅より狭い所定のビット幅の第2演算器(333)とを有する。第1演算器(332)および第2演算器(333)の接続構成は構成情報メモリ(340)に設定される構成情報に基づいて変更可能である。プログラマブルスイッチ(320)は、配線からプロセッサエレメントに複数ビット幅のデータおよび所定のビット幅のデータを構成情報に基づいて入出力する。制御回路(200)は、内部バス(180)に接続され、アレイ型プロセッサ部(300)の動作を制御し、内部バス(180)を介してデータを授受する。

(もっと読む)

プログラマブルLSI

【課題】低消費電力で、動的コンフィギュレーションにも対応可能なプログラマブルLSIを提供する。

【解決手段】複数のロジックエレメントを有し、複数のロジックエレメントそれぞれは、コンフィギュレーションメモリを有する。複数のロジックエレメントそれぞれは、コンフィギュレーションメモリに記憶されたコンフィギュレーションデータに応じて、異なる演算処理を行い、且つ、ロジックエレメント間の電気的接続を変更する。コンフィギュレーションメモリは、揮発性の記憶回路と、不揮発性の記憶回路との組を有し、不揮発性の記憶回路は、チャネルが酸化物半導体層に形成されるトランジスタと、当該トランジスタがオフ状態となることによってフローティングとなるノードに一対の電極のうちの一方が電気的に接続された容量素子と、を有する。

(もっと読む)

半導体装置

【課題】ドライバの故障による出力異常を救済することが可能な故障検出救済回路を含んだ半導体装置を提供すること。

【解決手段】故障検知部1は、ドライバ10の出力の期待電位の逆電位となるようにドライバ10の出力にプルアップ抵抗15またはプルダウン抵抗18を接続し、ドライバ10の入力電位と出力電位とを比較することによりドライバ10の故障を検出する。故障救済部2は、故障検知部1によってドライバ10の故障が検出された場合に、期待電位と同電位となるようにドライバ10の出力にプルアップ抵抗26またはプルダウン抵抗29を接続してドライバ10の故障を救済する。したがって、ドライバ10の故障による出力異常を救済することが可能となる。

(もっと読む)

FPGA設計支援システムおよびFPGA設計支援方法ならびにFPGA設計支援プログラム

【課題】FPGAの設計段階で、ユーザ回路にTMRを適用したときのSERを見積もることができるFPGA設計支援システムを提供する。

【解決手段】TMRを適用した場合のSER低減率を含む情報を保持するTMR効果情報DB17と、FPGAが有するCRAM全体のSERを計算するCRAM_SER計算部12と、各回路ブロックのFPGAリソースの使用率を計算するFPGAリソース使用率計算部13と、CRAM全体のSERおよび各回路ブロックのFPGAリソースの使用率に基づいて、回路ブロック単位のSERを計算する回路ブロックSER計算部11と、TMRブロックについてSERおよびTMRを適用した場合のSERの低減率に基づいてTMRブロックのSERを計算するTMRブロックSER計算部14と、各回路ブロックのSERおよび各TMRブロックのSERに基づいてユーザ回路全体のSERを計算するSER計算部10とを有する。

(もっと読む)

可変遅延回路およびその制御方法

【課題】信号の遅延量を微調整可能な可変遅延回路を提供する。

【解決手段】可変遅延回路において、N個の可変論理回路を用いてN段のセレクタが直列接続される。1段目のセレクタSL1の2つの入力端子に信号が入力される際、入力信号が通過する2つの信号経路D1には経路差d1が存在している。また、2段目のセレクタSL2の2つの入力端子に信号が入力される際、入力信号が通過する2つの信号経路D2には、経路差d2が存在している。信号が通過する当該経路の組み合わせは、セレクタSLの段数に基づき、N段であるため2nとおりの信号経路の組み合わせが生じる。すなわち、2nとおりの切替信号R1〜Rnの組み合わせに基づいて2nとおりの信号経路が選択される。2nとおりの信号経路の組み合わせに基づく配線経路差に基づいて信号遅延量を調節する。

(もっと読む)

半導体集積回路

【課題】 消費電力を削減した半導体集積回路を提供すること。

【解決手段】 本発明の実施形態による半導体集積回路は、第1の電源と第2の電源との間に2つの不揮発メモリと複数のスイッチング素子が接続されたメモリセルを複数含む半導体集積回路であって、少なくとも2つの前記メモリセルの出力配線が接続され、出力配線が接続されたメモリセルに含まれるスイッチング素子の制御ゲートに入力信号もしくはこの入力信号の反転信号が入力されて、出力配線が接続されたメモリセルの少なくとも1つのメモリセルに含まれる前記入力信号もしくはこの入力信号の反転信号が入力されたスイッチング素子が非導通となり、少なくとも1つのメモリセルに含まれる前記入力信号もしくはこの入力信号の反転信号が入力されたスイッチング素子が導通する。

(もっと読む)

再構成デバイス、処理配置方法及びプログラム

【課題】再構成デバイスの回路構成変更において、機構追加による回路規模を増やすことなく、処理内容に対する依存を回避しつつ回路構成変更期間を短縮する。

【解決手段】外部メモリ101は、内部に回路構成情報106を保持している。回路構成情報106は再構成デバイス105を構成する要素を動作させる設定群である。コンフィギュレーションコントローラ102は上記メモリ101から結線104を通じ回路構成情報106を取得する。取得した回路構成情報106は結線103を通じて再構成デバイス105へ送られる。

(もっと読む)

半導体集積回路及び電源電圧適応制御システム

【課題】フリップフロップを備える半導体集積回路において、エラーフリップフロップを効率的に検出する。

【解決手段】半導体集積回路は、冗長フリップフロップを含む複数のフリップフロップと、セレクタ部と、エラー検出部とを備える。セレクタ部は、再構成情報に応じて選択フリップフロップを選択し、入力端子に入力されたデータが選択フリップフロップのそれぞれによって出力端子に出力されるようにデータの流れを切り替える。テストモード時、フリップフロップはスキャンチェーンを構成し、そのスキャンチェーンにはスキャンデータが入力される。そして、エラー検出部は、それぞれのフリップフロップの入出力に基づいてエラーフリップフロップを検出し、当該エラーフリップフロップが選択フリップフロップから除外されるように再構成情報を作成する。

(もっと読む)

半導体装置

【課題】複数の電圧レベルの電源電圧が供給される入出力バッファ回路に対して、従来よりも少ない電源配線スペースで十分な電源供給を可能にする。

【解決手段】半導体装置3において、入出力バッファ回路BFは電圧レベルの変換を行なう。第1の電源配線HVLは、入出力バッファ回路BFの第1の回路部分HCと接続され、第1の回路部分HCに第1の電源電圧VCC1を供給する。第2の電源配線LVLは、入出力バッファ回路BFの第2の回路部分LCと接続され、第2の回路部分LCに第2の電源電圧VCC2を供給する。複数のスイッチ部SWは、第3の電源配線SVLに沿った複数箇所にそれぞれ設けられる。複数のスイッチ部SWの各々は、内部回路10から出力された制御信号に応じて、第1および第2の電源配線HVL,LVLのうち選択された一方の電源配線と第3の電源配線SVLとを接続する。

(もっと読む)

リコンフィギュラブルロジック装置

【課題】セット全体のコストダウンや小型化、ないしは、起動時間の短縮を実現することが可能なリコンフィギュラブルロジック装置を提供する。

【解決手段】リコンフィギュラブルロジック装置において、ルックアップテーブル11は、コンフィギュレーションデータを不揮発的に記憶する手段として、強誘電体素子のヒステリシス特性を利用した不揮発性フリップフロップFFを有する。コンフィギュレーションデータは、ルックアップテーブル11に任意の入出力論理値表を実装するための設定データであり、プログラミングによって設定される。

(もっと読む)

半導体チップ、半導体装置及びLSI設計装置

【課題】チップコストの低下とチップ歩留りの向上とを同時に実現する。

【解決手段】実施形態に係わる半導体チップは、パッド領域11及び方形でないゲート領域12を備える第1のレイアウトL1と、第1のレイアウトL1を180°回転させた第2のレイアウトL2とを備える。第1及び第2のレイアウトL1,L2は、点対称かつ重なり合わずに結合されることによりチップレイアウトを構成する。チップレイアウトは、方形のチップ領域内に配置され、第1及び第2のレイアウトL1,L2は、それぞれ独立に動作するLSIを構成する。

(もっと読む)

プログラマブルゲートアレイおよびプログラマブルゲートアレイのプログラミング方法

【課題】配置配線をやり直す可能性を低減することができるプログラマブルゲートアレイおよびプログラマブルゲートアレイのプログラミング方法を提供する。

【解決手段】論理素子11を電源電位を供給するVCC12と接地電位を供給するGND13とに接続させる接続素子14を備え、論理素子11と接続素子14との間に、論理素子11と接続素子14とを接続可能な配線領域15が設けられ、配線領域15と接続素子14とを接続する専用ライン16が設けられていることを特徴とする。

(もっと読む)

抵抗値補償方法、抵抗値補償機能を有する回路、回路の抵抗値試験方法、抵抗値補償プログラム、回路の抵抗値試験プログラム及びシステム

【課題】簡易で精度の高いODT回路の抵抗補償方式を提供することを目的とする。

【解決手段】複数のトランジスタの組み合わせによって所望の抵抗値と同等の抵抗値を実現するODT回路200であって、組み合わせるべきトランジスタを順次選択することにより、選択されたトランジスタによって実現される抵抗値を順次変化させる構成である。

(もっと読む)

1 - 20 / 171

[ Back to top ]