Fターム[5F064HH08]の内容

ICの設計・製造(配線設計等) (42,086) | 設計、製造における計算機技術 (6,629) | ソフトウェア(プログラム)関係 (5,214) | 使用言語 (170)

Fターム[5F064HH08]に分類される特許

161 - 170 / 170

生成装置、生成方法、その生成方法をコンピュータに実行させることが可能なプログラム、及びそのプログラムを記録した記録媒体

【課題】 プログラム言語が異なる複数の半導体試験装置のそれぞれで用いるテストプログラム及びテストパタンプログラムのいずれか又は両者を生成するための生成方法等であって、人為的な手法ではなく、処理工程がシンプルで無駄を取り除いた生成方法等を提供する。

【解決手段】 プログラム言語が異なる複数の半導体試験装置のそれぞれで用いるテストプログラム及びテストパタンプログラムを生成する生成装置51は、各半導体試験装置のプログラム言語に応じたテストプログラム77及びテストパタンプログラム79を生成するプログラム生成エンジン61と、生成されたテストプログラム77及びテストパタンプログラム79を、複数の半導体試験装置におけるプログラム言語とは異なるプログラム言語による共通フォーマットの中間データに変換する逆変換エンジン69とを備える。

(もっと読む)

半導体集積回路の設計方法、設計装置及び論理設計プログラム

【課題】レイアウト設計後の出戻りの発生を好適に抑制することのできる半導体集積回路の設計方法を提供する。

【解決手段】論理設計工程(ステップ110〜130)と物理設計工程(ステップ200)とを含むLSIの設計方法において、論理設計工程(ステップ110〜130)で作成したデータ(F1)が物理設計工程(ステップ200)での使用に妥当なデータであるかどうかを同物理設計工程(ステップ200)の開始に先立って見積もり(ステップ140)、該見積もり結果を論理設計工程(ステップ110〜130)にフィードバックして同論理設計工程(ステップ110〜130)で作成するデータ(F1)に反映させるようにした。

(もっと読む)

特定用途集積回路において自動伝送線路選択を行う方法、プログラム製品、および設計ツール

【課題】用途特定集積回路における自動伝送線路選択の方法、プログラム製品、および設計ツールを提供すること。

【解決手段】本方法は、用途特定集積回路のブロック間の配線経路を決定すること、伝送線路置換候補を得るために配線経路を細かく調べること、および、伝送線路置換候補ごとに、配線経路を実現すべきバッファ付き線か伝送線路を自動的に選択することを含む。

(もっと読む)

タイミングモデル、及びそれを用いたLSI設計方法

【課題】 理想クロック条件と伝搬クロック条件との2種類のモードを有するタイミングモデルを用いて、効率良く、機能ブロックを含んだLSIの設計を行う方法を提供する。

【解決手段】 複数のフリップフロップを含む機能ブロックを用いたLSI設計方法であって、第1モードと第2モードで使用可能なタイミングモデルを準備するステップと、機能ブロックを1又は複数含む機能要素の機能設計を行うステップと、機能設計で定められた機能要素に対し、機能ブロックのタイミングモデルを第1モードで用いて論理合成するステップと、論理合成された機能要素に対し、タイミングモデルを第1モードで用いて第1タイミング解析を行うステップと、論理合成と第1タイミング解析の結果に基づきレイアウトを行うステップと、レイアウト後にタイミングモデルを第2モードで用いて第2タイミング解析を行うステップと、を含むことを特徴とするLSI設計方法。

(もっと読む)

回路装置およびプログラム処理方法

【課題】 機能の変更が可能なリコンフィギュラブル回路を有する回路装置を提供する。

【解決手段】 本発明の集積回路装置は、マッピング用のプログラムに含まれる条件文中にelse文が存在しない場合であっても、代入処理を適切に実行する。具体的には、プログラムのコンパイル時に、条件文の実行に先立って実行される代入処理を探索し(S18のY)、探索した代入処理をelse条件成立時の代入処理として設定する。なお、探索により代入処理がみつからない場合は(S18のN)、記憶部に記憶された最新の変数値をelse条件成立時の代入値として決定する(S22)。

(もっと読む)

論理回路のシンボル表示装置

【課題】論理回路を読み込み、コンポーネントとシンボルを多対多の場合でも論理回路図面を表現可能にした表示装置を提供すること。

【解決手段】、本発明では、論理回路読み込み部2と、コンポーネントライブラリを参照してコンポーネントとコンポーネントポートを作成するコンポーネント/コンポーネントポート作成部4と、インスタンスに対し、コンポーネント/コンポーネントポートを参照してインスタンス/インスタンスポートを作成するインスタンス/インスタンスポート作成部5と、シンボルライブラリを参照してシンボルとシンボルポートを作成するシンボル/シンボルポート作成部6と、インスタンス毎にどのシンボルを用いて表示するのかを対応付けするインスタンス/インスタンスポートとシンボル/シンボルポート対応手段と、回路図表示手段と、コンポーネントライブラリと、シンボルライブラリを具備する。

(もっと読む)

集積回路製作におけるデルタ情報設計クロージャ

集積回路(「IC」)製作におけるタイミングドリブンの形状クロージャのためのシステム及び方法が提供される。これらの統合設計製造工程(「IDMP」)は、IC製作のタイミング及びジオメトリ検証工程の情報をIC設計に統合するデルタフローを含む。デルタフローは、回路特徴パラメータに関する差分情報を処理するためのデルタ−ジオメトリタイミング予測工程及び/又はデルタ−タイミング形状予測工程を含むインクリメンタルフローである。デルタフローは、回路特徴パラメータに対応する差分又はデルタ情報を用いてIC設計を独自に再特徴付けする。デルタフローは、新しい回路特徴パラメータを生成する必要がなく、更にIC設計の全ての情報を再処理することを必要とせずに、デバイス及び相互接続構造部の対応するパラメータを強調又は再特徴付けするデルタ出力(インクリメンタルの)を提供する。 (もっと読む)

製造を容易にする設計

【課題】製造容易性を改善するために、既存の超小型装置設計を変更する技術を提供する。

【解決手段】これらの技術により、設計者は、設計に於けるデータに関連した製造基準を受領する。次に、関連した設計データが識別されて、超小型装置設計者へ供給され、該設計者は、製造基準に基づいて設計変更を選択することが出来る。このようにして、設計者は、超小型装置の元の設計に於いて、半導体ファンドリからの製造基準を直接的に包含させることが出来る。

(もっと読む)

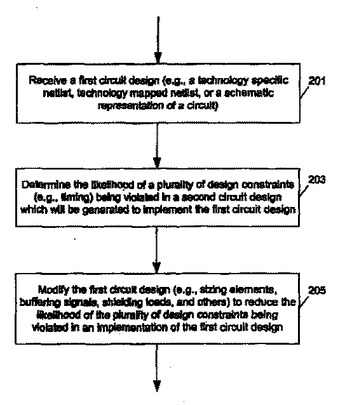

自動回路設計のための方法と装置

回路の後の実装で生じうる逸脱に応じて回路設計を自動的に修正する方法と装置。一態様では、回路を設計する方法は、回路の設計の後の配線実装時に設計制約条件に違反する可能性があるかどうかを判定することと、後の実装で設計制約条件に違反する可能性を低減するように回路設計を修正することを含む。例えば、2よりも大きい多数のファンアウトを持ち、タイミング・クリティカル・パスまたはクリティカルに近いパス上のネットに対する経路は、経路トポロジに敏感であると考えられ、代替配線経路であると、タイミング制約に違反する可能性があり、その後の配線ソリューションのタイミング問題が発生する可能性を低減するために、コスト関数を悪化させない範囲で、回路設計に変換を選択的に適用するとよい。  (もっと読む)

(もっと読む)

LSI回路のリグレッションテストシステム、及びそれに用いる装置とそのリグレッションテスト方法

【課題】検証中のLSI回路の設計変更があるごとにリグレッションテストの必要性を判断し、必要なら実行可能とする。

【解決手段】データ管理装置1で、入力設計データ11、テストベンチ12を登録済みデータとの差分チェックを行いながらデータベース13に登録し、検証内容に応じたデータをシミュレーション装置2へ送る。差分チェックにおいて入力設計データに差分があると、シミュレーション装置で実行中(予約中)のリグレッションテストがあるか問合せ、ある場合は、利用者の確認を得てから中止させる。ない場合及び中止後は、利用者の確認を得てから最新の設計データに関連するテストベンチをデータベースより読み出し最新の設計データと組にしてシミュレーション装置へ送出する。

(もっと読む)

161 - 170 / 170

[ Back to top ]