Fターム[5F064HH08]の内容

ICの設計・製造(配線設計等) (42,086) | 設計、製造における計算機技術 (6,629) | ソフトウェア(プログラム)関係 (5,214) | 使用言語 (170)

Fターム[5F064HH08]に分類される特許

21 - 40 / 170

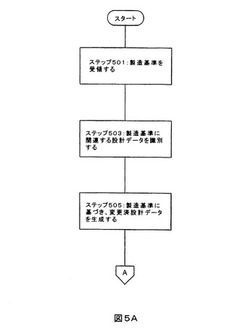

製造を容易にする設計

【課題】製造容易性を改善するために、既存の超小型装置設計を変更する技術を提供する。

【解決手段】これらの技術により、設計者は、設計に於けるデータに関連した製造基準を受領する。次に、関連した設計データが識別されて、超小型装置設計者へ供給され、該設計者は、製造基準に基づいて設計変更を選択することが出来る。このようにして、設計者は、超小型装置の元の設計に於いて、半導体ファンドリからの製造基準を直接的に包含させることが出来る。

(もっと読む)

半導体回路の設計装置および設計方法

【課題】配線のしやすさを損なうことなく、ビアの不良による歩留まりの低下を抑制可能な半導体回路の設計装置および設計方法を提供する。

【解決手段】半導体回路の設計方法は、論理回路を構成するセルの配置およびセル間の配線を行い、複数箇所にビアが設けられる配線を含むレイアウトパターンを生成するステップ(ステップS1、S2)と、ビアから、配線上の信号を受信するレシーバセルまでの負荷容量をビア毎に算出するステップ(ステップS4)と、ビアごとの、負荷容量に基づいて、負荷容量が大きいビアを優先的に低抵抗のビアに置換するステップ(ステップS6、S7)を備える。

(もっと読む)

フロアプランデータ生成装置及び方法

【課題】チップの設計期間を短縮する。

【解決手段】CPU1は、設計対象の回路を構成するセルのうち、所定のサイズより大きいセルサイズを有するセルのみの回路情報をゲートレベルで記述した簡易ネットリスト43と、所定のサイズより大きいセルサイズを有するセルのみの仕様データを含むセルリスト44とを用いてフロアプランを行い、仮フロアプランデータ47を生成する。CPU1は、ユーザによって回路全体のフロアプランが行われるときに、回路を構成するセルの仕様データである全体ライブラリ42と、回路を構成するセルの回路情報をゲートレベルで記述した全体ネットリスト45と、仮フロアプランデータ47と、簡易ネットリスト43を全体ネットリスト45に整合させるためのセルリスト44とを出力する。

(もっと読む)

多電源集積回路設計装置およびその方法、ならびに、多電源集積回路製造方法

【課題】異電源ドメイン間におけるタイミング収束性が改善された回路設計を容易に行うことができる多電源集積回路設計装置の提供。

【解決手段】回路構成情報および電源構成情報に基づいて、異電源ドメインと接続するデータパスに対し、最初および最後に接続される同期式フリップフロップである境界FFの少なくともいずれかを抽出して、境界FFデータとして出力する境界FF抽出部と、回路構成情報および境界FFデータに基づいて、境界FFに接続されたクロックラインに配されたバッファを抽出し、入力を分岐させて当該分岐を入力とする新たなバッファを追加するバッファ追加部と、境界FFが新たなバッファに接続されるようにクロックラインを繋ぎ換えるように、回路構成情報を変更して、変更された回路構成情報のデータを出力するクロックライン再構成部と、を有する多電源集積回路設計装置。

(もっと読む)

設計装置

【課題】消費電力を低減し、誤動作を防止することができるフリップフロップ回路を設計するための設計装置を提供することを課題とする。

【解決手段】第1の入力信号、第1のイネーブル信号及び第1のクロック信号を入力する第1のフリップフロップ回路の第1の設計データに対して、第1のクロック信号の周波数の2倍以上の周波数のクロック信号で第1の静的タイミング解析を行う第1の静的タイミング解析部(S11)と、第1の静的タイミング解析の結果が合格の場合には、第1の設計データを入力し、第1のフリップフロップ回路を第2のフリップフロップ回路に変換した第2の設計データを生成する第1の変換部(S13)とを有し、第1のフリップフロップ回路はクロックゲーティング回路を有さず、第2のフリップフロップ回路はクロックゲーティング回路を有する設計装置が提供される。

(もっと読む)

半導体集積回路の設計方法及びプログラム

【課題】タイミング制約を満たすためにセルの物理的な位置やRTL(Register Transfer Level)を変更する必要がなく、回路の最適化を短時間に行うことができ、半導体集積回路の設計期間を短縮することができる半導体集積回路の設計方法、設計プログラムを提供する。

【解決手段】半導体集積回路のネットリストに対して静的タイミング解析を行うことにより、所定のタイミング制約を満たさないタイミングエラーパスを検出し、前記タイミングエラーパスを含む第1の論理ブロックと、フリップフロップを介して前記第1の論理ブロックに接続され、所定のタイミング制約を満たす第2の論理ブロックとを抽出し、前記第1の論理ブロックと前記第2の論理ブロックとの間のフリップフロップが正相/逆相フリップフロップである場合は、当該正相/逆相フリップフロップを逆相/正相フリップフロップに変更する。

(もっと読む)

半導体集積回路の回路設計方法、設計装置及び回路設計プログラム

【課題】ピーク電流を抑えつつ、クロックツリーの生成のやり直しを減らし、設計TATを短縮すること。

【解決手段】本発明の第1の態様にかかる半導体集積回路の回路設計方法は、一のクロックルートからクロックが分配される複数の順序回路の配置情報に基づき、当該複数の順序回路のそれぞれのクロック分配遅延時間を算出し、算出されたクロック分配遅延時間に応じて、複数の順序回路を、予め遅延時間の範囲を定義した複数のグループに組み分けし、グループごとに設定された基準遅延時間となるように、グループごとに当該グループに組み分けされた順序回路に対するクロックのクロックツリーを生成する。

(もっと読む)

集積回路の設計のためのデバイスミスマッチのモデリングおよびシミュレーティング

【課題】ユーザは、回路スケマティック中のデバイスに対するレイアウトスタイルであって、デバイス配置およびデバイス相関の特徴を捉えるレイアウトスタイルを特定する。

【解決手段】結果として得られるレイアウトは、コンピュータを用いることでシミュレーションされ得て、1つ以上のパフォーマンス指標がその回路に対して評価され得る。場合によっては、テストチップが、異なるレイアウトスタイルに対応する配置に対するデバイス相関を画定するために用いられても良い。

(もっと読む)

集積回路設計方法及びプログラム

【課題】ある演算記述における単一の演算期間が、指定した期間よりも長い場合があっても、動作記述中の演算記述の変更を不要とする集積回路設計方法及びプログラムを提供する。

【解決手段】本集積回路設計方法は、演算子を細分化した演算記述を作成する第1工程と、第1工程で作成した細分化演算記述を使用して演算子のオーバロード用ライブラリを作成する第2工程と、動作記述を使用してオーバロード用ライブラリインクルード済み動作記述を作成する第3工程と、第3工程で作成したオーバロード用ライブラリインクルード済み動作記述と第2工程で作成したオーバロード用ライブラリとを使用して高位合成を行いレジスタ転送レベル記述を作成する第4工程と、第4工程で作成したレジスタ転送レベル記述を使用して論理合成を行いゲートレベル記述を作成する第5工程とを備える。

(もっと読む)

電子回路の階層的次数ランキングされたシミュレーション

【課題】集積回路設計をシミュレートする方法を提供する。

【解決手段】本発明の方法では、ネットリストにおけるノードのノード次数ランキングを決定することができる。ネットリストの回路は、ノード次数ランキングに基づいて静的及び動的電流駆動方式でパーティショニングされることができる。ノード次数パーティショニングに基づいて階層データ構造が構築されることができる。一実施形態では、シミュレーション最適化のために中間ノード次数を動的に結合することができる。その後、回路を1若しくは複数の結合された中間ノード次数に基づいて再パーティショニングすることができる。階層データ構造を用いて求解及び積分を行い、次数ランキングされた階層エンジンを生成することができる。次数ランキングされた階層エンジンについての解析を行うことができる。この時点で、解析に基づいてIC設計のシミュレーションデータがエクスポートされることができる。

(もっと読む)

レイアウト検証方法及びレイアウト検証装置

【課題】レイアウトデータのシールドについて精度良く検証する検証装置を提供すること。

【解決手段】検証装置は、レイアウトデータ30の被シールド配線パターンに対して検索領域を設定する。検証装置は、検証領域において、被シールド配線パターン、シールド配線パターン及びその他配線パターンを除く領域に複数の矩形領域を設定する。検証装置は、複数の矩形領域のうち被シールド配線パターンに接触する矩形領域を基にして、矩形領域を合成して合成領域を生成する。検証装置は、合成領域と接触するシールド配線パターン及びその他の配線パターンの情報に基づいて、抽出結果データDeを生成する。検証装置は、生成した抽出結果データDe及び制御カード21に基づいて、レイアウトデータ30のシールドが正常に行われているかを判定する。

(もっと読む)

等価性検証プログラム、等価性検証プログラムを記録したコンピュータ読み取り可能な記録媒体、等価性検証装置、および等価性検証方法

【課題】アナログ回路とその特性モデルとの等価性を効果的かつ容易に検証することができる等価性検証プログラム、等価性検証プログラムを記録したコンピュータ読み取り可能な記録媒体、等価性検証装置、および等価性検証方法を提供する。

【解決手段】アナログ回路およびその特性モデルについてそれぞれ自動的に検証環境を構築し(ステップS120)、構築した検証環境に基づきGUIを用いてテストシナリオを作成する(ステップS130)。次いで、作成したテストシナリオからシミュレーションを行い(ステップS140)、得られたシミュレーションログから等価性を判断するための情報を表として記載したテキストデータに変換し(ステップS150)、比較する(ステップS160)。

(もっと読む)

検証評価システム

【課題】半導体集積回路装置上で発生する誤動作状態を効率的に再現し、その誤動作状態による影響の効率的な解析を実現する。

【解決手段】FPGA1100の開発は、HDLベースで行われることに着目し、誤動作状態の検証を行う為の誤動作挿入論理を自動的に付与し、FPGA1100上での動作が可能となる仕組みを構成する。また、検証の総数を、FPGA1100と誤動作挿入論理を動的に制御する言語と制御機能によって削減する。

(もっと読む)

XOR及びXNORロジックの回路及びレイアウト

XOR回路は、第2の入力ノードによって制御されるパスゲートを備える。そのパスゲートは、制御されたとき、第1の入力ノードに存在するロジック状態のバージョンを出力ノードに通すように接続されている。伝送ゲートが、第1の入力ノードによって制御される。その伝送ゲートは、制御されたときに、第2の入力ノードに存在するロジック状態のバージョンを出力ノードに通すように接続されている。プルアップロジックが、第1及び第2の入力ノードの両方によって制御される。そのプルアップロジックは、第1及び第2の入力ノードの両方がハイのときに、出力ノードをロウに駆動するように接続されている。XNOR回路は、プルアップロジックが、第1及び第2の入力ノードの両方がハイときに出力ノードをハイに駆動するように接続されたプルダウンロジックに置換されることを除いて、XOR回路と同様に画定される。  (もっと読む)

(もっと読む)

ネットワーク接続のスイッチングを用いるエミュレータ

【課題】直列化及び非直列化回路が、クロスポイントスイッチにより経路付けするためにプログラマブルロジックデバイスの入力及び出力信号をグループ化するようにエミュレータ回路基板に提供される。

【解決手段】一例においては、プログラマブルロジックデバイスの入力及び出力信号は仮想相互接続のタイムマルチプレクスされた信号である。静的又は動的にスケジュールされた動作のためにクロスポイントスイッチを構成することが可能である。

(もっと読む)

ウェハ貫通ビア構造を有するESDネットワーク回路及び製造方法。

【課題】ウェハ貫通ビア構造を有するESDネットワーク回路及びその製造方法を提供する。

【解決手段】本発明は一般に回路構造及び回路の製造方法に関し、より具体的には、ウェハ貫通ビアを有する静電放電(ESD)回路及びその製造方法に関する。ESD構造体は、ESD能動デバイスと、ESD能動デバイスから基板への低直列抵抗経路をもたらす少なくとも1つのウェハ貫通ビアとを備える。装置は、入力部と、少なくとも1つの電力レールと、入力部と少なくとも1つの電力レールとの間に電気的に接続されたESD回路とを含み、ここでESD回路は少なくとも1つのウェハ貫通ビアを備えて基板への低直列抵抗経路をもたらす。方法は、ESDデバイスを基板上に形成することと、基板の裏面に接地面を形成することと、ESD能動デバイスの負電源及び接地面に電気的に接続されて基板への低直列抵抗経路をもたらす少なくとも1つのウェハ貫通ビアを形成することとを含む。

(もっと読む)

配線経路作成支援方法、配線経路作成支援プログラム、及び配線経路作成支援装置

【課題】集積回路パッケージにおける配線経路の作成を適切に支援する。

【解決手段】集積回路パッケージの少なくとも各ピン、各水平ピン間、各垂直ピン間、及び各対角ピン間を配線のボトルネック箇所とし、各ボトルネック箇所に配線容量を付与する手順と、ボトルネック箇所ごとに入り口ノード及び出口ノードの二つのノードを生成する手順と、それぞれのボトルネック箇所について、ボトルネック箇所内の入り口ノードから出口ノードへの有向枝を生成し、隣接するボトルネック箇所間において一方の出口ノードから他方の入り口ノードへの有向枝を相互に生成し、対角ピン間のボトルネック箇所と当該対角ピン間の全ての斜め隣のボトルネック箇所との間において一方の出口ノードから他方の入り口ノードへの有向枝を相互に生成し、生成された全ての有向枝に、ボトルネック箇所に割り当てられた配線容量の最小値を枝容量として付与する手順とを有する。

(もっと読む)

半導体構造、半導体構造の形成方法、半導体装置の動作方法(高周波の高調波を減少するためのSOIRFスイッチ)

【課題】SOI基板における容量結合を減少した集積回路を提供する。

【解決手段】底部半導体層と同じ導電型のドーパントを含む第1のドープされた半導体領域18及び反対導電型のドーパントを含む第2のドープされた半導体領域28がSOI基板の埋め込み絶縁層20の直下に形成される。第1のドープされた半導体領域18及び第2のドープされた半導体領域28は、共にグランド電位に接続されるか、又は底部半導体層への少数キャリアの順方向バイアス注入に基づく過剰な電流を生じるには不十分は電圧、即ち、0.6V乃至0.8Vを越えない電位差を保って底部半導体層に対して順方向バイアスされる。上部半導体の半導体装置内の電気信号により誘起される電荷層内の電荷は第1及び第2のドープされた半導体領域に接続されている電気的コンタクトを介して引き出され、これにより半導体装置内の高調波信号を減少させる。

(もっと読む)

半導体集積回路の検証装置、方法およびプログラム

【課題】意図的に導入された実験箇所を含む半導体集積回路装置のレイアウトデータから本来の欠陥のみを抽出する検証装置を提供すること。

【解決手段】検証装置は、設計者により意図的に導入された実験箇所を含む半導体集積回路のレイアウトデータを検証する装置であって、半導体集積回路に対する設計基準および実験箇所を含む1または2以上の検証ルールを生成する検証ルール生成部と、検証ルールに含まれる実験箇所を検証の対象から除外したレイアウトデータを検証ルールのそれぞれについて生成するレイアウトデータ生成部と、実験箇所を検証の対象から除外したレイアウトデータにおいて設計基準を満たさない箇所である欠陥を検証ルールのそれぞれについて抽出する欠陥抽出部とを備える。

(もっと読む)

電流波形解析方法及びその装置

【課題】回路の動作率を基に、統計的に作成した電流モデルを使用して回路シミュレーションを行い、短時間で電流波形に含まれるスペクトルを解析する。

【解決手段】部分回路動作電流解析部10において部分回路の電流波形をデータベース(DB)化し、回路動作率解析部20における高速なシミュレータから得られた部分回路の動作率と、DB化された部分回路の動作とから、電流波形整形部50によって電流波形を作成し、回路シミュレーション部60によって複数回シミュレーションしている。そのため、電流波形の変動を高速に得ることができ、スペクトル解析部70において効率良く信号のスペクトル解析を行うことができる。

(もっと読む)

21 - 40 / 170

[ Back to top ]