Fターム[5F064HH08]の内容

ICの設計・製造(配線設計等) (42,086) | 設計、製造における計算機技術 (6,629) | ソフトウェア(プログラム)関係 (5,214) | 使用言語 (170)

Fターム[5F064HH08]に分類される特許

41 - 60 / 170

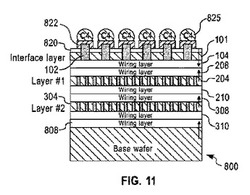

3次元集積回路の製造方法及び記録媒体(インターフェース・ウエハを永久的キャリアとして使用する3次元集積回路デバイスの製造方法)

【課題】 3次元集積回路構造を製造する方法を提供する。

【解決手段】 第1配線層及びスルー・シリコン・ビアを含むインターフェース・ウエハ並びに能動回路を含む第1の能動回路層ウエハを準備する。第1の能動回路層ウエハはインターフェース・ウエハにボンディングされる。次いで、第1の能動回路層ウエハの第2部分がインターフェース・ウエハに取り付けられたままになるように、第1の能動回路層ウエハの第1部分が除去される。インターフェース・ウエハ及び第1の能動回路層ウエハの第2部分を含む積層構造がベース・ウエハにボンディングされる。次に、インターフェース・ウエハはインターフェース層を形成するように薄くされ、そしてインターフェース・ウエハのスルー・シリコン・ビアを介して第1配線層に結合される金属がインターフェース・ウエハ上に形成される。

(もっと読む)

回路設計支援装置、装置のプログラム、プログラムを記録した記録媒体、回路設計支援方法、および半導体集積回路製造方法

【課題】配置配線ツールとレイアウト検証ツールとのそれぞれで用いる制約を自動生成するには、様々な手間がかかってしまっていた。また、目視確認で制約をチェックしていると、レイアウト制約の見落としにつながる虞もあった。

【解決手段】配置配線ツールとレイアウト検証ツールとを備えた回路設計支援装置について、配置配線ツールで用いる第1の制約と、レイアウト検証ツールで用いる第2の制約とを、共通のアサーションを含むものとして自動生成するようにする。

(もっと読む)

LSIの設計方法

【課題】LSIにおいて、信頼性やノイズ問題の生じない最少の電源パッド数と配置を決定する方法を提供する。

【解決手段】1) 電源線のエレクトロマイグレーション(EM)、2) 信号線間クロストーク、3) I/Oバッファの同時スイッチング・ノイズ(SSN)、4) 不要電磁放射(EMI)と共振、という順番で解析し、それぞれに予め設定された判定基準が満たされたかどうかの判定を行う。これにより、解析毎に必要な電源パッド数と配置が求められる。前記解析はLSIが持っている各機能の高品質化と処理の高速化を目的に、LSI内の各種の機能グループ(DDR2/HDMI/USB I/F、PLL回路、テスト端子等)毎に行うことが好ましい。そして、機能グループ毎に判定基準を満たす電源パッド数と配置を決定する。

(もっと読む)

回路設計装置および回路設計方法

【課題】必要な箇所に確実にエラー発生回路を配置する。また、ハードウェア回路の規模の増大を防止する。

【解決手段】回路設計装置1は、設計データ格納部2と、抽出部3と、回路配置部4とを有している。設計データ格納部2は、回路の設計データを格納する。抽出部3は、設計データ格納部2に格納されている設計データから、出力エラーチェックをするための機能を有する保護回路5、6を抽出する。回路配置部4は、抽出部3によって抽出された保護回路5、6にエラー検証用の検証用信号を供給するための信号供給用回路4aを配置し、信号供給用回路に選択的に検証用信号を供給するアクセス制御回路4cを配置する。

(もっと読む)

故障検出率向上用回路挿入方法

【課題】想定外の遅延による回路のパフォーマンス低下を回避可能な故障検出率向上用回路挿入方法を得ること。

【解決手段】本発明は、HDL記述による論理回路設計において、論理回路の故障検出率を向上させるための故障検出率向上用回路を挿入する場合の故障検出率向上用回路挿入方法であって、コンピュータの制御部が、論理合成により得られるネットリスト3を入力としてATPGを適用して故障検出率を算出し、また、ネットリスト3に基づいて仮配置配線を行い、目標となる故障検出率に達していない場合に、論理設計ファイル1,制約情報2,ネットリスト3,未検出故障情報4,遅延情報ファイル5およびタイミング制約ファイル6等に基づいて、故障検出率向上用回路を挿入する未検出故障箇所を決定する。

(もっと読む)

消費電力見積方法、回路設計支援装置及びプログラム

【課題】消費電力見積方法、回路設計支援装置及びプログラムにおいて、RTL消費電力見積の簡易さと高速性が損なわれることなく高精度の消費電力見積を行うことを目的とする。

【解決手段】回路に関するRTL設計データに基づいて簡易ネットリストを生成し、前記回路に関するRTLシミュレーション結果に基づいて活性化率データを生成し、前記簡易ネットリストから前記回路に含まれる組み合わせ回路を抽出すると共に、前記RTLシミュレーション結果から前記組み合わせ回路への入力データを抽出し、前記入力データを前記組み合わせ回路に適用した再シミュレーションにより差分活性化率データを生成し、前記活性化率データと前記差分活性化率データをマージしたデータに基づいて、前記RTL設計データに無い信号データの活性化率データを確率伝播技術により算出し、前記確率伝播技術により算出した活性化率データに基づいて前記回路の消費電力を見積もる。

(もっと読む)

検証支援プログラム、検証支援装置、および検証支援方法

【課題】効率的かつ信頼性の高い論理検証作業をおこなうこと。

【解決手段】関連性強度を『強』、『弱』、『無し』の3パターンに分けている。なお、仕様から求めた入力ゲートの組み合わせの関連性強度は、『強』、『弱』、『無し』の3パターンから選択される。どのパターンを選択するかは仕様の内容に応じてユーザが決定する。仕様と実装で、関連性強度が一致する場合、仕様と実装とで一貫性があることがわかる。また、使用と実装のうち一方が『強』で他方が『弱』である場合、一貫性がないため、警告する。また、仕様が『強』または『弱』で実装が『無し』の場合、実装に漏れがある可能性があるため、警告する。一方、実装が『強』または『弱』で仕様が『無し』の場合、仕様には記載がなくても実装すると関連する場合もあるため、参考程度に警告する。

(もっと読む)

セルライブラリ並びにその作成方法及び作成プログラム、半導体集積回路並びにその設計方法及び設計プログラム

【課題】アンテナエラーを低減すること等が可能なセルライブラリ等を提供する。

【解決手段】セルライブラリに含まれるセル30は、セル30の内部に信号を入力するための入力ピン32と、セル30の左辺と入力ピン32との間に配置され、最上層以外の配線層の配線の配置を防止するための仮想的な第1の障害物34と、第1の障害物34を挟んでセル30の左辺に沿って配置され、全ての配線層の配線の配置を防止するための仮想的な一対の第2の障害物35、36と、を含む。

(もっと読む)

クロック分配回路のレイアウト生成方法、および半導体集積回路装置

【課題】再収斂分岐構造を含むクロック分配回路のレイアウト生成において、冗長な迂回配線を生じさせることなく、クロックスキューを低減可能にする。

【解決手段】クロック分配回路の基本セル構成を解析し(S201)、解析された基本セル構成を基にして、クロック経路にクロックバッファを挿入する(S202)。その後、基本セルとクロックバッファとを配置し(S203)、配線を配置する(S105)。解析ステップ(S201)において、クロックの各経路における基本セルの段数の最大値を求め、挿入ステップ(S202)において、クロックの各経路におけるセル段数が、この最大値以上でかつ同じ値になるように、クロックバッファを挿入する。

(もっと読む)

半導体集積回路配置プログラム及び方法

【課題】ブロック配置を含むIC設計作業において、やり直し等を削減でき、設計の工数等を低減でき、設計効率を向上できる技術を提供する。

【解決手段】本ブロック配置方法及びプログラムでは、実配置処理の前の段階で、ブロック配置領域の大きさを見積もり、局所的配線混雑の発生を判定し、その結果に基づいてユーザによるブロックの最適な位置の決定を可能とする。S1でブロック間接続情報を抽出し、S2でブロックの回路ゲート物量情報を抽出する。S3,S4でユーザによりGUIの画面でブロックの位置を決定する。S5で配線の要求混雑度を評価して画面に表示する。S6でユーザにより配置の妥当性を判定し、OKであれば、S7で実現性の高いブロック配置情報が出力される。

(もっと読む)

システムLSIの電力見積方法及びそれに使用する設計済みブロックの電力ライブラリの生成方法。

【課題】LSIの初期の設計段階で少ない工数で比較的高精度の電力を見積もる

【解決手段】C言語またはハードウエア記述言語で機能記述されたLSIデータの電力見積方法では,LSIデータは複数のブロックを有する設計済み回路マクロのデータを有し,電力見積方法は,LSIデータの論理シミュレーションを実行し,LSIデータに含まれる複数の命令の実行に対応する回路マクロ内のブロックの動作モード履歴を出力するLSIシミュレーション工程と,回路マクロ内の複数のブロックのうち少なくとも一部のブロックについて動作モード毎の電力変動範囲データと残りのブロックについての電力変動範囲データとを有する電力ライブラリを参照し,動作モード履歴に対応する電力変動範囲を抽出し当該抽出した電力変動の範囲を累積してLSIデータの電力変動の範囲を生成する電力見積工程とを有する。

(もっと読む)

タイミング解析容易化装置、タイミング解析容易化方法、プログラム、及び記録媒体

【課題】正確なタイミング情報を得ることができるタイミング解析容易化装置、タイミング解析容易化方法、プログラム、及び記録媒体を提供する。

【解決手段】タイミングを解析する工程と、タイミングを解析する際にPLLをタイミングモデルとして取り扱う工程と、タイミングを解析する際にPLLを特定する工程とを備えたことにより、タイミング解析装置がPLLを認識する事ができるので、特に指定すること無しにPLLを特定しタイミングモデルに含まれるPLLに関する情報をタイミング解析装置が取得することができ、その結果正確なタイミング情報を得ることができる。

(もっと読む)

半導体集積回路及びその設計方法並びに半導体集積回路設計装置

【課題】マクロとユーザロジック回路との間の遅延故障を検出するマクロ境界テストにおいて必要なテストパタンの数を減少させる。

【解決手段】本発明の半導体集積回路10は、マクロ1と、マクロ1の入力に接続されたデータ出力52を有し、且つ、マクロ1と同じクロックで動作する制御用フリップフロップ3とを備えている。制御用フリップフロップ3は、データ入力52とは別に設けられた外部制御入力51及びマクロテストモード切換入力53に供給される外部制御信号及びマクロモード切換信号により、そのデータ出力を前記クロックに同期してトグルする動作を行うように設定可能であるように構成されている。

(もっと読む)

集積回路の設計支援装置、集積回路の設計支援方法、集積回路の設計支援プログラム、及びこのプログラムが記録された記録媒体

【解決課題】集積回路の論理設計の段階で最適な配線長や配線混雑を見積もることができ、実装設計段階で判明した配線ディレイを原因とする論理設計や機能設計のやり直しを防ぎ、以って集積回路の設計に要する時間を短縮することができる集積回路の設計支援装置等を提供する。

【解決手段】本発明は、集積回路の論理設計の段階で、モジュール間の配線長とモジュールにおける配線混雑を正確に見積もり(222,230)、その上で集積回路の論理設計結果を集積回路の実装設計に反映させる(224,226)ものである。

(もっと読む)

半導体回路設計プログラム、半導体回路設計装置および半導体回路

【課題】低消費電力、省回路サイズとともにレイアウトが容易な半導体回路を設計する。

【解決手段】半導体回路設計装置100は、設計対象回路111の構成が記述されたネットリスト110を取得し、取得されたネットリスト110に含まれるフリップ・フロップと、当該フリップ・フロップ外のトランジスタとを抽出する。さらに、抽出されたフリップ・フロップを、当該フリップ・フロップよりも入出力ビット数の大きなフリップ・フロップとなるように所定数ごとに統合する。そして、統合後のフリップ・フロップの数と、抽出されたトランジスタの数との比率を算出し、この比率に応じた統合後のフリップ・フロップとトランジスタとを基本ブロックとする半導体回路121の設計データ120を生成する。

(もっと読む)

半導体集積回路の設計方法、半導体集積回路の設計プログラム、及び半導体集積回路

【課題】本発明によれば、メモリマクロ配置領域を効率的に使用してメモリを配置する。

【解決手段】本発明による半導体集積回路1は、メモリ101と、逓倍器103と、制御回路とを具備する。メモリ101は、複数のインスタンスI10、I20に対応する複数のメモリ領域を有する。逓倍器103は、第1クロック信号CLKx1の周波数を逓倍した第2クロック信号CLKx2を複数のメモリ領域に出力する。制御回路は、複数のメモリ領域においてアクティブとなるデータ信号線を、第1クロック信号に同期して選択する。

(もっと読む)

設計支援プログラム、該プログラムを記録した記録媒体、設計支援装置、および設計支援方法

【課題】所定の配線領域内における仕様の回路特性を満たす配線長の配線を自動化することにより、作業負担の軽減化および設計期間の短縮化を図ること。

【解決手段】設計支援装置は、所定の配線領域内に配置された第1および第2の端子を接続する配線経路と、所定の配線領域内でかつ該配線経路と非接続な巡回路とを探索し、探索された配線経路の配線経路長と巡回路の配線経路長とを合わせた配線経路長を算出し、算出された配線経路長が、仕様の回路特性を満たす配線経路長以上か否かを判定し、判定された判定結果を出力する。これにより、探索困難な端子間の最長配線経路の換わりに、比較的に探索容易な端子間の任意の配線経路と巡回路とを合わせた最長配線経路候補を用いて、所定の配線領域における仕様の回路特性を満たす配線経路長の実現可能性を判定することができる。

(もっと読む)

セルデータの検証装置、方法、およびプログラム

【課題】個々のセルデータ自体の自動配線への適合性を評価する。

【解決手段】電子装置の他の部分と配線によって接続され、前記電子装置の機能を実現するセルを定義するセルデータの検証装置である。本検証装置は、セルを電子装置の他の部分と接続する端子の定義を含むセルデータを入力する手段と、セルデータの電子装置内での配置を模擬した検証用の配置情報を入力する手段と、配置情報で配置されるセルの端子と接続されるべき相手端子の定義データを生成する手段と、セルデータを配置情報にしたがって配置するとともに、相手端子の定義データを付加したレイアウトデータを作成するレイアウト手段と、自動配線システムにセルデータとレイアウトデータとを入力することによって相手端子から配置されたセルの端子に至る配線データを発生させる、自動配線を起動する手段と、自動配線システムからの自動配線の結果を報知する報知手段とを備える。

(もっと読む)

半導体装置及びその設計方法

【課題】要素回路ブロック間の配線構造に拘わらずアンテナフリーな回路構造の半導体装置を得ることを目的とする。

【解決手段】配線データD21で規定される配線が入力端子PIに接続される。入力端子PIはトランスファゲートTF3を介して入力用素子であるインバータG1の入力部に接続される。このトランスファゲートTF3はNMOSゲートQ3Nに電源電圧が付与され、PMOSゲートQ3Pに接地レベルが設定されることにより常時オン状態に設定される。

(もっと読む)

半導体集積回路の設計方法

【課題】半導体集積回路のノイズが抑制可能で、設計期間が短縮可能な半導体集積回路の設計方法を提供する。

【解決手段】最低セル配置間隔決定部(配置禁止領域決定部)13が個々のセルの単位時間当たりの平均動作回数及び使用電圧をもとに、セル間の最低セル配置間隔を個々のセルごとに決定して配置禁止領域を決定し、セル配置部14が配置禁止領域にセルが配置されないように配置していくことで、ノイズを抑制可能な半導体集積回路の設計ができるとともに、TATを短くでき、設計期間が短縮される。

(もっと読む)

41 - 60 / 170

[ Back to top ]