Fターム[5F064HH08]の内容

ICの設計・製造(配線設計等) (42,086) | 設計、製造における計算機技術 (6,629) | ソフトウェア(プログラム)関係 (5,214) | 使用言語 (170)

Fターム[5F064HH08]に分類される特許

101 - 120 / 170

半導体集積回路における試験時の電源供給方法および半導体集積回路用CADシステム

【課題】 フリップチップ構造の半導体集積回路の試験を低コストで確実に実施する技術を提供する。

【解決手段】 電源供給口決定工程では、電源網解析により電圧降下違反または電流密度違反のいずれも検出されない範囲で、複数の電源バンプの一部が試験時の電源供給口として決定される。詳細には、電源供給口決定工程では、まず、消費電力情報に基づいて試験時の電源供給口の必要最小数が求められ、複数の電源バンプの中から必要最小数の電源バンプが試験時の電源供給口として決定される。そして、電源網解析による電圧降下違反の検出時に違反発生箇所に対応する電源パンプを試験時の電源供給口として追加し、電源網解析による電流密度違反の検出時に違反発生箇所のレイアウトを修正する処理が、電源網解析により電圧降下違反または電流密度違反のいずれも検出されなくなるまで繰り返し実施される。

(もっと読む)

集積回路の設計を最適化するための方法とシステム

【解決手段】集積回路を最適化及び/設計するための方法及びシステムを提供する。集積回路(IC)を設計するプロセスの一部として、第1セットの配線リソースを使用して、IC表現上で接続を経路指定し、第1セット内の配線リソースが一旦経路指定に使用されたら、配線リソースに使用済みとマーキングする段階と、前記表現で第2セットの配線リソースを使用して、前記第2セット内の配線リソースが以前に接続を経路指定するのに使用されているか否かを確認すること無く、IC上の接続の経路指定を行う段階と、を含んでおり、第2セットの配線リソースは、平均で、物理的な寸法が、第1セット内の配線リソースとは異なっている。ICを最適化及び/又は設計するための他の方法及びシステムについても説明されており、更に、システムに1つ又はそれ以上これらの方法を実行させる実行可能なプログラム命令が入っている機械読み取り可能な媒体についても説明されている。 (もっと読む)

三次元集積回路設計装置および三次元集積回路設計方法

【課題】設計コストと設計時間を節約しつつ、性能的に優れた三次元集積回路を設計する。

【解決手段】三次元集積回路設計装置は、半導体回路生成部1と、ネットリスト生成部2と、二次元レイアウトデータ生成部3と、三次元レイアウトデータ生成部4とを備えている。二次元レイアウトデータを複数のレイアウトブロックデータに分割して、そのうちの一部を裏表に反転して、複数の基板上に各レイアウトブロックデータを配置するため、二次元レイアウトデータをフルに利用して、二次元的な面積を大幅に削減可能な三次元集積回路を作製できる。

(もっと読む)

検証方法及び検証装置

【課題】 検証対象の内部仕様を漏れなく定義することなく、外端の仕様のみが定義された検証対象に対して、擬似エラーの発生を抑止し、検証精度を向上させる。

【解決手段】 内部構成抽出器21で論理システム(DUT)11の内部構成を抽出し、内部ブロック入出力制約条件生成器22でDUT内部構成表13により内部構成の入出力制約条件を生成する。そして、論理システム11の仕様を表すプロパティを検証用のプロパティに基づいて検証を行い、検証したプロパティの反例16と矛盾する入出力制約条件14を検証用の更新プロパティ17に追加して更新する。

(もっと読む)

回路記述言語の等価性検証方法

【課題】検証を容易に出来る回路記述言語の等価性検証方法を提供すること。

【解決手段】回路記述言語の等価性検証方法は、第1回路記述言語により記述された、半導体集積回路に関する第1設計データ10を回路合成して、前記第1回記述言語よりも抽象度の低い第2回路記述言語により記述された第2設計データ14を得るステップと、前記第2回路記述言語により記述された第3設計データ20と、前記第2設計データ14とを比較して両者の対応関係を検証し、対応しない部分について形式的検証を行うステップとを具備し、前記第2、第3設計データ14、20が全て対応した場合、及び前記対応しない部分について形式的検証を行った結果、両者が等しい場合、前記第1設計データ10と前記第3設計データ20とは等価であると判定される。

(もっと読む)

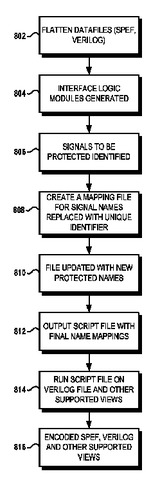

EDAツール設計ビューにおける情報を保護する方法およびプログラム・プロダクト

ある種のEDAツール設計ビュー内のモジュール名および構造といった、HDLインターフェース論理モデルにおける機微な回路設計情報(806)が、設計ビューを回路設計のシミュレーション・モデルの一部として移転するのに先立って、選択されたインスタンスおよびネット名を、無関係な一意的な識別子(808)で置き換えることによって消去される。結果として、その情報の許諾されていない使用が避けられる。IC設計の種々の設計ビューにおける信号名をエンコードする方法は、複数の設計データベースに含まれる名前のリストを提供し(806)、名前のリスト内の各名前を保護された名前に変え(808)、各設計ビュー・データベース中の関連付けられた保護された名前をそれぞれの変更された名前に置き換える(810、812、814、816)ことを含む。

(もっと読む)

(もっと読む)

ICレイアウトの電気特性の計算

集積回路内に生成される機構の電気特性を計算するためのシステム。所望のレイアウト設計の全部または一部は、1つ以上の分解能向上技術を使用して、フォトリソグラフィまたは他のプロセス歪みに対し補正される。補正レイアウトのシミュレーションによるレイアウトイメージは、機構の電気特性を計算する電磁界解析プログラムへの入力として使用され、ウエハ上に転写される。本発明はまた、集積回路レイアウト設計内の機構の電気特性を計算するための方法を提供する。  (もっと読む)

(もっと読む)

回路設計の回路素子をクラスタ化する方法、装置及びコンピュータ読み取り可能な記録媒体

【課題】 集積回路装置の設計に使用される方法、装置及びコンピュータ読み取り可能な記録媒体を提供する。

【解決手段】 上記方法、装置及びコンピュータ読み取り可能な記録媒体は、所望の空間的位置の距離を最適化するように回路素子をクラスタ即ちグループに割り当てる。例えば、スキャン時にイネーブルされるラッチが、回路設計のためのスキャン・アーキテクチャにおけるスキャン・チェーンのレイアウトを最適化するように、ヒューリスティクスなクラスタ化を使用して各スキャン・チェーンに割り当てられることができる。

(もっと読む)

半導体集積回路のシミュレーション方法

【課題】バスを有する半導体集積回路について、シミュレーションを高速に行う。

【解決手段】半導体集積回路のシミュレーション方法であって、前記マスターブロックのモデルがその共通化ポートから共通化インタフェースを用いて前記バスのモデルにアクセスし、前記バスのモデルがその共通化ポートから前記共通化インタフェースを用いて前記スレーブブロックのモデルにアクセスするモデルについてシミュレーションを実行する高精度シミュレーションステップと、前記マスターブロックのモデルがその共通化ポートから前記共通化インタフェースを用いて前記バスのモデルを介さずに前記スレーブブロックのモデルにアクセスするモデルについてシミュレーションを実行する抽象化シミュレーションステップとを備える。シミュレーションに必要とされる精度に応じて、前記高精度シミュレーションステップ又は前記抽象化シミュレーションステップを選択して実行する。

(もっと読む)

半導体集積回路の設計支援装置、設計支援方法および設計支援プログラム

【課題】ネットリスト修正によるレイアウト後の遅延劣化の有無を早期に発見する。

【解決手段】修正前のネットリスト(試行ネットリスト)および修正後のネットリスト(評価対象ネットリスト)に対して、ネットリストから抽出されるパスの段数とパス長とを求め、求めた段数とパス長とに基づいて、遅延改善の難しさを示す遅延難易度を算出する。そして、試行ネットリストにおけるパスの遅延難易度と評価対象ネットリストにおけるパスの遅延難易度との差分と、および試行ネットリストの実負荷遅延検証での遅延値とに基づいて、評価対象ネットリストの実負荷遅延検証での遅延増加および遅延値を予測する。試行ネットリストのネットリストと初期配置時の配置情報と実負荷遅延検証での遅延値とを与えることにより、評価対象ネットリストの初期配置を行った段階で、段数変化による遅延劣化を検出でき、パス長変化による遅延劣化の可能性も検出できる。

(もっと読む)

半導体集積回路の高位合成方法

【課題】回路記述流出時の不正利用と設計情報不正解読のリスクを低減するために、設計情報を秘匿化(設計情報隠蔽と回路記述難読化)した回路記述を生成する半導体集積回路の高位合成方法を提供する。

【解決手段】ハードウェアの動作レベル回路記述を解析して得られた中間表現であるCDFG(Control Data Flow Graph)に対して、設計情報を秘匿化するため、スケジューリング前又はスケジューリング後に、演算の追加によるCDFGの変形処理を施す。ハードウェアリソースのアロケーション処理済みのCDFGに対して、ハードウェアリソースの割り付け変更処理を施してもよい。

(もっと読む)

半導体装置

【課題】チップサイズを縮小する。

【解決手段】マクロセルMC3上をX方向に延在するセル外配線をマクロセルMC3の信号用の端子Tsよりも上層の配線層で構成し、この端子Tsをセル外配線の複数のチャネル分を確保するように、Y方向(X方向に交差する方向)に延在させて構成する。マクロセルMC3と、セル外配線との接続をこの信号用の端子Tsを介して行う。

(もっと読む)

回路設計装置、回路設計プログラム、及び回路設計方法

【課題】低消費電力化と回路の簡素化を実現するための論理設計を行う回路設計装置を提供する。

【解決手段】回路設計装置は設計対象RTLを解釈して構造解析を行う(S2)。構造解析の結果に基づいてクロックゲーティングを予測してEN生成論理のRTL記述を検出し(S3)、かつ、同一のEN生成論理を検出する(S4)。検出されたEN生成論理からクロックゲーティング回路の挿入位置と論理階層の組み替えを決定して(S5)、論理合成における論理階層組み換えの指示(S8)と設計変更処理を行う(S6)。設計変更後のRTLと論理階層組み換えの指示とによって論理合成を行い(S10)、具体的な回路構成にレイアウトする(S12)。

(もっと読む)

半導体集積回路装置の歩留まり向上方法、システム、プログラム、記録媒体、マスク及び装置

【課題】デザインルールの欠陥率を用いて関心レイアウトを修正することによって歩留まりを極大化する半導体集積回路装置の歩留まり向上方法を提供する。

【解決手段】本発明の半導体集積回路装置の歩留まり向上方法は、多数の実験デザインルール値に対応する多数の欠陥率と、関心レイアウト内で前記多数の実験デザインルール値各々に該当するフィーチャの数に基づいて前記デザインルールの欠陥率を算出し、前記デザインルールの欠陥率に基づいて関心レイアウトを修正することを含むことを特徴とする。これにより、歩留まりが極大化されたレイアウトをデザインすることができる。

(もっと読む)

半導体集積回路およびその設計方法

【課題】クロック信号に同期して動作する同期回路において、簡単な構成の回路で、ノイズの発生やIRドロップ、ピーク消費電流の増大などを大幅に低減することができる半導体集積回路およびその設計方法を提供する。

【解決手段】本発明の半導体集積回路は、複数の組み合わせ回路間に挿入された複数のフリップフロップと、複数のフリップフロップにクロック信号を分配するクロックツリーとを有し、クロック信号により同期動作する。複数のフリップフロップは、クロックツリーからクロック信号が正相で分配され、この正相のクロック信号の立ち上がりエッジに同期して動作する複数の正エッジフリップフロップと、クロックツリーからクロック信号が逆相で分配され、この逆相のクロック信号の立ち下がりエッジに同期して動作する複数の負エッジフリップフロップとを含む。

(もっと読む)

FPGA及びASICのネットリストを生成する方法

【課題】ASICとFPGAの設計品質を確保するとともに開発期間を短縮すること。

【解決手段】回路アーキテクチャ検討結果であり論理設計ドキュメントの一部であるブロックのポート仕様の接続情報のみを用いてデバイス・テクノロジに依存しないブロックのポートとポート間を結ぶネットからなるコア(論理コア)と呼ぶネットリストを生成し、コア(論理コア)から対象ブロックを選択、グループ化し、グループ化したコア(論理コア)のデータを使用する集積回路の開発方法。

(もっと読む)

集積回路内でのエラー伝播に基づくエラー検出回路の挿入

エラー検出回路(20)が集積回路内のどこに置かれるべきかを選択する方法は、基準及びテスト設計の模擬を用い、エラーがテスト設計に注入され、ファンアウト分析がそれら注入されたエラーの上に行われて、エラー伝播特性を識別する。このように、伝播されたエラーがそれら自体を大いに現しそうでキー構造状態を保護するレジスタ(12)が識別され、エラー検出機構の効率的な配置が達成される。集積回路(68)内で、不活性な回路要素からの出力信号は、集積回路の検出された現時の状態に依存して隔離ゲート(92、94、96、98、100)を受け得る。このように、ソフト・エラーが生じる不活性な回路要素は不適切な出力信号を有し、集積回路の残りに到達することからゲーティングされて誤った動作を減少する。  (もっと読む)

(もっと読む)

レイアウト装置、自動配置配線方法および半導体集積回路製造方法

【課題】 半導体集積回路チップ内の回路の自動配置を行うレイアウト装置において、クロックゲーティング回路の配置位置等を制御することで低消費電力化を図る。

【解決手段】 回路情報に基づいて半導体集積回路内の回路部分の配置・配線を行うレイアウト装置であって、クロックラインに挿入されているクロックゲーティング回路を認識する手段と、認識されたクロックゲーティング回路以外の回路部分の配置を行う手段と、クロックゲーティング回路の配置およびクロックツリー構築を、低消費電力化を考慮した上でクロックスキューを調整しつつ実施する手段とを備える。

(もっと読む)

論理検証手法および論理検証装置

【課題】 内部構成や仕様が明確でない検証対象に対し、外端の動作仕様のみを用いて検証をおこなうと検証抜けが生じ、検証精度が低下する。十分な検証精度が得られないことにより、十分な精度を持つ論理システムを予定の期間内に完成させることができず市場が欲するときに製品を投入できないという課題や不十分な精度のまま製品を市場に投入してしまう課題が生じる。

【解決手段】 機能ブロックを定義するプロパティを予め登録しておく。このプロパティを用いて検証対象の内部構成を抽出する。この内部構成から、予め登録したプロパティに一致しない部分について、入出力制約条件を求める。この入出力制約条件を用いて論理検証をおこなう。

(もっと読む)

論理合成方法及び論理合成装置

【課題】

LSI(LargeScale Integration)設計の効率化に好適な論理合成方法及び論理合成装置、特に、論理合成に使用するライブラリの向上を図ることにより、LSIの目標性能の達成を早期に行うことを特徴とする論理合成方法及び論理合成装置を提供することを課題とする。

【解決手段】

上記の課題を解決するため、本発明は、RTL設計段階で、早期にLSI回路のパフォーマンスを見積もることを可能とする論理合成方法及び論理合成装置を提供する。すなわち、バッファトリーの特性記述を含むライブラリを作成する工程、論理設計の記述を解析してファンアウト数が多い箇所を特定する工程、ファンアウト数が多い箇所を含めたバッファトリーの構成を特定する工程、及び、そのライブラリを適用して、論理設計の記述に基づき論理合成をする工程を含むことを特徴とする論理合成方法を提供する。

(もっと読む)

101 - 120 / 170

[ Back to top ]