Fターム[5F082BA38]の内容

Fターム[5F082BA38]の下位に属するFターム

Fターム[5F082BA38]に分類される特許

1 - 20 / 27

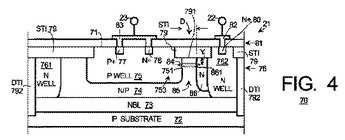

ESD保護デバイスおよび方法

関連するデバイスまたは回路24を保護する静電気放電(ESD)保護クランプ21、21’、70、700は、バイポーラ21、21’、70、700を備える。アバランシェ降伏が、上にある誘電体・半導体界面791から離れ、デバイス70、700のベース領域74、75の部分84,84以内に望ましく起こるように向かうベース75およびコレクタ86領域のドーパントを構成される。例えば、半導体ダイまたはウェハのトランジスタ21、21’、70、700の異なる方位配向のおかげで、ESDトリガ電圧の最大変化(△Vt1)MAXはベース・コレクタ間隔寸法Dの関数である。トリガ電圧一貫性および製造歩留まりが改良される。  (もっと読む)

(もっと読む)

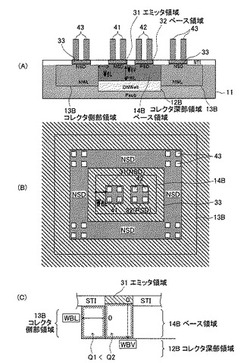

半導体デバイスおよびその製造方法

【課題】CMOS回路側の仕様で不純物領域の深さや濃度が制約を受けるような場合でもhFEの向上を可能とする。

【解決手段】1つのバイポーラトランジスタが、横型の主トランジスタ部と、縦型の補助トランジスタ部とから形成されている。横型の主トランジスタ部は、エミッタ領域31と、ベース領域14Bの表面側部分とコレクタ側部領域13Bとを電流チャネルとして動作する。縦型の補助トランジスタ部は、エミッタ領域31と、その底面に接するベース領域14Bの深部側部と、コレクタ深部領域12Bとを電流チャネルとして動作する。

(もっと読む)

有機トランジスタ、回路素子及びそれらの製造方法

【課題】低電圧で作動するとともに大きなベース電圧を印加した場合でも耐電圧が高く、各種の回路素子への応用が容易で、製造コストを抑えた有機トランジスタ及び回路素子を提供する。

【解決手段】コレクタ電極1とエミッタ電極2と両電極間に設けられた有機半導体層3と有機半導体層3内に設けられたベース電極4とを有する縦型トランジスタ部、及び、ベース電極4とベース電圧電源端子7との間に設けられた抵抗部6、を有する。抵抗部6は、コレクタ電極1と同じ材料からなりベース電圧電源端子7に接続する第1電極21と、エミッタ電極2と同じ材料からなりベース電極4に接続する第2電極22と、有機半導体層3と同じ材料からなり第1電極21及び第2電極22間に挟まれた抵抗層24とを有する。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】バイポーラトランジスタが動作する際に、ベース領域のうちコレクタ側の端部が破壊されることを抑制する。

【解決手段】ベース領域150は、ウェル110内に形成されている。エミッタ領域170はベース領域150の中に形成され、ベース領域150より浅い。コレクタ領域140はウェル110内に形成され、ベース領域150の外側に位置している。第1埋込領域180は、少なくとも一部がベース領域150の中に位置しており、ベース領域150よりも不純物濃度が高い。そして第1埋込領域180は、平面視において、エミッタ領域170とコレクタ領域140の間に少なくとも一部が位置している。また第1埋込領域180は、エミッタ領域170の縁のうち少なくとも一辺と重なっており、かつエミッタ領域170の全面には重なっていない。

(もっと読む)

電源回路及び光受信回路

【課題】光信号により起動制御が可能な電源回路及び光受信回路を提供する。

【解決手段】半導体基板の上に設けられ、光信号を電気信号に変換する起動回路と、前記半導体基板の上に設けられ、電源投入時に非起動状態であるバイアス回路と、を備え、前記起動回路は、p型半導体領域と、前記p型半導体領域と接して設けられたn型半導体領域と、を有し、前記p型半導体領域は、前記バイアス回路と電気的に接続され、前記n型半導体領域は、前記バイアス回路の電源と電気的に接続され、前記バイアス回路は、前記起動回路を流れる電流により起動状態となることを特徴とする電源回路が提供される。

(もっと読む)

静電破壊保護回路

【課題】 静電破壊保護回路の動作開始電圧を下げるためトリガ素子を接続した場合であっても、静電破壊保護回路の静電破壊耐量を向上させることができる静電破壊保護回路を提供する。

【解決手段】 トリガ素子が接続される別のベース電極部拡散領域の周囲に、ベース領域より不純物濃度が低く、かつベース領域より深く形成されたP型拡散領域11を備える構造とすることで、別のベース電極部拡散領域近傍で生じる高電界を緩和し、またコレクタの一部を構成する埋め込み領域近傍で、ベース電流供給に必要な高電界を生じさせることができ、静電破壊耐量を向上させている。

(もっと読む)

半導体装置

【課題】従来の半導体装置では、製造条件のばらつきにより、保護素子よりも先に被保護素子がオン動作し、過電圧から被保護素子が保護し難いという問題があった。

【解決手段】本発明の半導体装置では、保護素子1とNPNトランジスタ11との構成の一部を共用する。そして、保護素子1では、N型の拡散層10とP型の拡散層6との離間距離W1が、N型の拡散層9とP型の拡散層6との離間距離W2よりも短くなる。この構造により、出力端子に過電圧が印加された際に、NPNトランジスタ11よりも保護素子1の方が先にオン動作し、過電圧からNPNトランジスタ11が保護される。

(もっと読む)

半導体双方向スイッチング装置

【課題】本発明は、スーパージャンクション構造を有し双方向スイッチングが可能な半導体双方向スイッチング装置を提供する。

【解決手段】二つの主電極の両方に電子とホールの制御部を設け、スーパージャンクションを構成するn形半導体層とp形半導体層における電流を制御する。

(もっと読む)

半導体装置及びその製造方法

【課題】 高温時のウェーハ反りを抑制し、チッピングや欠けを回避した自己発熱を半導体基板裏面から放熱できる放熱特性改善がされた薄型半導体装置及び製造が容易なその製造方法を提供する。

【解決手段】 複数の素子領域及び当該素子領域を区画する素子分離領域14を有する半導体基板9と、素子領域に形成された半導体素子とを有する。素子分離領域は、DTI(Deep Trench Isolation) 構造であり、その底面は半導体基板9裏面に露出し、その内部は空洞になっている。この半導体基板は半導体素子を形成後に半導体基板裏面を素子分離領域14の底面が露出するまで研磨もしくはエッチングして半導体基板9を薄くすると共に素子分離領域14内部を空洞にする。

(もっと読む)

半導体装置

【課題】 コレクタ・エミッタ間の耐圧が異なる複数のバイポーラトランジスタを同一基板上に容易に混載可能な技術を提供ことにある。

【解決手段】 同一基板上に高周波バイポーラトランジスタと高耐圧バイポーラトランジスタとを混載した半導体装置において、高周波バイポーラトランジスタと高耐圧バイポーラトランジスタは、同一膜厚のエピタキシャル成長層上に形成されており、また、同一プロセスにより形成された同一の不純物プロファイルを持つ埋め込みコレクタ領域を備えた構造であり、高周波バイポーラトランジスタのベース直下には埋め込みコレクタ領域が存在し、高耐圧バイポーラトランジスタのベース直下には埋め込みコレクタ領域及びSIC領域が存在せずに、高耐圧バイポーラトランジスタのベース領域とコレクタプラグ領域との距離が高周波バイポーラトランジスタの同距離と比べて等しいか大きいことを特徴としている。

(もっと読む)

ホットエレクトロントランジスタおよびそれを含む半導体装置

【課題】期待される高周波特性を得ること、ならびに後続の回路で必要とされる駆動電流を得ることが可能なホットエレクトロントランジスタを提供する。

【解決手段】このホットエレクトロントランジスタ100は、コレクタ層3と、ベース層5と、エミッタ層7と、コレクタ層3とベース層5との間に形成されたコレクタバリア層4と、ベース層5とエミッタ層7との間に形成されたエミッタバリア層6とを備えている。そして、エミッタバリア層6とエミッタ層7との間のエネルギー障壁は実質的に存在しないとともに、コレクタバリア層4のエネルギー障壁の高さはエミッタバリア層6のエネルギー障壁の高さよりも低い。

(もっと読む)

半導体装置

【課題】正孔の移動を十分に抑制することが可能な半導体装置を提供する。

【解決手段】この半導体装置(npn型のバイポーラトランジスタ100)は、n型コレクタ層2と、p+拡散層4、SiGe層5およびp型シリコン膜6からなるベース層と、n型エミッタ層8と、n型コレクタ層2とn型エミッタ層8との間に形成され、電子または正孔のいずれか一方に対する電位障壁としての効果を有する電荷移動防止膜7とを備える。

(もっと読む)

半導体装置及びその製造方法

【課題】従来の半導体装置では、電極パッドに過電圧が印加された際に、チップ内の回路素子が破壊されるという問題があった。

【解決手段】本発明の半導体装置では、N型のエピタキシャル層3は分離領域4、5により複数の素子形成領域に区画されている。素子形成領域の1つにNPNトランジスタ1が形成されている。NPNトランジスタ1の周囲には、PN接合領域21、22を有する保護素子が形成されている。PN接合領域21、22は、NPNトランジスタ1のPN接合領域20より接合耐圧が低い。この構造により、ベース電極用のパッドに負のESDサージが印加された際、PN接合領域21、22がブレークダウンし、NPNトランジスタ1を保護することができる。

(もっと読む)

半導体装置及びその製造方法

【課題】従来の半導体装置では、パワー用半導体素子の耐圧特性と制御用半導体素子のデバイスサイズの縮小化とを実現することが難しいという問題があった。

【解決手段】本発明の半導体装置では、P型の単結晶シリコン基板3上にN型のエピタキシャル層4が形成されている。基板3にはP型の埋込拡散層6が形成され、基板3とエピタキシャル層4には、N型の埋込拡散層10がP型の埋込拡散層7上に形成されている。この構造により、P型の埋込拡散層7の這い上がりが抑制され、パワー用半導体素子の耐圧特性を維持しつつ、エピタキシャル層4の厚みを薄くすることができる。そして、制御用半導体素子のデバイスサイズを縮小化することができる。

(もっと読む)

半導体装置及びその製造方法

【課題】従来の半導体装置では、パワー用半導体素子の耐圧特性と制御用半導体素子のデバイスサイズの縮小化とを実現することが難しいという問題があった。

【解決手段】本発明の半導体装置では、P型の単結晶シリコン基板3上にN型のエピタキシャル層4が形成されている。基板3とエピタキシャル層4には、N型の埋込拡散層9がP型の埋込拡散層6上に形成されている。この構造により、P型の埋込拡散層6の這い上がりが抑制され、パワー用半導体素子の耐圧特性を維持しつつ、エピタキシャル層4の厚みを薄くすることができる。そして、制御用半導体素子のデバイスサイズを縮小化することができる。

(もっと読む)

空乏可能コレクタ列を備えた改良されたBVCEO/RCS相殺を有するバイポーラ構造

【課題】本発明によれば、バイポーラトランジスタからなる集積回路の多様な製造方法を提供する。

【解決手段】本発明の一実施の形態によれば、バイポーラトランジスタは、基板と、複数の交互にドープされた領域を含み、複数の交互にドープされた領域は正味の第1導電型から正味の第2導電型へ横方向に交互に配置されたコレクタと、コレクタと電気的にコンタクトするコレクタコンタクトからなるように構成できる。また、バイポーラトランジスタは、コレクタの下において高濃度にドープされた埋め込み層と、ベースコンタクトと電気的にコンタクトし、正味の第2導電型にドープされ、複数の交互にドープされた領域の一部にかかるベースと、ベース内に配置され、正味の第1導電型にドープされたエミッタからなり、エミッタの下の複数の交互にドープされた領域の一部が、約3×1012cm-2未満の濃度でドープされていることを特徴とすることができる。

(もっと読む)

半導体装置

【課題】

チップ面積に対するダイオード領域の面積の縮小を図ること。

【解決手段】

基板1上に形成される絶縁ゲート型トランジスタと、基板1上に形成されるとともに、絶縁ゲート型トランジスタのゲートと端子との間に複数個直列に接続された複数のダイオードD1、D2、D3を有し、端子からのサージ電圧の印加によりブレークダウンするダイオードアレイと、を備える。ダイオードアレイは、P型の基板1上に形成されるとともに、ダイオードD1、D2、D3ごとにカソードとなる複数のN型ウェル2a、2b、2cを有する。N型ウェル2a、2b、2c間のそれぞれの間隔S1、S2は異なる。

(もっと読む)

半導体装置

【課題】 半導体装置において、反転領域対策を、既存の製造工程の条件を変えないで実現することを課題とする。

【解決手段】 N型エピタキシャル層4上にP型拡散層よりなる抵抗素子5が形成してあり、N型エピタキシャル層4上にシリコン酸化膜40が形成してあり、抵抗素子5の端から出ているアルミニウム配線8,9がシリコン酸化膜40上を延在している。シリコン酸化膜40は、N型エピタキシャル層4内に食い込んで厚みが増してある厚み付加部分42を枠状に有する。厚み付加部分42は、シリコン酸化膜40の反転電圧を上げる。厚み付加部分42は酸素イオンの注入及びアニール処理によって形成される。

(もっと読む)

化合物半導体装置

【課題】近接する2つの素子間に高濃度不純物領域を配置し、フローティング電位またはGND電位を印加することにより2つの素子間のアイソレーションを向上させる手法は、漏れた高周波信号のパワーが大きい場合に高濃度不純物領域の電位が変動してしまう。このため、結果として2つの素子間のアイソレーションが十分確保できなくなる問題があった。

【解決手段】近接する2つの素子間に伝導領域または金属層による分離素子を配置する。分離素子は高抵抗素子を接続し、直流端子パッドに接続する。また直流端子パッドから分離素子に至る接続経路は電位が高周波振動しない経路とする。これにより、少なくとも一方に高周波信号が伝搬する2つの素子の間に高周波GND電位を配置したこととなり、2つの素子間の高周波信号の漏れを防止できる。

(もっと読む)

カレントミラー回路を備えた半導体装置

【課題】 半導体装置内で温度勾配が生じたとしても、所望のカレントミラー比を実現することができるカレントミラー回路を備えた半導体装置を提供する。

【解決手段】 各トランジスタ群A、B、Cに備えられる複数のトランジスタA1〜Ak、B1〜Bm、C1〜Cnを、各トランジスタ群A、B、C毎に集合配置するのではなく、トランジスタ群A、B、Cの順に交互に並べられたレイアウトとする。言い換えると、トランジスタ群Aを構成する複数のトランジスタA1〜Akの1つと、トランジスタ群Bを構成する複数のトランジスタB1〜Bmの1つと、トランジスタ群Cを構成する複数のトランジスタC1〜Cnの1つ(例えばトランジスタA1、B1、C1)を1纏めとしたものを1セットとして、そのセットが繰り返しパターンとして形成されたレイアウトとする。

(もっと読む)

1 - 20 / 27

[ Back to top ]