Fターム[5F082BC20]の内容

Fターム[5F082BC20]に分類される特許

1 - 20 / 42

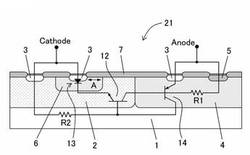

半導体集積回路のESD保護回路およびそのESD保護素子

【課題】従来構造に比べて、レイアウト面積の増加を抑え、保護能力の大幅な低下を招くことなく、保持電圧Vhを電源電圧以上の適正な電圧に制御する。

【解決手段】ESD保護素子21は、スナップバック特性を有するスナップバック特性素子としてのSCR素子と、このSCR素子に接続されて、スナップバック開始電圧Vt1を素子電圧分だけ加算すると共に保持電圧Vhを該素子電圧の2倍高くするための電圧加算素子としてのダイオード13とを有して、ダイオード13の素子電圧を調整して、保持電圧Vhを電源電圧Vcc以上で被保護素子の耐電圧以下に調整する。

(もっと読む)

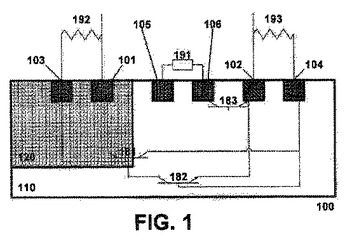

半導体装置

【課題】ホールド電圧を変化させずに、トリガー電圧のみを調節することができるようにする。

【解決手段】本実施形態における保護素子10は、低濃度コレクタ層102、シンカー層110、高濃度コレクタ層112、エミッタ層130、高濃度ベース層122、ベース層120、第1導電型層140、及び第2導電型層150を有している。第2導電型層150は低濃度コレクタ層102に形成されており、ベース層120と第1導電型層140の間に位置している。第2導電型層150は低濃度コレクタ層102よりも不純物濃度が高い。

(もっと読む)

半導体集積回路のESD保護素子およびそのESD保護回路

【課題】電源電圧以下の維持電圧Vhでも良好なESD保護を行う。

【解決手段】半導体集積回路のESD保護回路11は、電位端子とグランド電位間に、スナップバック動作を持つ第1のESD保護素子1としてのggMOSトランジスタと、スナップバック動作を持つESD保護素子1のスナップバック動作電圧Vt1に対して、低いブレークダウン電圧Vrを持ち、かつ高い破壊電圧Vt2を持つ第2のESD保護素子2としてのダイオードとが並列に接続されている。

(もっと読む)

抵抗変化型メモリ

【課題】 メモリの動作特性の向上を図る。

【解決手段】実施形態の抵抗変化型メモリは、ビット線BLとワード線WLと、第1エミッタ21と、第1ベース23と、第1コレクタ22とを有する、第1駆動型の第1バイポーラトランジスタ2と、第2エミッタ31と、第2ベース33と、第2コレクタ32とを有する第2駆動型の第2バイポーラトランジスタ3と、第1及び第2端子を有する抵抗変化型メモリ素子1と、を具備し、メモリ素子1の第1端子は第1及び第2エミッタ21,31に接続され、メモリ素子1の第2端子は、ビット線BLに接続され、第1及び第2ベース23,33はワード線WLに接続される。

(もっと読む)

半導体装置

【課題】占有面積を増大させずに、電源投入開始後のチップ動作時にESD保護素子で発生するリーク電流を低減することができるESD保護素子を提供する。

【解決手段】電源ライン及び接地ラインを含む電子回路が形成された半導体基板10と、半導体基板10において電源ライン(Vdd)及び接地ライン(Vss)間に設けられ、サイリスタSCR及びサイリスタを駆動するトリガーダイオードTDを含む静電気放電保護素子とを有し、トリガーダイオードは、半導体基板10に形成されたアノード拡散層22と、アノード拡散層22から離間して半導体基板10に形成されたカソード拡散層21と、アノード拡散層22及びカソード拡散層21間において半導体基板10上にゲート絶縁膜16を介して形成されたゲート電極17とを有し、外部電源に接続された外部端子(パッド電極27)がゲート電極17に電気的に接続されている構成とする。

(もっと読む)

高保持電圧デバイス

高保持電圧(HVO静電放電(ESD)保護回路が、シリコン制御整流器(SCE)デバイスと、SCRデバイスの保持電圧を高める、SCRデバイスのアノードとカソードとの間の長さ(LAC)内に設置された補償領域とを備える。補償領域は、負のフィードバック機構をSCRデバイスに導入することで、SCRのループゲインに影響を及ぼし、高保持電圧で回生フィードバックに達しうる。  (もっと読む)

(もっと読む)

化合物半導体素子及びその製造方法

【課題】高速動作が可能でかつ、ESD耐性の高い化合物半導体素子及びその製造方法を提供すること。

【解決手段】本発明に係る化合物半導体素子は、電界効果トランジスタ又はヘテロ接合バイポーラトランジスタからなるトランジスタ部と、トランジスタ部と並列に接続されたESD保護部114と、を備え、ESD保護部114は、第1導電型の不純物を含有する第1及び第2の半導体層109、113と、第1及び第2の半導体層109、113の間に形成され、第1及び第2の半導体層109、113の禁制帯幅よりも禁制帯幅が広く、かつ、不純物濃度が1×1017cm−3以下である第3の半導体層111と、を備えるものである。

(もっと読む)

半導体装置の動作方法

【課題】ワイドギャップ半導体素子を動作させる半導体装置の動作方法であって、積層欠陥の発生による素子破壊を招くことなく簡単に実現できるものを提供すること。

【解決手段】この発明の半導体装置の動作方法では、ワイドギャップ半導体素子の通電開始時に通電電流Iを或る電流上昇率でゼロから定格電流Inまで上昇させる。ワイドギャップ半導体素子内の積層欠陥の発生によるワイドギャップ半導体素子の破壊を防止するように、通電電流Iをゼロから定格電流Inまで上昇させるソフトスタート時間tsを0.5秒から10秒までの範囲内に設定する。

(もっと読む)

電源回路及び光受信回路

【課題】光信号により起動制御が可能な電源回路及び光受信回路を提供する。

【解決手段】半導体基板の上に設けられ、光信号を電気信号に変換する起動回路と、前記半導体基板の上に設けられ、電源投入時に非起動状態であるバイアス回路と、を備え、前記起動回路は、p型半導体領域と、前記p型半導体領域と接して設けられたn型半導体領域と、を有し、前記p型半導体領域は、前記バイアス回路と電気的に接続され、前記n型半導体領域は、前記バイアス回路の電源と電気的に接続され、前記バイアス回路は、前記起動回路を流れる電流により起動状態となることを特徴とする電源回路が提供される。

(もっと読む)

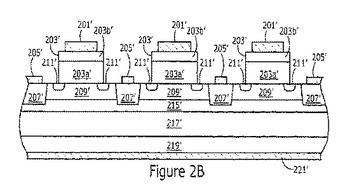

静電気放電シリコン制御整流器構造のための設計構造体及び方法

【課題】 静電気放電(ESD)シリコン制御整流器(SCR)構造体のための設計構造体及び方法を提供すること。

【解決手段】 設計構造体は、設計、製造、又は設計の試験のために機械可読媒体内で具現化される。設計構造体は、基板内に形成され第1及び第2のシリコン制御整流器(SCR)を含む。さらに、第1及び第2のSCRは各々、第1及び第2のSCR間で共有される少なくとも1つの構成要素を含む。

(もっと読む)

トランジスタ素子及びその製造方法並びに発光素子及びディスプレイ

【課題】エミッタ電極−コレクタ電極間において、低電圧で大電流変調を可能とするトランジスタ素子を提供する。また、そうしたトランジスタ素子の製造方法、また、そのトランジスタ素子有する発光素子及びディスプレイを提供する。

【解決手段】エミッタ電極3とコレクタ電極2との間に、半導体層5(5A,5B)とシート状のベース電極4が設けられているトランジスタ素子により、上記課題を解決する。半導体層5は、エミッタ電極3とベース電極4との間及びコレクタ電極2とベース電極4との間に設けられて、それぞれ第2半導体層5B及び第1半導体層5Aを構成し、さらに、ベース電極の厚さが80nm以下であることが好ましい。また、少なくともエミッタ電極とベース電極との間又はコレクタ電極とベース電極との間には、暗電流抑制層が設けられていてもよい。

(もっと読む)

電流シフト領域を有する半導体デバイスおよび関連方法

半導体デバイスは、第1の伝導形を有する半導体バッファ層と、バッファ層の表面上にあって第1の伝導形を有する半導体メサとを含む。さらに第2の伝導形を有する電流シフト領域が半導体メサと半導体バッファ層との間の隅に隣接して設けられ、第1と第2の伝導形が互いに異なる伝導形である。関連する方法も開示される。  (もっと読む)

(もっと読む)

トランジスタ型保護素子、半導体集積回路およびその製造方法

【課題】保護素子のターンオン電圧を決める制約を少なくする。

【解決手段】半導体基板1、Pウェル2、ゲート電極4、ソース領域5、ドレイン領域6および抵抗性降伏領域8を有する。抵抗性降伏領域8はドレイン領域6に接し、ゲート電極4直下のウェル部分と所定の距離だけ離れたN型半導体領域からなる。ドレイン領域6または抵抗性降伏領域8に接合降伏が発生するドレインバイアスの印加時に抵抗性降伏領域8に電気的中性領域(8i)が残るように、抵抗性降伏領域8の冶金学的接合形状と濃度プロファイルが決められている。

(もっと読む)

静電気保護回路

【課題】本発明は、静電気保護回路に関し、サイリスタの過剰なラッチアップ動作の継続を防止しつつ被保護回路を静電気による過電圧破壊から保護することにある。

【解決手段】サイリスタ構造に形成されたpnpバイポーラトランジスタ及びnpnバイポーラトランジスタを設ける。そして、pnpバイポーラトランジスタのベース端子を、被保護回路に接続する基準電源端子に接続させると共に、pnpバイポーラトランジスタのベース端子とnpnバイポーラトランジスタのコレクタ端子との間に、両端に印加される電圧が所定電圧以上である場合に導通し、一方、所定電圧未満である場合に遮断するツェナーダイオードを設ける。

(もっと読む)

静電気保護回路

【課題】本発明は、静電気保護回路に関し、静電気電流の高い放電能力を維持しつつ過剰なラッチアップ動作の継続を防止することにある。

【解決手段】サイリスタ構造に形成された第1接合型のバイポーラトランジスタ及び第2接合型のバイポーラトランジスタと、第1接合型のバイポーラトランジスタのコレクタ端子と第2接合型のバイポーラトランジスタのベース端子との間に介挿されたMOSトランジスタと、を設ける。そして、そのMOSトランジスタを、被保護回路へ印加される電圧が、被保護回路の通常動作時に生ずる電圧よりも高くかつ被保護回路が破壊される電圧の下限値よりも低い所定電圧以上である場合に導通させ、一方、被保護回路へ印加される電圧がその所定電圧未満である場合に遮断させる。

(もっと読む)

静電気保護素子

【課題】表示パネル駆動用の半導体集積装置に適した、保持電圧が高い静電保護素子を提供する。

【解決手段】静電保護素子は、P型半導体基板1の表面側に形成されたNウェル領域2と、Nウェル領域の上に形成された第1のP型高濃度不純物領域8と、P型半導体基板の表面上に形成されたN型高濃度不純物領域5と、Nウェル領域とP型半導体基板1との境界を跨いでNウェル領域と前記P型半導体基板との双方に接触して形成された第2のP型高濃度不純物領域6とを備えている。すなわち、第2のP型高濃度不純物領域6がP型半導体基板1と接触するため、P型半導体基板1におけるP型不純物の濃度が高くなり、従って静電気保護素子の保持電圧が高くなる。

(もっと読む)

静電気保護素子

【課題】特殊な工程や、保護抵抗の挿入なしに被保護回路を保護できる静電気保護素子を提供する。

【解決手段】P型の半導体基板1と、半導体基板1に形成された、N型の第1不純物層3を備える。第1不純物層3内には、ゲートとして動作するP型の第2不純物層5を備える。第2不純物層5には、カソードとして動作するN型の第3不純物層6を備える。また、第2不純物層5から一定距離離間した第1不純物層3内には、N型の第4不純物層4を備える。第4不純物層4内には、アノードとして動作するP型の第5不純物層8と、N型の第6不純物層9とを備える。そして、本静電気保護素子は、第4不純物層4の不純物濃度が第1不純物層3の不純物濃度よりも高く、かつ第4不純物層4の底部が第2不純物層5の底部より深くなっている。

(もっと読む)

発光素子チップ、露光装置および画像形成装置

【課題】本発明は、発光素子アレイの構造を利用して信号線の引き回しの複雑化を軽減した発光素子チップを提供する。

【解決手段】発光素子チップ51aは、GaAs系の半導体で構成され、基板200上に形成されたpnpn構造からなる、発光部120の発光サイリスタ401と、設定部130の転送サイリスタ402と、制御部140の論理演算素子403とを備え、基板200上にp型の第1半導体層201とn型の第2半導体層202と、p型の第3半導体層203と、n型の第4半導体層204とを積層し、その後、予め定められた箇所をエッチングして形成される。

(もっと読む)

ESD保護素子および該ESD保護素子を設けた半導体装置

【課題】 本発明の目的はESD保護素子の平面サイズの増大を図ることなく、良好なESD特性を得る。

【解決手段】 第1導電型の第1半導体領域1と、所定の間隔を有してそれぞれ設けられた第1電極11および第2電極12と、第1半導体領域の表面側に設けられた第2導電型の第2半導体領域2と、当該領域の表面側にそれぞれ設けられた第1導電型の第3半導体領域3および第4半導体領域4と、第3半導体領域内であって当該領域の表面側に設けられて、第1電極と電気的に接続された第2導電型の第5半導体領域5と、第4半導体領域内であって当該領域の表面側に設けられて、第2電極と電気的に接続された第2導電型の第6半導体領域6と、を備えており、第2半導体領域、前記第3半導体領域および前記第4半導体領域は、それぞれが浮遊電位に保たれていることを特徴とする。

(もっと読む)

保護回路

【課題】静電気印加時には、高速にトリガし、通常使用時には、ラッチアップが起きにくいサイリスタ型の保護回路を提供する。

【解決手段】第1の端子と第2の端子との間に、一端が第2の端子に接続された容量素子と、半導体基板上に設けられたサイリスタであって、上記第1の端子に接続されたアノードと、上記第2の端子に接続された第1カソードと、アノードと第1カソードとの間に配置され上記容量素子の他端に接続された第2カソードと、を備えたマルチカソードサイリスタと、を用いることにより、アノードと第2カソード間で開始したサイリスタ動作がアノードと第1カソード間のサイリスタ動作を誘起するようにした。

(もっと読む)

1 - 20 / 42

[ Back to top ]