Fターム[5F083AD16]の内容

Fターム[5F083AD16]に分類される特許

1 - 20 / 33

半導体装置

【課題】半導体層上での占有面積の増加を抑制しながらキャパシタ素子の容量を増大させることができる半導体装置を提供する。

【解決手段】この半導体装置は、素子分離溝2によって分離された複数の活性領域Aを有するn型半導体層3と、素子分離溝2の側壁2bを覆う側壁被覆部17を有する容量膜15と、容量膜15に積層された電極膜18とを含む。n型半導体層3、容量膜15および電極膜18によってキャパシタCが形成されている。

(もっと読む)

半導体装置及びその駆動方法

【課題】消費電力を低減することが可能な新たな構造の半導体装置及びその駆動方法を提供する。

【解決手段】メモリセルは、容量素子と、第1のトランジスタと、第1のトランジスタよりオフ電流の小さな第2のトランジスタとを有する。第1のトランジスタは、第2のトランジスタよりもスイッチング速度が速い。第1のトランジスタと第2のトランジスタと容量素子とは直列に電気的に接続されている。容量素子への電荷の蓄積、及び容量素子からの電荷の放出は、第1のトランジスタと第2のトランジスタの両方を介して行われる。こうして、半導体装置の消費電力を少なく、且つ情報の書き込み及び読み出し速度を高速化することができる。

(もっと読む)

半導体記憶装置

【課題】SOI構造のDRAMの提供

【解決手段】

半導体基板1上に複数層の絶縁膜(2、3、4、5)が選択的に設けられ、絶縁膜5上より、絶縁膜5が設けられていない領域上に延在して選択的に半導体層(8、9、10)が設けられ、半導体層の一部9の全周囲にゲート絶縁膜16を介し、絶縁膜4上に包囲構造のゲート電極17が設けられ、ゲート電極に自己整合し、直下に空孔7を有する半導体層の一部10にドレイン領域(14、15)が、半導体層の一部8にソース領域(12、13)が設けられた構造のMIS電界効果トランジスタと、ソース領域12の側面に一部を接し、絶縁膜(3、5)中にトレンチが設けられ、トレンチの側面に電荷蓄積電極19が設けられ、電荷蓄積電極の側面及び上部にキャパシタ絶縁膜20を介してセルプレート電極21が設けられた構造のトレンチ型キャパシタと、により構成されたDRAM。

(もっと読む)

半導体記憶装置

【課題】CMOSプロセスで、ダイナミック型半導体記憶装置を形成し、ロジックとの混載に適したダイナミック型半導体記憶装置を実現する。

【解決手段】メモリセル(MC)のワード線(WL)を形成する導電線(3)とメモリセルセルプレート電極(CP)を形成する導電線(5)とを、異なる配線層に形成する。対をなすビット線に並行してメモリセルを接続し、2つのメモリセルで1ビットのデータを記憶する。

(もっと読む)

半導体装置の製造方法

【課題】半導体装置の製造方法において、半導体装置の歩留まりを向上させること。

【解決手段】シリコン基板20に溝20aを形成する工程と、溝20aに充填材30を充填する工程と、溝20aに充填材30が充填された状態で、シリコン基板20に対してウエット処理を行う工程と、ウエット処理の後、充填材30を除去する工程と、充填材30を除去した後、溝20a内に、キャパシタ誘電体膜45aを介してキャパシタの対向電極50pを形成する工程とを有する半導体装置の製造方法による。

(もっと読む)

複合メモリ

【課題】 製造コストの上昇を招くことなくNANDフラッシュメモリにDRAMを混載することができ、且つチップ面積の増大を招くことなくシステム性能の向上をはかる。

【解決手段】 半導体基板10上に、NANDセルユニットからなる第1のメモリセルアレイとDRAMセルからなる第2のメモリセルアレイとを搭載した複合メモリであって、NANDセルユニットは、第1のゲート14と第2のゲート16を積層した2層ゲート構成の不揮発性メモリセル100と不揮発性メモリセル100の第1及び第2のゲート14,16間を接続した選択トランジスタ200で構成され、DRAMセルは、選択トランジスタ200と同じ構成のセルトランジスタ300と、不揮発性メモリセル100又は選択トランジスタ200と同じ構成のMOSキャパシタ400で構成されている。

(もっと読む)

半導体装置の製造方法

【課題】ストレージ拡散層を介したリーク電流の抑制が図られたメモリセルの作製に適した、半導体装置の製造方法を提供する。

【解決手段】半導体装置の製造方法は、第1導電型領域上に、ゲート絶縁膜とゲート電極の積層構造、及びキャパシタ絶縁膜とキャパシタ電極の積層構造を有する半導体基板を準備する工程と、ゲート電極とキャパシタ電極とを覆って半導体基板上に絶縁膜を形成する工程と、ゲート電極とキャパシタ電極との間の第2領域、及びゲート電極に対しキャパシタ電極と反対側の第3領域に、絶縁膜を通して第1導電型と反対の第2導電型の不純物を注入する工程と、絶縁膜をエッチングしてゲート電極側壁上にサイドウォールを残す工程と、第2領域上にマスク部材を形成する工程と、ゲート電極と、キャパシタ電極と、マスク部材と、ゲート電極側壁上のサイドウォールをマスクとし、第3領域に第2導電型不純物を注入する工程とを有する。

(もっと読む)

半導体装置とその製造方法

【課題】

ロジックプロセスと適合性が高く、ノイズに対して強い耐性を有するメモリ回路を含む半導体装置とその製造方法を提供する。

【解決手段】

半導体装置は、複数のメモリセルが第1および第2の方向に沿って行列状に配置されたメモリセルアレイ、および第1および第2のセンスアンプを含む複数のセンスアンプ、を形成した半導体基板を含み、メモリセルの各々は絶縁ゲート電極とその両側に形成されたビット線コンタクト領域と他のソース/ドレイン領域を備えたトランジスタと、他のソース/ドレイン領域に接続されたキャパシタとによって構成される。メモリセルアレイ上方に、第1の方向に沿って延在し、複数のビット線コンタクト了以金に接続され、第2の方向に並んで配置された複数のビット線を含む。第1のセンスアンプに接続される第1対のビット線は、第1配線層で形成され、第2のセンスアンプに接続される第2対のビット線は、第1の配線層と異層の第2配線層で形成される。

(もっと読む)

半導体装置及びその製造方法

【課題】電極と対向する半導体基板との間で容量を形成し、半導体基板に形成された溝内に電極が形成され、リーク電流の抑制が図られたキャパシタを含む半導体装置を提供する。

【解決手段】半導体装置は、溝101が形成された半導体基板1と、溝101内に形成されたキャパシタ電極8Cと、溝101の底上に形成され、半導体基板1とキャパシタ電極8Cとの間に介在する第1の絶縁膜5と、溝101の側壁上に形成され、半導体基板1とキャパシタ電極8Cとの間に介在する第2の絶縁膜6Caと、溝101の底で、キャパシタ電極8Cと第1の絶縁膜5との間に介在する第1の金属酸化物膜7Caとを有する。

(もっと読む)

半導体装置及びその製造方法

【課題】微細化した場合であっても電気的特性の良好なメモリセルを得ることができる半導体装置及びその製造方法を提供する。

【解決手段】半導体基板10上及びトレンチ12cの側壁に形成されたキャパシタ誘電体膜30aと、キャパシタ誘電体膜上に形成されたキャパシタ電極36aとを有するキャパシタ40と、キャパシタ40に接続されたメモリセルトランジスタ54と、メモリセルトランジスタとキャパシタとが形成されたメモリセル領域4における半導体基板に形成された第2導電型の第1のチャネルドープ層26aと、メモリセル領域における半導体基板内に形成され、第1のチャネルドープ層よりも浅い第2導電型の第2のチャネルドープ層27とを有している。

(もっと読む)

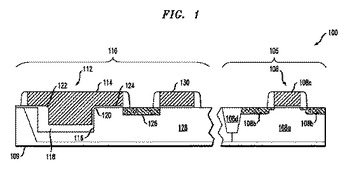

ランダム・アクセス・メモリ・デバイスのトレンチ・キャパシタ漏洩電流を低減する方法

本発明は、一態様では、半導体デバイスを製造する方法を提供する。この方法は、半導体基板(109)のダイナミック・ランダム・メモリ領域(DRAM)(110)内にトレンチ分離構造(118)を形成すること、ならびにトレンチ分離構造(118)の上に、トレンチ分離構造(118)の一部分を露出するようにエッチング・マスクをパターニングすることを含む。露出したトレンチ分離構造(118)の一部分を除去してその中に、半導体基板によって形成された第1の角部と、トレンチ分離構造によって形成された第2の角部とを含むゲート・トレンチ(116)を形成する。エッチング・マスクをDRAM領域(110)から除去し、ゲート・トレンチの少なくとも第1の角部に丸みをつけて、丸みをつけた角部(120)を形成する。この後に、ゲート・トレンチ(116)の側壁の上、第1の丸みをつけた角部(120)の上、およびゲート・トレンチ(116)に隣接する半導体基板(109)の上の酸化物層(124)の形成を続ける。トレンチ(116)をゲート材料で充填する。  (もっと読む)

(もっと読む)

タングステン材料の原子層堆積法

【課題】ALDプロセスを使用して、均一性が良好で、ほとんどまたは全く汚染がなく、かつ導電率が高いつまり抵抗率が低いタングステン含有材料を堆積するための改良されたプロセスを提供する。

【解決手段】一実施形態では、プロセスチャンバ内に基板を位置決めするステップであって、該基板がこの上に配置されている下地層を含有するステップと、該基板をタングステン前駆体および還元ガスに順次曝してALDプロセス時に該下地層上にタングステン核形成層を堆積するステップであって、該還元ガスが約40:1、100:1、500:1、800:1、1,000:1以上の水素/ハイドライド流量比を含有するステップと、該タングステン核形成層上にタングステンバルク層を堆積するステップとを含む、基板上にタングステン含有材料を形成するための方法が提供される。該還元ガスはジボラン、シランまたはジシランなどのハイドライド化合物を含有している。

(もっと読む)

半導体装置の製造方法

【課題】MONOS型不揮発性メモリの製造プロセスを大幅に変更することなく、1つの基板上に互いにメモリ機能の異なる複数種類のメモリを搭載する半導体装置を製造し、半導体装置の多機能化を実現することのできる技術を提供する。

【解決手段】第1導体膜によりMONOSセルの選択用nMISの選択ゲート電極4mと、DRAMセルの選択用nMISのゲート電極4dと、FLASHセルのメモリMISの浮遊ゲート電極4fとを形成し、第2導体膜によりMONOSセルのメモリ用nMISのメモリゲート電極MGと、DRAMセルの容量電極11dと、FLASHセルのメモリMISの制御ゲート電極11fとを形成し、絶縁膜10b、電荷蓄積層CSLおよび絶縁膜10tからなる積層膜によりMONOSセルの電荷保持用絶縁膜、DRAMセルの容量絶縁膜およびFLASHセルの層間絶縁膜を形成することにより、半導体基板1に、MONOSセル、DRAMセルおよびFLASHセルを搭載する半導体装置を製造する。

(もっと読む)

プログラム可能な感知検出器、ソフト・エラーを検出する方法及びDRAMアレイ(高速のDRAMソフト・エラー検出のためのプログラム可能な重イオン感知デバイス)

【課題】プログラム可能な感知検出器、ソフト・エラーを検出する方法及びDRAMアレイを提供する。

【解決手段】本発明の態様は、高速化されたDRAMソフト・エラー検出のためのプログラム可能な重イオン感知デバイスに関する。DRAMベースのアルファ・イオン粒子感知装置の設計は、高速化されたオン・チップSERテスト装置として使用されることが望ましい。多様な度合いのSER感度を達成するために、感知装置には、プログラム可能感知マージン、リフレッシュ率及び供給電圧が与えられる。更に、デュアル・モードのDRAMアレイが提案され、その結果、アレイの少なくとも一部が、ソフト・エラー検出(SED)モードの間、高エネルギー粒子の活動をモニタするために使用され得る。

(もっと読む)

3次元チャネル電界効果トランジスタを備えた集積回路およびその製造方法

【課題】3次元チャネル構造トランジスタのゲート長とゲート幅を拡大した集積回路及びその製造方法を提供する。

【解決手段】ソース領域161、ドレイン領域162、上記ソース領域と上記ドレイン領域との間に配置されるチャネル領域163、ゲート電極165と、上記チャネル領域と上記ゲート電極との間に配置されるゲート誘電体164と、上記ゲート電極と上記ソース領域の少なくとも一部との間に配置される第1絶縁体構造物146と、上記ゲート電極と上記ドレイン領域の少なくとも一部との間に配置される第2絶縁体構造物147とを含み、上記ゲート電極の下端部は、上記ソース領域および上記ドレイン領域の少なくとも1つの領域の下端部よりも下に形成され、上記第1絶縁体構造物および上記第2絶縁体構造物の少なくとも1つは、上記ゲート誘電体よりも大きな層厚を有し、上記第1絶縁体構造物および上記第2絶縁体構造物は、互いに非対称である。

(もっと読む)

半導体記憶装置及びその製造方法

【課題】半導体記憶装置においてキャパシタの蓄積容量の増加を図る。

【解決手段】半導体記憶装置は、トランジスタ14及びキャパシタ16を夫々有する複数のメモリセル12と、メモリセル間を素子分離する素子分離部22とを具備する。素子分離部22は、半導体基板2の第1表面内に形成された第1トレンチ6内に埋め込まれた素子分離絶縁膜22を含む。キャパシタ16は、第1トレンチ6に隣接して第1表面内に形成された第2トレンチ8内の側面及び底面上に形成されたキャパシタ絶縁膜34と、第2トレンチ8内でキャパシタ絶縁膜34上に埋め込まれた上側電極36と、上側電極36と対向するように半導体基板2内に形成された下側電極32とを含む。トランジスタ14は、第2トレンチ8に隣接して第1表面内に形成され且つ一方が下側電極32に電気的に接続された一対のソース/ドレイン層42と、一対のソース/ドレイン層42間でゲート絶縁膜44を介して半導体基板2上に配設されたゲート電極46とを含む。

(もっと読む)

半導体装置およびその製造方法

【課題】形成面積の縮小化とキャパシタの容量の確保との両立を可能にする半導体装置を提供する。

【解決手段】DRAMセルは、シリコン基板1の上部に形成された分離トレンチ40により規定される活性領域7に形成され、当該活性領域7の端部にキャパシタC1,C2が形成される。このキャパシタC1,C2が形成される活性領域7の端部の表面には、選択エピタキシャル成長法によりエピタキシャル層25が形成されており、他の部分よりも幅が広くなっている。当該キャパシタC1,C2は、その幅広部の形成された不純物拡散層24を第1電極とし、その上に誘電体層21を介して形成された電極22を第2電極とする。

(もっと読む)

半導体記憶装置およびその製造方法

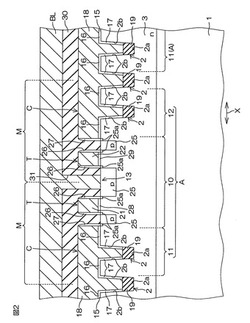

【課題】メモリセルの高集積化およびメモリセルのキャパシタの容量増大を図る。

【解決手段】半導体基板の活性領域40を規定する分離トレンチ2内にはフィールドシールド電極であるN型導電性膜4nが形成される。各活性領域40には、その両端に形成されたキャパシタと、ゲート電極12を有する2つのトランジスタとから成る2つのDRAMセルが形成される。活性領域40の両端のキャパシタは、分離トレンチ2の内壁(活性領域40の側壁)の不純物拡散層をストレージ電極とし、分離トレンチ2内のN型導電性膜4nをセルプレート電極とする。活性領域40の両端のキャパシタのセルプレート電極であるN型導電性膜4nは、互いに分離トレンチ2内で繋がっている。

(もっと読む)

スケーリング可能な組み込みDRAMアレイ

第1のプロセスから第2のプロセスに組み込みDRAMアレイをスケーリングするための方法及び装置であって、スケーリングは一定のスケールファクタでフィーチャの直線寸法を縮小することを含む。第1のプロセスから第2のプロセスへと、DRAMセルキャパシタの配置面積はスケールファクタの2乗で減少し、セル容量はスケールファクタで減少する。ロジックトランジスタに供給するために利用される電圧は、第1のプロセスから第2のプロセスにスケールダウンされる。しかしながら、センスアンプに供給するために利用される電圧はどちらのプロセスも変わらない。従って、第2のプロセスの組み込みDRAMアレイにおいては、センスアンプはロジックトランジスタより大きな電圧を供給される。これにより、一つのプロセス世代から次の世代にわたってDRAMセルの検出電圧を維持しながら、メモリサイズをプロセスのスケールファクタの2乗でスケーリングすることが可能になる。  (もっと読む)

(もっと読む)

半導体記憶装置

【課題】形成過程における位置合わせずれが生じた場合であっても、電気的特性のばらつきの発生を抑制できる相補型メモリセルを提供する。

【解決手段】相補型メモリセルは、2つのメモリユニットMUから成る。メモリユニットMUの各々は、半導体基板における活性領域3と上部電極22とが重なる部分にメモリキャパシタを備える。相補型メモリセルが備える2つのメモリキャパシタのうち一方の上部電極22は、活性領域3における所定の第1方向側端部を覆っており、他方の上部電極22は、活性領域3における第1方向とは逆の第2方向側端部を覆う。

(もっと読む)

1 - 20 / 33

[ Back to top ]