Fターム[5F083BS02]の内容

Fターム[5F083BS02]の下位に属するFターム

ゲート構造 (68)

ソース/ドレイン構造 (193)

Fターム[5F083BS02]に分類される特許

141 - 141 / 141

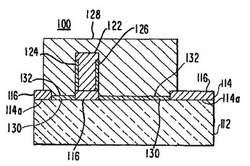

ノード・キャパシタンスを増加した半導体メモリ・デバイス

【課題】 ノード・キャパシタンスを増加した半導体メモリ・デバイスを提供することにある。

【解決手段】 集積回路半導体メモリ・デバイス(100)は、ゲートから基板へのキャパシタンスを増加し、それにより、ソフト・エラー率を低減するために、ストレージ・トランジスタのゲートの下に基板(112)の一部分(130)には存在しないBOX層として特徴付けられた第1の誘電体層(116)を有する。第1の誘電体層とは異なる特性を有する第2の誘電体層(132)は、基板のその部分(130)を少なくとも部分的に覆う。このデバイスは、フィン(122)と、ゲートとフィンとの間のゲート誘電体層(124、126)とを含むFinFETデバイスにすることができ、第2の誘電体層はゲート誘電体層より漏れが少ない。

(もっと読む)

141 - 141 / 141

[ Back to top ]