Fターム[5F083BS03]の内容

Fターム[5F083BS03]に分類される特許

1 - 20 / 68

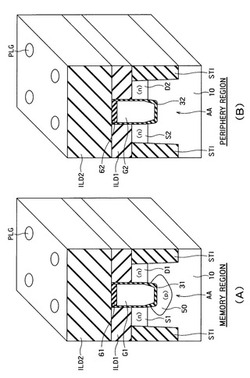

半導体装置とその製造方法

【課題】製造プロセスが容易であり、かつ、Fin型FETおよび従来型トランジスタを混載した半導体記憶装置を提供することである。

【解決手段】半導体記憶装置は第1の領域および第2の領域を備える。メモリ部のトランジスタは第1導電型のFin型半導体層を備える。第1導電型の第1のソース層および第1のドレイン層はFin型半導体層の両端に設けられる。第1のゲート電極はFin型半導体層の両側面に設けられる。第2導電型のパンチスルーストッパ層は第1のゲート電極およびFin型半導体層の下に設けられている。パンチスルーストッパ層の不純物濃度は第1のソース層および第1のドレイン層の下の不純物濃度よりも高い。周辺回路部のトランジスタは、第2のゲートトレンチを備える。第1導電型の第2のソース層および第1導電型の第2のドレイン層は、第2のゲートトレンチの両側に設けられる。第2のゲート電極は、第2のゲートトレンチ内に充填される。

(もっと読む)

二重フローティングゲート構造を有するトランジスタを備えた不揮発性メモリ

【課題】CMOS製造プロセスに用いることのできる材料を用いかつノイズマージンの広い不揮発性メモリを提供する。

【解決手段】本実施形態の不揮発性メモリによれば、第1および第2のPチャネルトランジスタはそれぞれ第1の半導体領域上に設けられ、第1の半導体領域上に、第1の絶縁膜と、第1のフローティングゲート、第2の絶縁膜、第2のフローティングゲート、第3の絶縁膜、および第1の制御ゲートが、この順序で積層された構造を有し、前記第1および第2のNチャネルトランジスタはそれぞれ第2の半導体領域上に設けられ、前記第2の半導体領域上に、第4の絶縁膜、第3のフローティングゲート、第5の絶縁膜、第4のフローティングゲート、第6の絶縁膜、および第2の制御ゲートがこの順序で積層された積層構造を有している。

(もっと読む)

半導体装置

【課題】高集積なCMOS SRAMを提供する。

【解決手段】第1の第1導電型半導体137と、第1の第1導電型半導体とは極性が異なる第1の第2導電型半導体104と、第1の第1導電型半導体と第1の第2導電型半導体との間に配置される第1の絶縁物112が一体となり基板に対して垂直に延びる1本の第1の柱と、

第1の第1導電型半導体の上に配置される第1の第2導電型高濃度半導体182と、第1の第1導電型半導体の下に配置される第2の第2導電型高濃度半導体141と、第1の第2導電型半導体の上に配置される第1の第1導電型高濃度半導体186と、第1の第2導電型半導体の下に配置される第2の第1導電型高濃度半導体143と、第1の柱を取り囲む第1のゲート絶縁物176と、第1のゲート絶縁物を取り囲む第1のゲート導電体167と、を有するインバータ501を用いてSRAMを構成する。

(もっと読む)

バッファ付きフィンFETデバイス

【課題】フィンFETデバイスのロバストネスを向上させる。

【解決手段】トランジスタデバイスであって、半導体基板と、半導体基板に形成されたバッファ付き垂直フィン状構造であって、垂直フィン状構造は、ドレーン領域とソース領域512との間にチャンネル領域514を含む上位の半導体層と、上位の半導体層の下のバッファ領域304であって、第1のドーピング極性を有するバッファ領域と、第1のドーピング極性と反対である第2のドーピング極性を有するウェル領域302の少なくとも一部分と、バッファ領域とウェル領域との間の少なくとも1つのp−n接合であって、該垂直フィン状構造の水平断面を少なくとも部分的にカバーする少なくとも1つのp−n接合とを含むバッファ付き垂直フィン状構造と、上位の半導体層のチャンネル領域をおおい形成されたゲートスタックとを備えている。

(もっと読む)

半導体装置

【課題】短チャネル効果を抑制させつつ微細化を行い、低消費電力化した半導体装置を提供する。

【解決手段】重畳する第1のトランジスタおよび第2のトランジスタからなる第1のインバータと、重畳する第3のトランジスタおよび第4のトランジスタからなる第2のインバータと、第1の選択トランジスタと、第2の選択トランジスタと、を有し、第1のインバータの出力端子、第2のインバータの入力端子および第1の選択トランジスタのソースおよびドレインの一方が接続され、第2のインバータの出力端子、第1のインバータの入力端子および第2の選択トランジスタのソースおよびドレインの一方が接続されることによって、微細化したSRAM回路を形成する。

(もっと読む)

半導体装置およびその製造方法

【課題】ゲート電極の一部にメタルゲート電極を有するMISEFTにおいて、メタルゲート電極を構成するグレインの配向性のばらつきに起因するMISFETのしきい値電圧のばらつきを小さくする。

【解決手段】メタルゲート電極4a、4bに炭素(C)を導入することにより、メタルゲート電極4a、4b内のグレインの粒径が大きくなることを防ぎ、メタルゲート電極4a、4bの中に多数の小さいグレインを形成することにより、グレインの配向性を均一化し、ゲート電極の仕事関数のばらつきを低減する。

(もっと読む)

SRAM装置

【課題】低消費電力でより安定して動作することが可能なSRAM装置を提供する。

【解決手段】SRAM装置100は、非反転出力端子Qおよび反転出力端子/Qを有するフリップフロップ回路FFを備える。非反転出力端子と第1のビット線bitとの間に、非反転出力端子側から第1のビット線側への方向に電流が流れる第1のトンネルトランジスタT1を備える。非反転出力端子と第1のビット線との間で、第1のビット線側から非反転出力端子側への方向に電流が流れる第2のトンネルトランジスタT2を備える。反転出力端子と第2のビット線bitbとの間に、反転出力端子側から第2のビット線側への方向に電流が流れる第3のトンネルトランジスタt3を備える。反転出力端子と第2のビット線との間で、第2のビット線側から反転出力端子側への方向に電流が流れる第4のトンネルトランジスタt4を備える。

(もっと読む)

半導体装置

【課題】FETの駆動力性能や遮断性能などを向上できる半導体装置を提供する。

【解決手段】半導体装置は、半導体基板と、前記半導体基板上に形成され、オフ状態とオン状態とで閾値電圧を可変させるFETからなる半導体素子と、を備える。前記半導体素子は、前記半導体基板のチャネル形成箇所の上方に形成される絶縁膜と、前記絶縁膜の上方に配置されるゲート電極と、前記絶縁膜と前記ゲート電極との間に介挿され、前記チャネルとの間よりも、前記ゲート電極との間で、より多くの電子の授受を行なうチャージトラップ膜と、を有する。

(もっと読む)

二重ゲート電極構造を含む半導体装置及びその製造方法

【課題】漏洩電流発生を最小化すると同時にオン電流(On current)を増加させ得る二重ゲート電極構造を含む半導体装置及びその製造方法が提供される。

【解決手段】本発明による半導体装置は、基板に配置されるゲート電極と、前記ゲート電極の両端に各々隣接するように前記基板に配置される第1不純物注入領域及び第2不純物注入領域と、前記第1不純物注入領域と前記第2不純物注入領域との間に配置されるチャンネル領域を含み、前記ゲート電極は前記第1不純物注入領域に隣接する第1サブゲート電極と前記第2不純物注入領域に隣接する第2サブゲート電極と、を含み、前記第1サブゲート電極と前記第2サブゲート電極とは前記チャンネル領域の上に配置される。この半導体装置では1つのチャンネル領域が2つのサブゲートによって独立的に制御されて漏洩電流発生を最小化できる。

(もっと読む)

半導体装置および当該半導体装置の作製方法

【課題】電気的特性の安定した酸化物半導体膜を用いることにより、半導体装置に安定した電気的特性を付与し、信頼性の高い半導体装置を提供すること。また、結晶性の高い酸化物半導体膜を用いることにより、移動度の向上した半導体装置を提供すること。

【解決手段】表面粗さの低減された絶縁膜上に接して、結晶性を有する酸化物半導体膜を形成することにより、電気的特性の安定した酸化物半導体膜を形成することができる。これにより、半導体装置に安定した電気的特性を付与し、信頼性の高い半導体装置を提供することができる。さらに、移動度の向上した半導体装置を提供することができる。

(もっと読む)

半導体装置及びその作製方法

【課題】酸化物半導体層の側面からの酸素の脱離を防ぎ、酸化物半導体層中の欠陥(酸素欠損)が十分に少なく、ソースとドレインの間のリーク電流が抑制された半導体装置を提供する。

【解決手段】酸化物半導体膜に対して第1の加熱処理を施した後に該酸化物半導体膜を加工して酸化物半導体層を形成し、その直後に該酸化物半導体層の側壁を絶縁性酸化物で覆い、第2の加熱処理を施すことで、酸化物半導体層の側面が真空に曝されることを防ぎ、酸化物半導体層中の欠陥(酸素欠損)を少なくして半導体装置を作製する。該半導体装置はTGBC(Top Gate Bottom Contact)構造とする。

(もっと読む)

電界効果トランジスタを備える半導体素子及びその製造方法

【課題】電界効果トランジスタを備える半導体素子及びその製造方法を提供する。

【解決手段】半導体基板と、前記半導体基板上に形成され、第1活性領域の上面及び向き合う側面を経て伸張する第1ゲート電極を有する第1導電型の第1FET素子と、前記第1FET素子上に形成された層間絶縁膜と、前記層間絶縁膜上に形成され、第2活性領域の上面及び向き合う側面を経て伸張する第2ゲート電極を有する第2導電型の第2FET素子と、を備える。

(もっと読む)

半導体回路及びその駆動方法、並びに記憶装置、レジスタ回路、表示装置、及び電子機器

【課題】トランジスタのしきい値電圧を最適な値に保持可能な半導体回路を提供すること。またトランジスタのしきい値電圧を制御可能な半導体回路、及びその駆動方法を提供すること。また上記半導体回路を適用した記憶装置、表示装置、及び電子機器を提供すること。

【解決手段】被制御トランジスタのバックゲートに接続されるノードに、ダイオードと第1の容量素子を設け、トランジスタのしきい値電圧が最適になるように所望の電圧を印加可能で且つその電圧を保持することができる構成とし、さらにダイオードに並列に接続された第2の容量素子を設け、当該ノードの電圧を一時的に変化させられる構成とすればよい。

(もっと読む)

半導体装置およびその製造方法

【課題】高密度で素子特性に優れた、SRAMを備えた半導体装置を提供する。

【解決手段】一対の駆動トランジスタと一対の負荷トランジスタと一対のアクセストランジスタを備えたSRAMセル単位を有する半導体装置であって、前記トランジスタはそれぞれ、基体平面に対して上方に突起した半導体層と、この半導体層を跨ぐようにその上部から相対する両側面上に延在するゲート電極と、このゲート電極と前記半導体層の間に介在するゲート絶縁膜と、前記半導体層に設けられた一対のソース/ドレイン領域を有し、前記駆動トランジスタはそれぞれ、前記負荷トランジスタ及び前記アクセストランジスタの少なくとも一方の各トランジスタのチャネル幅より広いチャネル幅を有する半導体装置。

(もっと読む)

半導体装置

【課題】本発明は、SOIにおいて適したゲッタリング方法を適用して得られる半導体装置を提供する。

【解決手段】埋め込み酸化膜と、埋め込み酸化膜上に表面シリコン層を有するSOI構造を有する半導体装置において、埋め込み酸化膜上に、表面シリコン層を活性層として有するトランジスタと、素子分離絶縁膜を有し、素子分離絶縁膜上に容量が形成されており、素子分離絶縁膜に希ガス元素又は金属元素が含まれていることを特徴とする半導体装置とする。

(もっと読む)

半導体装置及びその製造方法

【課題】ゲート幅が互いに異なる第1,第2のMISトランジスタを備えた半導体装置において、第1,第2のMISトランジスタの閾値電圧を、所望の閾値電圧に制御する。

【解決手段】半導体装置は、第1,第2のMISトランジスタを備えた半導体装置である。第1のMISトランジスタは、第1の高誘電率絶縁膜15aを有する第1のゲート絶縁膜15Aと、第1のゲート電極20Aとを備えている。第2のMISトランジスタは、第2の高誘電率絶縁膜15bを有する第2のゲート絶縁膜15Bと、第2のゲート電極20Bとを備えている。第1,第2のゲート絶縁膜は、調整用金属を含む。第1のMISトランジスタの第1のゲート幅W1は、第2のMISトランジスタの第2のゲート幅W2よりも小さい。第1のゲート絶縁膜中における調整用金属の平均調整用金属濃度は、第2のゲート絶縁膜中における調整用金属の平均調整用金属濃度に比べて低い。

(もっと読む)

半導体装置

【課題】高集積なCMOS型SRAMを提供する。

【解決手段】第1の第1導電型半導体137と、第1の第1導電型半導体とは極性が異なる第1の第2導電型半導体104と、第1の第1導電型半導体137と第1の第2導電型半導体104との間に配置される第1の絶縁物112が一体となり基板に対して垂直に延びる1本の第1の柱と、第1の第1導電型半導体137の上下に配置された第1の第2導電型高濃度半導体182と、第2の第2導電型高濃度半導体141と、第1の第2導電型半導体104の上下に配置された第1の第1導電型高濃度半導体186と、第2の第1導電型高濃度半導体143と、第1の柱を取り囲む第1のゲート絶縁物176と、第1のゲート導電体167と、を有するインバータを用いてSRAMを構成する。

(もっと読む)

半導体装置およびそれを用いた半導体集積回路

【課題】バックゲートを有するMOSを、回路の動作特性に応じて使い分け、幅広い温度範囲にて高速かつ低電力なLSIを実現する。

【解決手段】薄膜埋め込み酸化膜層を持つFD−SOIを使用し、薄膜埋め込み酸化膜層の下層半導体領域をバックゲートとし、論理回路ブロックにおいてブロック中の負荷の軽い論理回路にはバックゲートの電圧をブロック活性化に合わせてブロック外から制御する。このバックゲート駆動信号を発生する回路、及び回路ブロック出力部など負荷の重い論理回路には、ゲートとバックゲートとを接続したトランジスタを用い、そのゲート入力信号でバックゲートを直接制御する。

(もっと読む)

半導体装置及びその製造方法

【課題】集積度が高くリソグラフィーコストが低いn型及びp型FETの積層構造を有した半導体装置を提供すること。

【解決手段】半導体装置100は、半導体基板1上にそれぞれ離隔しつつ列状に形成された第1グループの複数の柱状ゲート電極10と、前記半導体基板1上であって前記第1グループの隣接する柱状ゲート電極10間に形成された第1導電型の第1半導体層12と、前記第1半導体層の上であって前記第1グループの隣接する柱状ゲート電極間に形成された第1絶縁層20と、前記第1絶縁層20の上であって前記第1グループの隣接する柱状ゲート電極10間に形成された前記第1導電型と異なる第2導電型の第2半導体層13とを備え、前記第1半導体層12をチャネルとする前記第1導電型の第1MOSFETが形成され、前記第2半導体層13をチャネルとする前記第2導電型の第2MOSFETが形成されている。

(もっと読む)

信号処理回路、及び信号処理回路の駆動方法

【課題】複雑な作製工程を必要とせず、消費電力を抑えることができる記憶装置、当該記憶装置を用いた信号処理回路の提供を目的の一つとする。

【解決手段】インバータまたはクロックドインバータなどの、入力された信号の位相を反転させて出力する位相反転素子を用いた記憶素子内に、データを保持するための容量素子と、当該容量素子における電荷の蓄積及び放出を制御するスイッチング素子とを設ける。上記スイッチング素子には、酸化物半導体をチャネル形成領域に含むトランジスタを用いる。そして、上記記憶素子を、信号処理回路が有する、レジスタやキャッシュメモリなどの記憶装置に用いる。

(もっと読む)

1 - 20 / 68

[ Back to top ]