Fターム[5F083BS02]の内容

Fターム[5F083BS02]の下位に属するFターム

ゲート構造 (68)

ソース/ドレイン構造 (193)

Fターム[5F083BS02]に分類される特許

41 - 60 / 141

半導体記憶装置

【課題】縦型トランジスタSGTで構成されたE/R型4T−SRAMにおいて、小さいSRAMセル面積を実現する。

【解決手段】4個のMOSトランジスタ及び2個の負荷抵抗素子を用いて構成されたスタティック型メモリセルにおいて、前記メモリセルを構成するMOSトランジスタは、基板上に形成された拡散層上に形成され、前記拡散層は記憶ノードであり、前記MOSトランジスタのドレイン、ゲート、ソースが基板に対して垂直方向に配置され、ゲートが柱状半導体層を取り囲む構造を有し、負荷抵抗素子はコンタクトプラグ形状に形成される小さい面積のSRAMセルを実現する。

(もっと読む)

半導体装置

【課題】絶縁層上の半導体層に形成されたトランジスターの閾値電圧のバラツキを低減できるようにした半導体装置を提供する。

【解決手段】絶縁層上に半導体層が形成された基板と、前記半導体層に形成されたトランジスターと、を備え、前記トランジスターは、前記半導体層上にゲート絶縁膜を介して形成されたゲート電極と、前記ゲート電極の両側下の前記半導体層に形成されたソース又はドレインと、前記ゲート電極直下の前記半導体層において前記トランジスターのゲート幅方向に沿って電流を流すための入力側端子及び出力側端子と、を有する。

(もっと読む)

半導体記憶装置

【課題】縦型トランジスタSGTで構成されたLoadless4T−SRAMにおいて、小さいSRAMセル面積と安定した動作マージンを実現する。

【解決手段】4個のMOSトランジスタを用いて構成されたスタティック型メモリセルにおいて、メモリセルを構成するトランジスタは、基板上に形成され、ドレイン、ゲート、ソースが垂直方向に配置され、ゲートが柱状半導体層を取り囲む構造を有し、前記平面状シリコン層は第1の導電型を持つ第1の活性領域と第2の導電型を持つ第2の活性領域からなり、それらが平面状シリコン層表面に形成されたシリサイド層を通して互いに接続されることにより小さい面積のSRAMセルを実現する。また、基板上に配置される第1のウェルと同一の導電型を持つドレイン拡散層のそれぞれを第1のウェルと反対の導電型を持ち、第1のウェルより浅い第2のウェル及び第3のウェルを形成することにより、基板へのリークを抑制する。

(もっと読む)

半導体装置の製造方法及び半導体装置

【課題】半導体装置が備えるnMOSトランジスタ及びpMOSトランジスタの形成面積を縮小する。

【解決手段】半導体装置の製造方法は、基板上に環状の突起部を形成する工程と、環状の突起部に第1のn型チャネル領域を形成する工程と、環状の突起部に第1のp型チャネル領域を形成する工程と、環状の突起部に形成された第1のn型チャネル領域及び第1のp型チャネル領域を跨ぐ第1のゲート電極を形成することにより、第1のnMOSトランジスタ及び第1のpMOSトランジスタを形成する工程と、を備える。

(もっと読む)

半導体装置、電気光学装置、電子機器

【課題】ある応力がかかっても回路全体としての動作特性が変化しない薄膜の半導体素子を実現し、これによって、動作マージンが広く大型化が容易なフレキシブルな半導体装置、電気光学装置、電子機器を提供する。

【解決手段】本発明の半導体装置は、基板100上に薄膜トランジスタ8を有し、この薄膜トランジスタ8は、基板100の湾曲に対してチャネル内のキャリアの移動度が相補的に変化する第1のチャネル領域1cおよび第2のチャネル領域1cを有している。

(もっと読む)

SOI構造シングルイベント耐性のNAND素子、及びNOR素子

【課題】高いシングルイベント耐性を有するNAND素子、NOR素子を提供する。

【解決手段】チャネルが並列に接続された第1のpチャネルMOSトランジスタ及び第2のpチャネルMOSトランジスタと、チャネルが直列に接続された第1のnチャネルMOSトランジスタ及び第2のnチャネルMOSトランジスタと、が第1の電圧源側に接続されたノードから第2の電圧源側に接続されたノードに向かって直列にSOI構造の基板上で接続され、それらのトランジスタのそれぞれに対して、それとゲート同士が相互に接続された同じ導電型のチャネルのMOSトランジスタがチャネルが直列に更に接続された二重化構造を有する。

(もっと読む)

半導体記憶装置

【課題】縦型トランジスタSGTで構成されたCMOS型6T−SRAMにおいて、小さいSRAMセル面積と安定した動作マージンを実現する。

【解決手段】6個のMOSトランジスタを用いて構成されたスタティック型メモリセルにおいて、前記メモリセルを構成するMOSトランジスタは、基板上に形成され、ドレイン、ゲート、ソースが垂直方向に配置され、ゲートが柱状半導体層を取り囲む構造を有し、前記基板は第1の導電型を持つ第1の活性領域と第2の導電型を持つ第2の活性領域からなり、それらが基板表面に形成されたシリサイド層を通して互いに接続されることにより小さい面積のSRAMセルを実現する。また、基板上に配置される第1のウェルと同一の導電型を持つドレイン拡散層のそれぞれを第1のウェルと反対の導電型を持ち、第1のウェルより浅い第2のウェル及び第3のウェルで囲むことにより、基板へのリークを抑制する。

(もっと読む)

半導体装置の作製方法

【課題】半導体装置の作製方法において、不純物元素を選択的に偏析させる方法を提供する。また、ディープサブミクロン領域の微細素子を形成することを可能とする。

【解決手段】シリコン基板上に形成された酸化珪素膜と、酸化珪素膜上に形成された単結晶シリコン層を有する半導体装置の作製方法であって、単結晶シリコン層に不純物元素を注入し、単結晶シリコン層に電気的に不活性な元素を注入し、単結晶シリコン層を熱酸化し、不活性な元素を注入した領域に選択的に酸化領域を形成し、酸化領域に不純物元素を偏析させる半導体装置の作製方法により、課題を解決する。

(もっと読む)

半導体装置及びその製造方法

【課題】読み出しマージンの大きなSRAMセルを提供する。

【解決手段】第1インバータ回路と、出力ノードが前記第1インバータ回路の入力ノードに接続され、入力ノードが前記第1インバータ回路の出力ノードに接続された、第2インバータ回路と、ソース及びドレインの一方が前記第1インバータ回路の出力ノードに接続され、他方がビット線に接続された、第1アクセストランジスタとを具備する。前記第1インバータ回路は、第1トランジスタを含む。前記第1アクセストランジスタ及び前記第1トランジスタのそれぞれは、基板上に形成され、前記基板面に対して垂直に延びる半導体柱と、前記半導体柱を前記基板面に平行な方向で取り囲むように形成され、前記半導体柱にチャネル領域を形成させる、ゲート電極と、前記半導体柱の下端部又は上端部にそれぞれ接続されるソース及びドレインとを備える。前記第1トランジスタの電流駆動力は、前記第1アクセストランジスタのそれよりも高い。

(もっと読む)

スタティックランダムアクセスメモリ(SRAM)セルとその製造方法

【課題】スタティックランダムアクセスメモリ(SRAM)セルとその製造方法を提供する。

【解決手段】スタティックランダムアクセスメモリ(SRAM)セルの複数のトランジスタのアクティブ領域の縦軸は全て平行である。第一線形イントラセル接続は、第一プルダウントランジスタPD−1、第一プルアップトランジスタPU−1、及び、第一パスゲートトランジスタPG−1の各アクティブ領域を、第二プルダウントランジスタPD−2のゲート電極118と第二プルアップトランジスタPU−2のゲート電極116に電気的に結合する。第二線形イントラセル接続は、第二プルダウントランジスタPD−2、第二プルアップトランジスタPU−2、及び、第二パスゲートトランジスタPG−2の各アクティブ領域を、第一プルダウントランジスタPD−1のゲート電極112と第一プルアップトランジスタPU−1のゲート電極110に電気的に結合する。

(もっと読む)

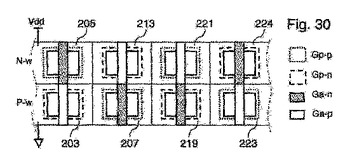

明白に異なる閾値電圧を有するトランジスタを持つSOIから製造する集積回路

本発明は、埋め込まれた絶縁材料面によって半導体基板層から隔てられた活性半導体層を含む集積回路に関する。この集積回路は、同じ型の第1および第2のトランジスタ(205、213)と、第1および第2のトランジスタの真下に配置された第1および第2の接地面とを有し、第1のトランジスタの接地面のドーピングは、第1のトランジスタのソースのドーピングと反対のドーピングであり、第1の閾値電圧を有する。第2のトランジスタの接地面のドーピングは、第2のトランジスタのソースのドーピングと同一のドーピングであり、第2の閾値電圧を有する。第1の閾値電圧は、第1のトランジスタのソースと接地面との間に印加される電位差に依存し、第2の閾値電圧は、第2のトランジスタのソースと接地面との間に印加される電位差に依存する。  (もっと読む)

(もっと読む)

非プレーナ型トランジスタを用いた半導体装置および製造方法

【課題】より速い駆動電流およびより小さな短チャネル効果を備え、微細化されたスタティック・ランダム・アクセス・メモリ・セルを提供する。

【解決手段】スタティック・ランダム・アクセス・メモリ・セル300は、半導体基板上の1つ以上のフィンを備える2つの非プレーナ型パスゲート・トランジスタを備える。2つの非プレーナ型プルアップ・トランジスタは、半導体基板上の1つ以上のフィンを備える。2つの非プレーナ型プルダウン・トランジスタは、半導体基板上の1つ以上のフィンを備える。半導体基板上の2つのアシスト・バー314、316は、非プレーナ型プルアップ・トランジスタのフィンの一部と非プレーナ型プルダウン・トランジスタのフィンの一部とを電気的に接続する。

(もっと読む)

重イオン・アップセット硬化浮遊ボディSRAMセル

【課題】ソフトエラーに耐えるSOICMOSSRAMを提供する。

【解決手段】シリコン−オン−絶縁物MOSFETトランジスタを有するCMOSメモリ素子。トランジスタのボディが電源に接続されておらず、その代わりに電気的浮遊を許容するように、MOSFETトランジスタの少なくとも一つが構成されている。重イオン放射によって生じるエラーに対する増加した免疫を備えた開示されたメモリ素子の実施態様。

(もっと読む)

半導体装置及びその製造方法

【課題】容易に製造することができ、トランジスタの性能を向上させることができる半導体装置及びその製造方法を提供する。

【解決手段】半導体基板1上にゲート絶縁膜2及びゲート電極3が形成されている。半導体基板1の表面の、平面視でゲート電極3を挟む位置に2個の不純物拡散層4が形成されている。2個の不純物拡散層4の表面に、ゲート絶縁膜2と半導体基板1との界面より低くなった掘り込み部6が設けられている。更に、半導体基板1のゲート絶縁膜2下の領域(チャネル)に応力を付加する応力付加膜が、少なくとも掘り込み部6内に位置している。

(もっと読む)

同一の能動領域内に形成されるトランジスタにおいて能動領域内に局所的に埋め込み歪誘起半導体材質を設けることによる駆動電流調節

【解決手段】

共通の能動領域内に少なくとも1つの埋め込み半導体合金を設けることによって得られる異なる歪レベルに基いて、その能動領域内に形成されるプルダウントランジスタ及びパストランジスタの駆動電流能力を調節することができ、それにより能動領域の単純化された全体的な幾何学的構造を提供することができる。従って、能動領域の単純化された構造を伴う最小のチャネル長に基きスタティックRAMセルを形成することができ、プルダウン及びパストランジスタに対する駆動電流の比を調節するためにトランジスタ幅の明白な変化が従来的に用いられている洗練されたデバイスで観察され得るような顕著な歩留まり低下を回避することができる。

(もっと読む)

半導体装置

【課題】 動作マージンを確保しつつ、微細化を可能とするSRAMセルを提供する。

【解決手段】

SRAMセルが、それぞれ、NMOSドライバとPMOSロードとが接続された第1、第2のインバータを含み、それぞれのインバータの内部ノードが他方のインバータの入力に接続されたフリップフロップ回路と、第1、第2のビット線と、第1、第2のインバータの内部ノードと第1、第2のビット線との間に接続された第1、第2のNMOSトランスファトランジスタであって、それぞれ、絶縁ゲート電極構造の両側に形成された第1、第2のn型ソース/ドレイン領域と、を含み、2つの第1のn型ソース/ドレイン領域が第1、第2のインバータの内部ノードに接続され、2つの第2のn型ソース/ドレイン領域が第1、第2のビット線に接続された第1、第2のNMOSトランスファトランジスタと、第1のn型ソース/ドレイン領域を覆って形成された圧縮応力膜と、第2のn型ソース/ドレイン領域を覆って形成された引張応力膜と、を有する。

(もっと読む)

半導体記憶装置

【課題】小型で動作信頼性の高い半導体記憶装置を提供することを目的とする。

【解決手段】第1、第2のインバータをクロスカップル接続させて形成されるインバータ対と、フロントゲートとバックゲートを有し前記バックゲートが前記第1のインバータの出力端子と前記第2のインバータの入力端子が接続する第1のノードに接続される第1のトランスファートランジスタと、前記フロントゲートと前記バックゲートを有し前記バックゲートが前記第2のインバータの出力端子と前記第1のインバータの入力端子が接続する第2のノードに接続される第2のトランスファートランジスタと、前記第2のノードにゲートが接続されるドライバトランジスタと、前記フロントゲートと前記バックゲートを有し前記バックゲートが前記第2のノードに接続され、電流経路の一端を前記ドライバトランジスタの電流経路一端に接続される読み出しトランジスタとを備える。

(もっと読む)

半導体記憶装置

【課題】本発明は、たとえばメモリセルの数が増大し、ワード線の長さが長くなったとしても、動作速度の高速化を図ることができる、半導体記憶装置を提供することを目的とする。

【解決手段】本発明に係る半導体記憶装置は、SRAMセル101とワード線ドライバー102とを備えている。さらに、SRAMセル101において、第一のコンタクト45,46を介して、アクセストランジスタQ5,Q6の第一のボディー領域およびドライバートランジスタの第二のボディー領域と、アクセストランジスタQ5,Q6のゲート電極とを電気的に接続する。さらに、第二のコンタクト148,180を介して、PMOSトランジスタQ51の第三のボディー領域と、PMOSトランジスタQ51のゲート電極とを電気的に接続する。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】新たなレイアウトパターンを作成せずにNMOSの駆動力を向上することができる半導体装置及び半導体装置の製造方法を提供する。

【解決手段】本発明の一態様に係る半導体装置1は、半導体基板100と、第1の導電型の第1の半導体素子が設けられる半導体基板100に形成される第1の半導体素子領域と、第2の導電型の第2の半導体素子が設けられる半導体基板100に形成される第2の半導体素子領域と、第1の半導体素子領域と第2の半導体素子領域とを分離する素子分離領域120とを備え、第1の半導体素子領域は、第1の半導体素子領域に隣接する素子分離領域120より高い位置に形成され、素子分離領域120の表面からの第1の半導体素子領域の表面までの距離が、第1の半導体素子領域の上面視における幅以下である。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】微細で精度が高く、歩留まりが向上した半導体装置を提供する。

【解決手段】半導体装置は、第1トランジスタ2と第2トランジスタ5とを具備する。第1トランジスタ2は、半導体基板100上に第1ゲート絶縁膜51を介して形成された第1ゲート電極21と第1ソース・ドレイン領域31と第1共通ソース・ドレイン領域30とを備える。第2トランジスタ5は、半導体基板100上に第2ゲート絶縁膜51を介して形成された第2ゲート電極22と第2ソース・ドレイン領域31と第1共通ソース・ドレイン領域30とを備える。第1ゲート電極21及び第2ゲート電極22は、第1共通ソース・ドレイン領域30のコンタクトである第1ノード電極41の両側壁に設けられている。

(もっと読む)

41 - 60 / 141

[ Back to top ]