Fターム[5F083BS02]の内容

Fターム[5F083BS02]の下位に属するFターム

ゲート構造 (68)

ソース/ドレイン構造 (193)

Fターム[5F083BS02]に分類される特許

101 - 120 / 141

半導体集積回路及びその作製方法、並びに半導体集積回路を用いた半導体装置

【課題】半導体基板にスルーホールを形成する工程や、半導体基板を裏面から研磨する工程は、非常に長い時間を要し生産性を低下させる要因となる。また、半導体基板を積層する構造であるため、積層して形成された半導体集積回路は厚くなり機械的な柔軟性に劣っている。

【解決手段】複数の基板上に剥離層を形成し、剥離層上に半導体素子、および貫通配線のための開口部を形成する。そして、半導体素子を有する層を基板から剥離し、重ね合わせて積層し、開口部に導電性を有する層を形成して貫通配線を形成することによって半導体集積回路を作製する。

(もっと読む)

スタティック・ランダムアクセスメモリ・セル

スタティック・ランダム・アクセス・メモリ(SRAM)手段を得る。SRAM手段は、第1ノード(A)とビット線バーとの間を接続する、第1パスゲートFET(T6)を有する。第2パスゲートFET(T1)は、第2ノード(B)とビット線(BL)との間を接続する。第2ノード(B)は、第1パスゲートFET(T6)に接続し、第1パスゲートFET(T6)は、第2ノード(B)の電圧(VB)に基づいて切り替わる。第1ノード(A)は、第2パスゲートFET(T1)に接続する。第2パスゲートFET(T1)は、第1ノード(A)の電圧(VA)により切り替わる。  (もっと読む)

(もっと読む)

サラウンディングゲートを有するナノワイヤ・トランジスタ

本主題の態様のひとつは、トランジスタの形成方法に関する。本方法の或る実施形態では、結晶質基板上に、非晶質半導体材料でつくった柱をつくり、固相エピタキシー工程を施して、結晶質基板を結晶成長の種として使い、非晶質半導体材料を結晶化する。この柱の厚さは、リソグラフィ基準寸法以下となっている。トランジスタボディを、結晶化した半導体柱内の第一のソース/ドレイン領域と第二のソース/ドレイン領域の間につくる。サラウンディングゲート絶縁体を半導体柱の周りにつくってから、サラウンディングゲートを半導体柱の周りにそのサラウンディングゲート絶縁体を間に挟んでつくる。他の態様についても本明細書に開示してある。  (もっと読む)

(もっと読む)

半導体装置の製造方法

【課題】支持体領域の第1半導体層を十分にウエットエッチングできるようにした半導体装置の製造方法を提供する。

【解決手段】SBSI法を用いて半導体装置を製造する方法であって、支持体領域210は、第1支持体領域211と、第1支持体領域と直交する第2支持体領域212と、第1支持体領域211と第2支持体領域212との交差領域220から第1支持体領域211の長手方向に突出した第1突出領域213と、交差領域220から第2支持体領域212の長手方向に突出した第2突出領域214とを有し、支持体保持領域230は、第1突出領域213と平面視で重なり且つ交差領域220から離れた位置と、第2突出領域214と平面視で重なり且つ交差領域220から離れた位置とに設けられている。このような構成であれば、交差領域240の隅付近に隙間240が生じ、その隙間240にSiGe層の側面を露出する開口面を形成することができる。

(もっと読む)

半導体装置及びその製造方法

【課題】ボディコンタクト構造を採らなくても、パスゲートリークの発生を防止できるようにした半導体装置及びその製造方法を提供する。

【解決手段】複数のメモリセル50からなるSRAMを有する半導体装置であって、メモリセル50を構成するパスゲートトランジスタQ5,Q6は(シリコン基板に直接形成された)バルクトランジスタであり、それ以外のトランジスタQ1〜Q4は(シリコン基板に部分的に形成されたSOI構造のSi層に形成された)SOIトランジスタである。このような構成であれば、パスゲートトランジスタQ5,Q6の基板電位を例えばGNDに固定することができ、パスゲートトランジスタQ5,Q6のチャネル領域下部における電荷の蓄積を防止することができる。

(もっと読む)

半導体装置

【課題】リーク電流を効果的に抑制するための技術を提供する。

【解決手段】絶縁表面を有する基板上にPチャネル型TFTを有し、前記Pチャネル型TFTの活性層のゲイト電極と重なる領域に、P型を付与する不純物元素が添加された第1の領域を有し、前記Pチャネル型TFTの活性層は、前記第1の領域を囲むように設けられたN型の導電型の第2の領域を有する半導体装置を提供する。こうして、電流パスとなり易い箇所にエネルギー的に障壁の高い領域を形成してリーク電流の発生(ショートチャネルリーク)を防ぐことができる。

(もっと読む)

半導体装置

【課題】プレーナ型トランジスタとフィンの2つの側面にチャネルが形成されるフィン型トランジスタとフィンの2つの側面と上面の合計3面にチャネルが形成されるトライゲート型トランジスタを基板上に搭載した半導体装置の個々の半導体素子の特性を変化させて所望の特性をもつ半導体装置を提供することである。

【解決手段】半導体基板と、半導体基板内に形成された素子分離層と、半導体基板表面に対して略平行な方向に電流が流れるプレーナ型トランジスタからなるプレーナ型トランジスタ領域と、半導体基板表面に対して略垂直に形成されたフィンの側面上を半導体基板表面に対して略平行な方向に電流が流れるフィン型トランジスタからなるフィン型トランジスタ領域とを備え、素子分離層の高さは、プレーナ型トランジスタ領域の方がフィン型トランジスタ領域よりも大きく、かつ、フィン型トランジスタ領域は複数の素子分離層の高さを有するものとする。

(もっと読む)

半導体装置

【課題】バックゲート型のフィンFETを使いながらも十分なSNMを得ることのできるSRAMセルを有する半導体装置を提供する。

【解決手段】複数のフィンフィールドエフェクトトランジスタで構成され、前記複数のフィンフィールドエフェクトトランジスタの中の少なくとも1つの前記トランジスタが、第1ゲート電極と第2ゲート電極を持ち、前記第1ゲート電極の電位を制御してチャネルを形成し、前記第2ゲート電極の電位を制御してデータの書き込み時に閾値電圧を低下させるセパレートゲート型のダブルゲートフィールドエフェクトトランジスタであるSRAMセルを有する半導体装置による。

(もっと読む)

半導体装置及びその製造方法

【課題】従来の半導体装置は、微細な素子を形成する場合、微細なピッチを有するパターンのマスクを複数用い、それぞれのマスクに対して、高精度な位置合わせと高精度かつ高精細な露光とを行うため、製造コストが高く、製造工程に多くの時間を必要とする問題がある。

【解決手段】本発明にかかる半導体装置は、ソース、ドレイン、ゲートとからなる素子を有する半導体装置であって、素子は、基板上に互いに分離して形成され、それぞれがソース又はドレインとなる第1、第2の領域と、一部が第1、第2の領域の対向する面に挟まれ、基板に埋め込まれて形成されるゲート電極とを有し、ゲート電極はゲート幅方向に、第1、第2の領域のゲート幅方向の長さよりも長く、第1、第2の領域に挟まれない第3の領域を有するものである。

(もっと読む)

高密度集積回路の製造方法

【課題】FinFET素子などを含む高密度集積回路を製造するための方法を提供する。

【解決手段】回路パターン(100)を半導体基板(300)のデバイス層(320)に形成する方法は、回路パターン(100)を2つの直交するサブパターン(200,210)に分解することと、第1サブパターンのパターンを、デバイス層(320)の上に横たわるハードマスク層(330,500)に転写することと、他方のサブパターンのパターンを、パターン化したハードマスク層(330,500)の上に横たわる感光層(350)に転写することと、パターン化したハードマスク層(330,500)およびパターン化した感光層(350)をマスクとして用いてデバイス層(320)のパターニングを行うことと、パターン化したハードマスク層(330,500)およびパターン化した感光層(350)を除去することを含む。

(もっと読む)

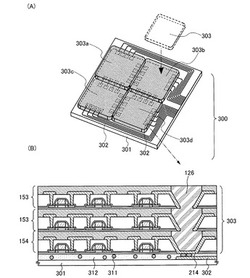

積層メモリセル

【課題】高集積SRAMに好適な積層メモリセルを提供する。

【解決手段】高集積SRAMに好適な積層メモリセルにおいて、第1層に形成された第1,2プルダウントランジスタと、前記第1層の上部に位置した第2層に形成され、前記第1,2プルダウントランジスタとそれぞれ連結されてインバータラッチを形成する第1,2プルアップトランジスタと、前記第2プルダウントランジスタのゲートとビットラインとの間に接続され、前記第1層または第2層の上部に位置した第3層に形成されるパストランジスタと、を備える。

(もっと読む)

半導体集積回路装置

【課題】本発明の課題は、待機時にある電位に固定する必要がある回路を駆動する回路のリーク電流低減を実現する技術を提供することにある。

【解決手段】ゲート酸化膜厚の厚さが違うダブルゲート型トランジスタを用いて、そのトランジスタの酸化膜厚が薄いゲートはオフさせ、酸化膜厚が厚いゲートをオンさせることで電位が変化しないノードを駆動し、回路ブロックのリーク電流を低減する回路自体のリーク電流および回路ブロックのリーク電流を低減する。

(もっと読む)

共存論理デバイスを有するバック・ゲート制御SRAMのための基板解決策

【課題】 共存論理デバイスを有するバック・ゲート制御SRAMのための基板解決策を提供する。

【解決手段】 少なくとも1つの論理デバイス領域と少なくとも1つのスタティック・ランダム・アクセス・メモリ(SRAM)デバイス領域とを含み、各デバイス領域がダブル・ゲート電界効果トランジスタ(FET)を含み、異なるデバイス領域内のFETデバイスのパフォーマンスを改善するためにそれぞれのFETデバイスのバック・ゲートが特定のレベルまでドーピングされる半導体構造を提供する。特に、SRAMデバイス領域内のバック・ゲートは、論理デバイス領域内のバック・ゲートより高濃度ドーピングされる。短チャネル効果を制御するために、論理デバイス領域内のFETデバイスはドープ・チャネルを含み、SRAMデバイス領域内のFETデバイスはドープ・チャネルを含まない。ソース/ドレイン領域下の低ネット・ドーピングおよびチャネル下の高ネット・ドーピングを有する不均一側方ドーピング・プロファイルにより、論理デバイスに関する追加のSCE制御がもたらされるであろう。

(もっと読む)

半導体装置

【課題】トラップの電子の捕獲、放出によるしきい値電圧の変動を小さくすることができる半導体装置を得る。

【解決手段】半導体基板11と、この半導体基板11の表面上にゲート絶縁膜を介して形成されて半導体基板11中での電荷の移動を電気的に制御する少なくとも1つのゲート電極13とを備えた半導体装置であって、半導体基板11は、不純物が添加された半導体で構成され、不純物の濃度が表面の位置で最も低く表面から深い位置となるほど高くなるようにされている。チャネル界面の不純物濃度のみ低下させ、基板11の奥の濃度を上昇させることで、しきい値電圧Vthを所定の電圧に保ちながら、導電チャネルを流れる電流の不均一性を緩和してトラップによるしきい値変動ΔVthを抑制することができる。

(もっと読む)

逆T型チャネルトランジスタを製造する方法

逆T型電界効果トランジスタ(10)を製造する方法を提供する。該方法は、基板(12)上に水平活性化領域(14)及び垂直活性化領域(16)を製造することを含む。該方法は更に、垂直活性化領域の第1の側及び垂直活性化領域の第2の側に側壁スペーサ(22)を形成することを更に有する。該方法は更に、側壁スペーサで被覆されていない水平活性化領域の一部を除去することを含む。該方法は更に側壁スペーサを除去することを含む。該方法は更に、水平活性化領域の少なくとも第1の部分及び垂直活性化領域の少なくとも第1の部分の上にゲート誘電体(26)を形成することを含む。該方法は更に、ゲート誘電体の上にゲート電極(28)を形成することを含む。該方法は更に、水平活性化領域の少なくとも第2の部分及び垂直活性化領域の少なくとも第2の部分の上にソース領域(30)及びドレイン領域(32)を形成することを含む。  (もっと読む)

(もっと読む)

逆T字チャネル型トランジスタを含む複数の型のデバイス、及びその製造方法

半導体デバイスを製造する方法が提供される。この方法は、縦型活性領域(56)と該縦型活性領域(56)の両側に延在する水平活性領域(54)とを有する第1のトランジスタ(94)を形成する工程を含んでいる。この方法はまた、縦型活性領域(58)を有する第2のトランジスタ(96)を形成する工程を含んでいる。この方法は更に、縦型活性領域(60)と該縦型活性領域(60)の片側のみに延在する水平活性領域(54)とを有する第3のトランジスタ(98)を形成する工程を含んでいる。  (もっと読む)

(もっと読む)

半導体装置およびその製造方法

【課題】トランジスタの駆動力を調整する。

【解決手段】SRAMアクセス領域SAにおけるN型のMISトランジスタの上に、圧縮応力含有絶縁膜50および引っ張り応力含有絶縁膜51を形成する。一方、SRAMドライブ領域SDにおけるN型のMISトランジスタの上に、引っ張り応力含有絶縁膜51を形成する。

(もっと読む)

電荷保持特性に優れた不揮発性半導体記憶素子およびその製造方法

【課題】 浮遊ゲートの周囲の絶縁体の絶縁性の向上と、浮遊ゲート中の酸化した金属超微粒子の割合の低減を可能とする不揮発性半導体記憶素子および製造方法を提供すること。

【解決手段】 ギブスの酸化物生成自由エネルギーが、0℃〜1200℃の範囲内で、Siのそれよりも高い元素である難酸化性物質からなる浮遊ゲートと、同浮遊ゲートの周囲を囲む、同エネルギーがSiと同じまたはSiよりも低い易酸化性物質の酸化物からなる絶縁体を有する不揮発性半導体記憶素子の製造方法において、難酸化性物質の浮遊ゲートが物理的形成法を用いて形成され、易酸化性物質の酸化物が物理的形成法または化学的形成法を用いて形成され、ゲート絶縁膜を形成した後に、酸化用気体と還元用気体との混合気体中で、0℃〜1200℃までの温度範囲内において難酸化性物質のみを還元し、易酸化性物質の酸化物のみを酸化するように、混合気体の混合比および温度を制御して熱処理を行う構成を有している。

(もっと読む)

半導体装置及びその製造方法

【課題】 カーボンナノチューブ(CNT)トランジスタを用いる半導体装置のレイアウト面積を縮小する。

【解決手段】 半導体装置は、第1の電極103と、第1の層間絶縁膜104を挟み第1の電極に対向する第2の電極106と、第1及び第2の電極間を貫通する第1のCNT部108と、第1の層間絶縁膜104と第1のCNT部108との間に介在する第1のゲート絶縁膜107と、第1の層間絶縁膜104中に形成され且つ第1のゲート絶縁膜107に接する第1のゲート電極105とを備える。更に、第2の層間絶縁膜114を挟み第2の電極と対向する第3の電極116と、各々第1のものと同様に構成された第2のゲート絶縁膜117、第2のCNT部118及び第2のゲート電極115を備える。各々の電極、ゲート絶縁膜、CNT部、ゲート電極により、垂直に配置された第1及び第2の電界効果トランジスタ151及び152が構成されている。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】スイッチング速度、とくにオン状態からオフ状態への高速でのスイッチングが可能なサイリスタ構成の半導体装置、さらにはこのような半導体装置の駆動方法および製造方法を提供する。

【解決手段】p型領域p1、n型領域n1、p型領域p2、およびn型領域n2がこの順に接して設けられた半導体層101と、両端部に配置されたp型領域p1に接続されたアノード電極Aと、n型領域n1に接続されたカソード電極K電極と、中央に配置されたp型領域p2に接続されたゲート電極G1,G2とを備えた半導体装置1において、ゲート電極は、p型領域p2を構成する半導体層101部分を挟んで対向配置されている。

(もっと読む)

101 - 120 / 141

[ Back to top ]