Fターム[5F083BS02]の内容

Fターム[5F083BS02]の下位に属するFターム

ゲート構造 (68)

ソース/ドレイン構造 (193)

Fターム[5F083BS02]に分類される特許

121 - 140 / 141

半導体装置

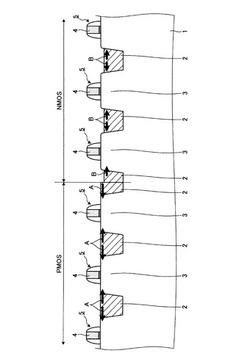

【課題】シャロー・トレンチ・アイソレーション構造により形成された素子分離膜から生じる物理的な応力に起因した半導体装置の電流駆動能力の変動が緩和され、本来の電流駆動能力を発揮可能な半導体装置を得ること。

【解決手段】第1および第2の領域を有する半導体基板と、前記半導体基板の表層に形成される溝と、前記溝に埋め込まれた素子分離絶縁膜と、前記半導体基板の表層に形成され、前記素子分離絶縁膜によって規定される活性領域と、を備え、前記素子分離絶縁膜の表面の高さが前記第1の領域と第2の領域とで異なり、いずれか一方の領域の素子分離絶縁膜の高さが前記半導体基板の表面よりも低いことを特徴とする。

(もっと読む)

半導体装置およびその駆動方法

【課題】無線通信を利用して動作する半導体装置の低消費電力化と高性能化を図ることを目的とする。

【解決手段】無線通信を利用して動作する半導体装置において、演算回路及び通信回路に加え状態制御レジスタを設ける。データの送受信時、すなわち動作磁界が変動する場合に消費電力の大きい演算回路の動作を停止し、動作磁界が変動しない場合に演算回路を動作させることができる。一方、動作磁界が変動する場合に、受信又は送信に最低限必要な機能を受信回路もしくは送信回路で実現することで大容量電源を必要としない。つまり、高度な演算処理を小規模な電源回路で実行することが可能である。このようにして、大規模回路を搭載した半導体装置に好適な構成で、高性能且つ低消費電力の半導体装置を提供できる。

(もっと読む)

半導体装置及びその製造方法

基体平面に対して突出した半導体凸部と、この半導体凸部を跨ぐようにその上部から相対する両側面上に延在するゲート電極と、このゲート電極と前記半導体凸部の間に介在するゲート絶縁膜と、前記半導体凸部に設けられたソース/ドレイン領域とを有するMIS型電界効果トランジスタ、このトランジスタを含む基体上に設けられた層間絶縁膜、及びこの層間絶縁膜に形成された埋め込み導体配線を有し、この埋め込み導体配線は、前記半導体凸部のソース/ドレイン領域と、前記層間絶縁膜下の他の導電部とに接続されていることを特徴とする半導体装置。  (もっと読む)

(もっと読む)

半導体装置

【課題】高速かつ低消費電力動作が可能なブートストラップ回路を有する半導体装置を得る。

【解決手段】NMOS構成のパストランジスタQ1のゲート電極(フローティングゲート電極)とボディ領域とを電気的に接続し、パストランジスタQ1のゲート電極にNMOS構成の分離トランジスタQ2のドレインを接続する。分離トランジスタQ2はゲート電極に電源Vddが付与される。上記したパストランジスタQ1及び分離トランジスタQ2はSOI基板上に他の素子と素子分離して形成される。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】半導体装置の性能を向上させることが可能な技術を提供する。

【解決手段】ロジック回路領域及びメモリセル領域における半導体基板には素子分離絶縁膜4によって活性領域1c,1bがそれぞれ区画されている。活性領域1b,1cにはMOSトランジスタTR2及びドライバトランジスタDTRがそれぞれ形成されている。上面視上において、活性領域1bのゲート幅方向の長さは活性領域1cのそれ以下である。素子分離絶縁膜4では、活性領域1bの周辺に位置する周辺部分4bの上面が活性領域1bの上面よりも下方に位置し、活性領域1cの周辺に位置する周辺部分4cの上面が活性領域1cの上面よりも下方に位置している。素子分離絶縁膜4の上面よりも上方に位置する、活性領域1b,1cの上面及びゲート幅方向の両側面にはゲート絶縁膜6を介してゲート電極7が形成されている。

(もっと読む)

改善されたセル安定性及び性能のためのハイブリッド・バルク−SOI6T−SRAMセル

【課題】 改善されたセル安定性及び性能を示すハイブリッド・バルクSOI 6T STRAMセルを提供すること。

【解決手段】 本発明は、同じ結晶配向又は異なる結晶配向を有するSOI領域及びバルク−Si領域を含む基板と、バルク−Si領域からSOI領域を分離する分離領域と、SOI領域内に配置された少なくとも1つの第1デバイス及びバルク−Si領域内に配置された少なくとも1つの第2デバイスとを含む、6T−SRAM半導体構造体を提供する。SOI領域は、絶縁層の上にシリコン層を有する。バルク−Si領域はさらに、第2デバイスの下にあるウェル領域と、浮遊体効果を安定化させる、ウェル領域へのコンタクトとを含む。ウェル・コンタクトはまた、バルク−Si領域内のFETの閾値電圧を制御して、SOI領域のFET及びバルク−Si領域のFETの組み合わせから構築されたSRAMセルのパワー及び性能を最適化するためにも用いられる。

(もっと読む)

電界効果トランジスタとその製造方法、及び半導体装置

【課題】ソフトエラーレートを向上させる電界効果トランジスタを提供すること

【解決手段】本発明による電界効果トランジスタ1は、第1の空洞51を有する基板10と、ゲート電極40と、拡散層60とを備える。ゲート電極40及び拡散層60は、基板10の表面に平行な面XYにおいて、第1の空洞51を囲むように形成される。チャネル領域70は、第1の空洞51の側面に位置し、基板10の表面に対して略垂直に形成される。

(もっと読む)

積層型デカップリングキャパシタを有する半導体装置

【課題】積層型デカップリングキャパシタを有する半導体装置を提供することにある。

【解決手段】互いに異なった層に形成されたトランジスタを有する半導体装置において、前記記トランジスタを積層して製造する場合に使用される絶縁膜と前記絶縁膜を境界にして上下部層に存在する導電層を用いて形成され、第1,2ライン間に互いに並列連結されたデカップリングキャパシタからなる積層型キャパシタクラスタを複数個備える。

(もっと読む)

半導体集積回路

【課題】

ソフトエラー耐性および加工精度の向上を図る。

【解決手段】

ワード線と直交する第1の方向に延在する第1及び第2のNウェル領域と、第1、第2のNウェル領域に挟まれるPウェル領域とを有し、第1から第4のPMOSトランジスタおよび第1、第2のNMOSトランジスタから1つのメモリセルを形成し、メモリセルを複数有する半導体集積回路であって、1つのメモリセルのうち第1、第2のPMOSトランジスタは、第1のNウェル領域に、第1の方向に並んで配置され、第1、第2のNMOSトランジスタはPウェル領域に形成され、第3、第4のPMOSトランジスタは、第2のNウェル領域に、第1の方向に並んで配置される。

(もっと読む)

半導体装置及びその作成方法

【課題】MOSFETに匹敵する性能を有した半導体装置を提供する。

【解決手段】絶縁表面を有する基体上に非晶質珪素膜を成膜し、非晶質珪素膜上に選択的にマスク絶縁膜を形成して結晶化を助長する金属元素を導入させ、第1の加熱処理により非晶質珪素膜の少なくとも一部を結晶性珪素膜にし、マスク絶縁膜を除去し、パターニングすることにより島状の結晶性珪素膜を形成し、ハロゲン元素を含む雰囲気中において第2の加熱処理を行うことにより、島状の結晶性珪素膜中の金属元素をゲッタリング除去すると共に、ゲイト絶縁膜として用いる熱酸化膜を島状の結晶性珪素膜の表面に形成し、熱酸化膜上にゲイト電極を形成し、一導電性を付与する不純物イオンを注入して島状の結晶性珪素膜にソース領域、ドレイン領域を形成し、ソース領域及び前記ドレイン領域上面に金属膜を形成し、ソース領域とドレイン領域をシリサイド化することを特徴とする。

(もっと読む)

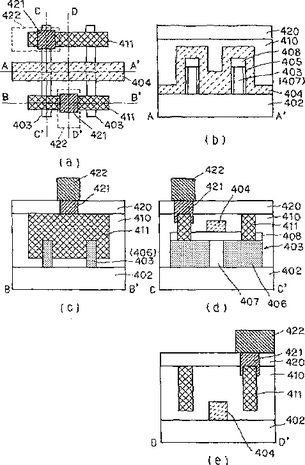

半導体装置、半導体記憶装置および半導体装置の製造方法

【課題】 ゲートからソースへの漏洩電流を伴うことなく、しきい値電圧を可変させるとともに、素子面積の増大を抑制する。

【解決手段】 半導体基板101上には絶縁層102が形成され、絶縁層102上には半導体層103が形成され、さらに、半導体層103上には絶縁層104が形成され、絶縁層104上には半導体層105が形成され、半導体層105上には、ゲート絶縁膜106を介してゲート電極107が形成され、ゲート電極107の側方には、ソース層109およびドレイン層110が形成され、ゲート電極107は、配線層を介して半導体層103に接続されている。

(もっと読む)

非晶質酸化物を利用した半導体デバイス

【課題】透明酸化物膜を用いた半導体デバイスや回路を提供する。

【解決手段】P型領域と、N型領域とを備え、電子キャリア濃度が1018/cm3未満である非晶質酸化物、又は電子キャリア濃度が増加すると共に、電子移動度が増加する傾向を示す非晶質酸化物をN型領域に用いている。電子キャリア濃度が1018/cm3未満である非晶質酸化物又は電子キャリア濃度が増加すると共に、電子移動度が増加する傾向を示す非晶質酸化物からなる第1領域と、第1領域に対してヘテロ接合を形成する第2領域と、を具備する。

(もっと読む)

半導体装置及びその製造方法、並びにメモリ回路

【課題】本発明は、ボディ浮遊効果を抑制することが可能な半導体装置及びその製造方法を提供する。

【解決手段】シリコン基板1と、シリコン基板1上に形成された埋め込み絶縁層2と、埋め込み絶縁層2上に形成された半導体層3とを備えるSOI構造の半導体装置であって、半導体層3は、第1導電型のボディ領域4、第2導電型のソース領域5及び第2導電型のドレイン領域6を有し、ソース領域5とドレイン領域6との間のボディ領域4上にゲート酸化膜7を介してゲート電極8が形成され、ソース領域5は、第2導電型のエクステンション層52と、エクステンション層52と側面で接するシリサイド層51を備え、シリサイド層51とボディ領域4との境界部分に生じる空乏層の領域に結晶欠陥領域12が形成されている。

(もっと読む)

半導体集積回路装置およびその製造方法

【課題】 トランジスタの接合容量を低下させ、ソフトエラー耐性およびノイズ耐性を保持した半導体集積回路装置を提供する。

【解決手段】 半導体集積回路装置100は、半導体基板内のバルク基板領域10上に形成され、ソース/ドレインが第1の基準電位GNDに接続された第1のトランジスタTBn1および、

p型バルク基板領域上に形成されたn型の不純物層領域12と、不純物層領域上に形成されたp型の半導体領域14と、半導体領域に形成されn型のソース/ドレイン30と、ソース・ドレイン間にあり半導体領域上に形成されたゲート絶縁膜40と、ゲート絶縁膜上に形成されたゲート電極50と、ソース−ドレイン方向の断面において、ソース、ドレイン、不純物層領域およびゲート絶縁膜によって囲まれたp型のボディ領域16とを含み、前記不純物層領域が空乏化された第2のトランジスタTSn1、を備え、

第2のトランジスタのソース/ドレインは第1のトランジスタを介して第1の基準電位に接続されている。

(もっと読む)

半導体装置、SRAMおよび半導体装置の製造方法

【課題】 狭い活性領域にコンタクト部を配設する工程を、容易に行うことができる半導体装置および半導体装置等を提供する。

【解決手段】 本発明に係る半導体装置は、SOI基板10、活性領域3a、第一の絶縁膜(完全分離絶縁膜)3b、第二の絶縁膜(部分分離絶縁膜)3c、およびコンタクト部4を備えている。ここで、活性領域3aは、SOI層3の表面内に形成されている。また、第一の絶縁膜3bは、活性領域3aの一方の側面に形成されており、かつ、SOI層3の表面から埋め込み絶縁膜2にかけて形成されている。また、第二の絶縁膜3cは、活性領域3aの他方の側面において形成されており、かつ、SOI層3の表面から、埋め込み絶縁膜2に至らない所定の深さにかけて形成されている。また、コンタクト部4は、平面視において、活性領域3aの中心より第一の絶縁膜3bが存する側に配設されている。

(もっと読む)

半導体記憶装置およびその製造方法

【課題】 リフレッシュ動作を必要とせず、かつ、高集積化・大容量化を実現する半導体記憶装置を提供する。

【解決手段】 半導体基板1上に形成されたメモリセルと、第1電荷保持部と、第2電荷保持部と、第1アクセストランジスタと、第1リークトランジスタ522Aと、第2アクセストランジスタと、第2リークトランジスタと、層間絶縁膜16と、層間絶縁膜16上に形成され、第1電荷保持部に接続されたメモリセル内の第1MISFET56A(Metal-Insulator-Semiconductor Field Effect Transistor)と、層間絶縁膜16上に形成され、第2電荷保持部と接続されたメモリセル内の第2MISFET(Metal-Insulator-Semiconductor Field Effect Transistor)とを備える。

(もっと読む)

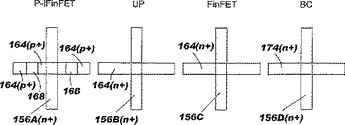

反転型FinFET薄膜トランジスタを用いたFinFETSRAMセル

【課題】反転型FinFETトランジスタ(P2)とFinFETトランジスタ(N3)とを含む、SRAMセル(130)などの集積回路を提供すること。

【解決手段】反転型FinFETトランジスタは、基板上に半導体構造(100)によって形成された第1のゲート領域(108)、ならびに、第1のゲート領域上に配置された第1のチャネル領域(112)と、第1のチャネル領域のいずれか一方の側に形成されたソース(110)およびドレイン(114)とを有する、半導体層(104)からなる第1のボディ領域を含む。FinFETトランジスタ(N3)は、反転型FinFETトランジスタに結合しており、第2のチャネル領域(118)と、第2のチャネル領域のいずれか一方の側に形成されたソース(116)およびドレイン(120)とを有する、半導体構造(102)によって形成された第2のボディ領域、ならびに、第2のチャネル領域上に配置された、半導体層からなる第2のゲート領域(122)を含む。  (もっと読む)

(もっと読む)

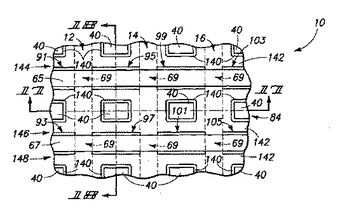

DRAMセル用の分離領域を有する半導体構造及び製造方法

本発明は、垂直に延びるピラー(80,82)を含む半導体構造、及び、そのような構造を形成する方法を含む。垂直に延びるピラーは、トランジスタデバイス(80,95)内に組み込まれることができ、トランジスタデバイスの垂直に延びるチャネル領域を含むことができる。トランジスタデバイスは、集積回路内に組み込まれることができ、ある態様では、たとえば、ダイナミックランダムアクセスメモリ(DRAM)構造などのメモリ構造に組み込まれる。  (もっと読む)

(もっと読む)

半導体装置並びにその配置及び製造方法

【課題】半導体装置及びその装置の配置及び製造方法を提供する。

【解決手段】複数のワードライン選択信号と複数のカラム選択信号に応答してアクセスされる複数のメモリセルを備えたメモリセルアレイ、ロウアドレスをデコーディングして複数のワードライン選択信号を発生するロウデコーダ、及びカラムアドレスをデコーディングして複数のカラム選択信号を発生するカラムデコーダを備える。ロウ及びカラムデコーダは、複数のインバータ及び複数のNANDゲートを備える。複数のインバータそれぞれは、少なくとも一つの第1プルアップトランジスタ及び第1プルダウントランジスタを備る。複数のNANDゲートそれぞれは、少なくとも2個の第2プルアップトランジスタ及び少なくとも2個の第2プルダウントランジスタを備える。第1及び第2プルアップトランジスタ及び第1及び第2プルダウントランジスタは、少なくとも2層に積層して配置され。

(もっと読む)

半導体記憶装置及びその製造方法

【課題】SRAMセルの形成面積の増大を抑えつつ、動作の安定化を図る。

【解決手段】SRAMセルのアクセストランジスタQ5のゲート電極33の上には、ワード線に接続するコンタクト45が形成される。コンタクト45は、素子分離絶縁膜14を突き抜けてSOI層13にまで達する。ドライバトランジスタQ1のボディー領域と第1アクセストランジスタQ5のボディー領域とは、素子分離絶縁膜14下方のSOI層13を介して互いに電気的に接続している。よって、アクセストランジスタQ5はそのゲート電極とボディー領域との間がコンタクト45で接続されたDTMOS構造になり、コンタクト45はさらに第1ドライバトランジスタQ1のボディー領域にも電気的に接続する。

(もっと読む)

121 - 140 / 141

[ Back to top ]