Fターム[5F083EP07]の内容

半導体メモリ (164,393) | EPROM、EEPROMの構造 (21,423) | 電荷蓄積機構 (5,261) | FGを有するもの (3,098) | 粒径 (19)

Fターム[5F083EP07]に分類される特許

1 - 19 / 19

半導体記憶装置およびその製造方法

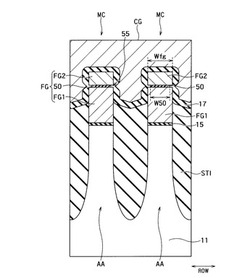

【課題】微細化されても、コントロールゲートとフローティングゲートとの間のカップリング容量比を増大させることができる半導体記憶装置およびその製造方法を提供する。

【解決手段】半導体記憶装置は、半導体基板を備える。第1の絶縁膜は、半導体基板上に形成されている。フローティングゲートは、第1の絶縁膜上に設けられた第1のフローティングゲート部分、第1のフローティングゲート部分上に設けられた中間絶縁膜、および、中間絶縁膜上に設けられた第2のフローティングゲート部分を含み、電荷を蓄積可能に構成されている。第2の絶縁膜は、フローティングゲートの上面および側面に設けられている。コントロールゲートは、第2の絶縁膜を介してフローティングゲートの上面および側面に対向し、フローティングゲートの電圧を制御する。フローティングゲートの側面において中間絶縁膜が第1および第2のフローティングゲート部分に対して窪んでいる。

(もっと読む)

不揮発性半導体記憶装置

【課題】ゲート電極間絶縁膜のリーク電流を抑制し、電気的信頼性を向上した不揮発性半導体記憶装置を提供する。

【解決手段】半導体基板上に行列状に形成された複数のメモリ素子と、同一列方向のメモリ素子に選択的に接続される複数のビット線と、同一行方向のメモリ素子に接続される複数のワード線とを具備し、各メモリ素子は、半導体基板上に順次形成された第1のゲート絶縁膜、電荷蓄積層、第2のゲート絶縁膜、制御電極と、電荷蓄積層の対向する側面に沿って、前記シリコン基板上面に形成された1対の不純物注入層とを具備し、ビット線に垂直な方向に沿った断面における電荷蓄積層の上部コーナー部が曲面を有し、上部コーナー部が前記第1のゲート絶縁膜の上方にある。

(もっと読む)

マルチドットフラッシュメモリ

【課題】マルチドットフラッシュメモリの書き込み/消去の低消費電力化を図る。

【解決手段】本発明の例に係わるマルチドットフラッシュメモリは、書き込み/消去の対象となる選択されたフローティングゲートの左側に存在するビット線BL13,BL12,BL11,…の電位V2(1), V2(2), V2(3),…を、V2(1)>V2(2)>V2(3)>…とし、選択されたフローティングゲートの右側に存在するビット線BL14,BL15,BL16,…の電位V1(1), V1(2), V1(3),…を、V1(1)<V1(2)<V1(3)<…とする。但し、V2(1)は、プラス電位、V1(1)は、マイナス電位である。また、ビット線の電位は、選択されたフローティングゲートから離れるに従い、0Vに収束する。

(もっと読む)

不揮発性半導体記憶装置の駆動方法及び不揮発性半導体記憶装置

【課題】書き込み・消去を高速化したり、或いはデータの保持特性を向上させる不揮発性半導体記憶装置の駆動方法及び不揮発性半導体記憶装置を提供する。

【解決手段】チャネルと前記チャネルの両側に設けられたソース・ドレイン領域を有する半導体層と、前記チャネルの上に設けられた第1の絶縁膜と、浮遊電極と、第2の絶縁膜と、ゲート電極と、を有する不揮発性半導体記憶装置の駆動方法であって、前記浮遊電極に第1の極性の電荷が注入された状態とするために、前記半導体層と前記ゲート電極との間に、前記第1の極性の電荷を前記第2の絶縁膜に注入する第1の電位差を与え、その後、前記第1の極性と逆極性の第2の極性の電荷を前記第2の絶縁膜に注入する第2の電位差を与え、その後、前記第1の極性の電荷を前記浮遊電極に注入する第3の電位差を与えることを特徴とする不揮発性半導体記憶装置の駆動方法。

(もっと読む)

マイクロコンピュータ及びデータプロセッサ

【課題】不揮発性メモリセルから記憶情報を高速に読み出すことができる半導体装置を提供する。

【解決手段】マイクロコンピュータは、内部バス68と、前記内部バスに結合されている中央演算部61と、前記内部バスに結合された不揮発性メモリ63とを含む。前記不揮発性メモリは、第1ゲートと第2ゲートとを含む複数の不揮発メモリセルと、前記複数の不揮発メモリセルの一つの前記第1ゲートに結合された第1回路21と、前記複数の不揮発メモリセルの一つの前記第2ゲートに結合された第2回路22と、前記第1回路に供給する第1電圧と前記第2回路に供給する第2電圧とを生成する電圧生成回路VS,77と、を含む。前記第1回路のゲート耐圧は前記第2回路のゲート耐圧より低い。

(もっと読む)

半導体メモリ素子の形成方法

【課題】半導体基板上にポリシリコン膜を形成した後、熱処理工程条件を調節して実施することにより、ポリシリコン膜の粒子サイズの増加を抑制することができるフラッシュメモリ素子等の半導体メモリ素子の形成方法を提供する。

【解決手段】半導体基板300上にトンネル絶縁膜302を形成する段階と、トンネル絶縁膜302上に、高融点の金属物質を含むシリコン膜304を形成する段階とを含む。シリコン膜304に高融点の異種金属を混合することにより、後続で行う熱処理工程の際に、シリコン膜304内の応力を減少させて粒子成長を抑制することができるので、ナノサイズの粒子を形成して、半導体メモリ素子の電気的特性を向上させることができる。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】多結晶シリコンの空乏化を抑制して微細化ができる半導体装置および半導体装置の製造方法を提供する。

【解決手段】多結晶シリコンからなる第1の層を有する制御ゲート電極を備え、前記第1の層は、不純物を含んだ多結晶シリコンからなる第1の膜をエッチバックしてその膜厚を減らしたものであって、前記第1の膜の不純物活性化率を保持していることを特徴とする半導体装置が提供される。また、絶縁膜上に設けたアモルファスシリコン膜を熱処理して、不純物を含んだ多結晶シリコンからなる第1の膜を形成する工程と、前記第1の膜をエッチバックして、前記第1の膜の膜厚を減らす工程と、を備えたことを特徴とする半導体装置の製造方法が提供される。

(もっと読む)

ナノ構造

【課題】非常に小さい幾何学的特徴をもつナノ構造のデバイスを製作することができる改善された方法を提供すること。

【解決手段】予め決められた形状をもつ一又はそれより多い電気的に帯電された部位を、半導体基板の表面又は半導体基板の不動態化表面である第一の表面上に形成する工程であって、その際、前記一又はそれより多い部位に対応する前記第一の表面の部分と固体材料の道具(9)とを、前記道具と前記第一の表面との間で電荷を移動させるように接触させる工程;

第二の材料の粒子(7)を、前記一又はそれより多い電気的に帯電された部位の近くに流れるようにし、該電気的に帯電された部位の極性に対する該電荷の極性により、該粒子(7)を前記一又はそれより多い電気的に帯電された部位にひきつけるか又は反発させることによって、該粒子(7)を上記形成工程において提供された電気的に帯電された部位に一致させて第一の表面上に堆積させる工程;及び

該堆積させた粒子を使用して、ナノメートルサイズのフィラメント若しくは粒子の鎖(148)、カーボンナノチューブのアレイ若しくはフィラメント(158)、又は半導体性材料若しくは磁性材料のフィラメント若しくはナノロッド(168)をつくる工程、

を含む方法によって、半導体基板の表面又は半導体基板の不動態化表面上にナノ構造を形成する。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】粒状結晶シリコン膜の長所である小さなグレイン、良好な界面平坦性、ボロンのシリコン基板への拡散防止効果を維持しつつ、柱状結晶シリコン膜単層で形成した場合に匹敵する良好なカバレッジ特性を実現することが可能なように改良されたシリコン膜を有する半導体装置を提供することを主要な目的とする。

【解決手段】本発明にかかる半導体装置は、積層シリコン膜を有する半導体装置であって、上記積層シリコン膜は、粒状結晶のシリコン膜で形成された最上層2及び最下層1と、上記最上層2と上記最下層1との間に設けられ、柱状結晶のシリコン膜3aを含む中間層3とを備える。

(もっと読む)

半導体装置およびその製造方法

【課題】半導体装置の高集積化を達成する。

【解決手段】第1導電型の半導体基板上に第1ゲート絶縁膜4を介して形成された浮遊ゲート7と、前記半導体基板上に第2絶縁膜を介して形成された第2電荷保持領域と、第1方向に延在し、前記第1電荷保持領域の上に第2ゲート絶縁膜5を介して形成された制御ゲート8と、前記第1方向に延在し、前記第2電荷保持領域の上に第2ゲート絶縁膜を介して形成された第2ゲート電極と、第2方向に延在し、前記第1及び第2ゲート電極と交差するように前記半導体基板上に形成された半導体層10とを具備し、前記半導体層は、第2導電型のn型導電領域3が形成される。

(もっと読む)

ナノ結晶シリコン量子ドットメモリ装置及びその形成方法

【課題】 ナノ結晶シリコン量子ドットメモリ装置と関連する製造方法を提供する。

【解決手段】 ナノ結晶シリコン量子ドットメモリ装置の製造方法は、シリコン基板活性層104上にゲート酸化膜108を形成する工程と、ゲート酸化膜108上に多結晶シリコン/二酸化シリコン積層膜112を含むナノ結晶シリコンメモリ膜110を形成する工程と、ナノ結晶シリコンメモリ膜110上にコントロール酸化膜118を形成する工程と、コントロール酸化膜118上にゲート電極120を形成する工程と、シリコン活性層104にソース/ドレイン領域122,124を形成する工程とを有する。ナノ結晶シリコンメモリ膜110はCVD法を用いて非晶質シリコン層を堆積し、非晶質シリコン層の一部を熱酸化処理することによって形成される。非晶質シリコン層の堆積及び熱酸化処理は繰り返され、複数層の多結晶シリコン/二酸化シリコン積層膜を形成する。

(もっと読む)

半導体記憶装置およびその動作方法

【課題】半導体記憶装置の、例えば情報記憶保持期間等の情報記憶特性を向上する。

【解決手段】半導体記憶装置は、半導体基板に形成されたP型ウエル領域5と、P型ウエル領域5を挟むように形成されたソース領域2およびドレイン領域3と、P型ウエル領域5上に第一の絶縁膜10を介して形成された電荷保持部1と、電荷保持部1上に第二の絶縁膜11を介して形成されたゲート電極4とを備えている。電荷保持部1は、常温での荷電粒子6の分布状態を保持し得る絶縁体からなり、また、電荷保持部1では、内部の荷電粒子の異なる分布状態を保持することによって情報を記憶するようになっている。

(もっと読む)

不揮発性メモリ

電子デバイスは、ゲート線、ビット線、またはこれらの組合せに接続されたメモリセルを含む。1つの実施形態では、少なくとも2つのメモリセルのセットは第1の方向(例えば、行または列)に沿って実質的に配向される。第2のゲート線2741に比して第1のゲート線2702は、メモリセルのより少ない行または列に電気的に接続される。例えば、第1のゲート線は第1のメモリセルのセットのみに電気的に接続され、第2のゲート線は第2および第3のメモリセルのセットに電気的に接続される。別の実施形態では、第2のビット線に比して第1のビット線は、メモリセルのより少ない行または列に電気的に接続される。さらに別の実施形態では、別のメモリセルのセットが、第1の方向に対して実質的に直交する別の方向に実質的に沿って配向される。  (もっと読む)

(もっと読む)

溝に横方向第1ゲート及び縦方向第2ゲートを含むスプリットゲート記憶装置

スプリットゲート記憶装置には、第1ゲート誘電体に接触した第1ゲート電極と、第2ゲート誘電体に接触した第2ゲート電極とが含まれる。第1拡散領域は、半導体基板中に画成された溝(108)の一部の下に横たわり、第2拡散領域は、基板(102)の上部を占有する。第1ゲート誘電体(110)は、溝を内張りする。第1及び第2ゲート誘電体の内の1つには、一層の不連続記憶素子(DSE)(120)が含まれ、第1及び第2ゲート電極の内の1つは、少なくとも部分的に溝内に配置される。一事例では、第1ゲート電極は制御ゲートであり、第1誘電体は一層のDSEを含む。他の事例では、第1ゲート電極は選択ゲートであり、第2誘電体は一層のDSEを含む。第2ゲート誘電体は基板の上面全体に横たわる。  (もっと読む)

(もっと読む)

半導体装置およびその作製方法

【課題】半導体膜のチャネル領域の端部におけるゲート絶縁膜の段切れや薄膜化により生じる半導体膜とゲート電極とのショートやリーク電流を抑制する半導体装置および当該半導体装置の作製方法の提供を課題とする。

【解決手段】基板上に連続して設けられた半導体膜と、半導体膜の上方にゲート絶縁膜を介して設けられた導電膜と、導電膜と重ならない半導体膜に形成されたソース領域及びドレイン領域と、導電膜の下方に位置する半導体膜であってソース領域とドレイン領域の間に形成されたチャネル領域とを有する複数の薄膜トランジスタと、導電膜と重ならない半導体膜であってソース領域及びドレイン領域と隣接して設けられた不純物領域とを有し、導電膜をチャネル領域及びチャネル領域に隣接する半導体膜上に設ける構成とする。

(もっと読む)

半導体メモリ

【課題】 情報の保持時間を確保できる半導体メモリを提供する。

【解決手段】 半導体メモリは、第1面を有する半導体基板1を有する。第1絶縁膜4aは、第1面上に設けられ、第1面と離れた位置に第1面内の第1方向に広がりを持つ溝11を有する。第2絶縁膜4bは、溝の開口を塞ぐように第1絶縁膜上に形成される。複数の微粒子12が、溝内に設けられる。ゲート電極G1は、溝の上方において第2絶縁膜上に設けられる。チャネル領域は、溝の下方の半導体基板の表面に設けられ、溝の第1方向における長さより短い第1方向における長さを有する。1対のソース/ドレイン領域S/Dが、チャネル領域を挟むように半導体基板の表面に設けられる。

(もっと読む)

不揮発性半導体記憶装置およびその製造方法

【課題】

ナノドットを均一に形成することで,高信頼のナノドットメモリを提供する。また,トンネル絶縁膜にシリコン酸化膜代替材料を採用することにより,高速,高信頼のナノドットメモリを提供する。

【解決手段】

シリコンあるいはゲルマニウム基板,好ましくはシリコンあるいはゲルマニウムの(111)基板上にHfO2,ZrO2あるいはCeO2の高誘電率絶縁膜をエピタキシャル成長させたトンネル絶縁膜と,前記トンネル絶縁膜上に形成されたCoSi2あるいはNiSi2のシリサイドナノドットを有することを特徴とする。

(もっと読む)

半導体装置およびその製造方法

【課題】 トンネル絶縁膜の特性を確保した上で消去動作後のVth素分布幅の拡大を防止し、さらに所定の場合デバイス動作速度を向上させることができる半導体装置およびその製造方法を提供する。

【解決手段】 トレンチに絶縁膜を充填して分離絶縁膜5を形成する工程と、分離絶縁膜を保護膜が露出されるまで平坦化する工程と、保護膜を除去して第1ポリシリコン層3と分離絶縁膜5との上に第2ポリシリコン層4を形成する工程とを有し、第1ポリシリコン層形成工程では、第1ポリシリコン層としてノンドープのシリコン層を形成し、第2ポリシリコン層形成工程では、第2ポリシリコン層としてドープトシリコン層を形成するか、またはノンドープシリコン層を形成してその後に不純物を注入するかして、その第2ポリシリコン層中の不純物を、その後の熱履歴により、第1ポリシリコン層へと熱拡散させる。

(もっと読む)

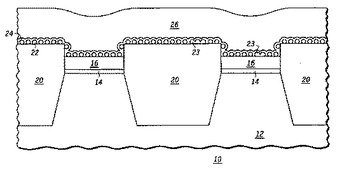

改良された表面形状を用いるメモリ構造の形成方法及びその構造。

半導体装置10のゲートカップリング比を増大させるため、超微細結晶等の個別素子22が浮遊ゲート16上に析出される。一実施形態において、個別素子22は、蒸気相中で予め形成され、静電気力によって半導体装置10に吸着される。一実施形態において、個別素子22は、それらが吸着されるチャンバとは異なるチャンバ内で予め形成される。更に別の実施例において、同じチャンバが全ての析出工程に使用される。界面層17は、必要に応じて、浮遊ゲート16と個別素子22との間に形成される。  (もっと読む)

(もっと読む)

1 - 19 / 19

[ Back to top ]