Fターム[5F083EP21]の内容

半導体メモリ (164,393) | EPROM、EEPROMの構造 (21,423) | 制御機構 (7,428)

Fターム[5F083EP21]の下位に属するFターム

CGを有するもの (4,415)

CG、FG、SG以外のゲートを有するもの (262)

SGを有するもの (2,694)

ゲート/チャネル/ゲート構造 (16)

Fターム[5F083EP21]に分類される特許

21 - 40 / 41

半導体装置

【課題】電力が供給されない状況でも記憶内容の保持が可能で、かつ、書き込み回数にも制限が無い、新たな構造の半導体装置を提供する。

【解決手段】第1のトランジスタ160と、第2のトランジスタ162と、第1のトランジスタ160のソース領域またはドレイン領域120と、第2のトランジスタ162のチャネル形成領域144との間に設けられた絶縁層128と、を含むメモリセルを有し、第1のトランジスタ160と、第2のトランジスタ162とは、少なくとも一部が重畳して設けられる半導体装置である。また、絶縁層128と第2のトランジスタのゲート絶縁層146は、式((ta/tb)×(εrb/εra)<0.1)を満たす。(但し、式中、taはゲート絶縁層146の膜厚を示し、tbは絶縁層128の膜厚を示し、εraはゲート絶縁層146の誘電率を示し、εrbは絶縁層128の誘電率を示す。)

(もっと読む)

半導体装置

【課題】電力が供給されない状況でも記憶内容の保持が可能で、かつ、書き込み回数にも制限が無い、新たな構造の半導体装置を提供することを目的の一とする。

【解決手段】メモリセルアレイを構成する複数のメモリセルが、複数行ごとに複数のブロックに分割され、共通ビット線は、各ブロックにおいて、選択トランジスタを介して分割ビット線と電気的に接続されており、メモリセルの一は、第1のチャネル形成領域を含む第1のトランジスタと、第2のチャネル形成領域を含む第2のトランジスタと、容量素子と、を有し、ソース線は、第1のソース電極と接続され、分割ビット線は、第1のドレイン電極および第2のソース電極と接続され、ワード線は、容量素子の電極の一方と接続され、信号線は、第2のゲート電極と接続され、第1のゲート電極と、第2のドレイン電極と、容量素子の電極の他方とが接続される半導体装置を提供する。

(もっと読む)

半導体装置の作製方法

【課題】酸化物半導体を用いた半導体装置に安定した電気的特性を付与し、高信頼性化することを目的の一とする。

【解決手段】第1の絶縁膜を形成し、第1の絶縁膜上に、ソース電極およびドレイン電極、ならびに、ソース電極およびドレイン電極と電気的に接続する酸化物半導体膜を形成し、酸化物半導体膜に熱処理を行って、酸化物半導体膜中の水素原子を除去し、水素原子が除去された酸化物半導体膜上に、第2の絶縁膜を形成し、第2の絶縁膜に酸素ドープ処理を行って、第2の絶縁膜中に酸素原子を供給し、第2の絶縁膜上の酸化物半導体膜と重畳する領域にゲート電極を形成する半導体装置の作製方法である。

(もっと読む)

半導体メモリ装置

【課題】オフ状態のソース、ドレイン間のリーク電流の低いトランジスタを書き込みトランジスタに用いて、データを保存する半導体メモリ装置を提供する。

【解決手段】書き込みトランジスタのドレインと読み出しトランジスタのゲート、および、前記ドレインとキャパシタの一方の電極を接続した記憶セルを複数用いて形成されたマトリクスにおいて、書き込みトランジスタのゲートを書き込みワード線に、書き込みトランジスタのソースおよび読み出しトランジスタのソースをビット線に、読み出しトランジスタのドレインを読み出しワード線に接続する。ここで、書き込みトランジスタと読み出しトランジスタの導電型を異なるものとする。集積度を高めるために、バイアス線を他行の読み出しワード線で代用したり、記憶セルを直列に接続し、NAND構造とし、読み出しワード線と書き込みワード線を共用してもよい。

(もっと読む)

半導体装置および半導体装置の駆動方法

【課題】電力が供給されない状況でも記憶内容の保持が可能で、かつ、書き込み回数にも制限が無い、新たな構造の半導体装置を提供することを目的の一とする。また、新たな構造の半導体装置の高集積化を図り、単位面積あたりの記憶容量を増加させることを目的の一とする。

【解決手段】トランジスタのオフ電流を十分に小さくすることができる材料、例えば、ワイドギャップ半導体である酸化物半導体材料を用いて半導体装置を構成する。トランジスタのオフ電流を十分に小さくすることができる半導体材料を用いることで、長期間にわたって情報を保持することが可能である。また、半導体装置の各メモリセルを構成する、酸化物半導体を用いたトランジスタを直列に接続することにより、隣り合うメモリセルにおいて、酸化物半導体を用いたトランジスタのソース電極またはドレイン電極をお互いに接続させることができ、メモリセルの占有面積を低減することができる。

(もっと読む)

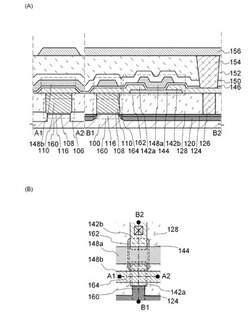

半導体装置

【課題】電力が供給されない状況でも記憶内容の保持が可能で、かつ、書き込み回数にも制限が無い、新たな構造の半導体装置を提供することを目的の一とする。

【解決手段】第1のトランジスタ上に設けられた第2のトランジスタと容量素子とを有し、容量素子は、第2のトランジスタのソース電極またはドレイン電極と、ゲート絶縁層と、第2のトランジスタを覆う絶縁層上に設けられた容量素子用電極を含み、第2のトランジスタのゲート電極と、容量素子用電極とは、絶縁層を介して少なくとも一部が重畳して設けられる半導体装置を提供する。第2のトランジスタのゲート電極と、容量素子用電極とを、異なる層で形成することで、半導体装置の集積度を向上させることができる。

(もっと読む)

PMOS・NMOS・PMOS・NMOS構造を備えた4トランジスタ不揮発性メモリセル

半導体装置の作製方法

【課題】信頼性の高い半導体装置を提供することを課題の一とする。また、信頼性の高い半導体装置の作製方法を提供することを課題の一とする。また、消費電力が低い半導体装置を提供することを課題の一とする。また、消費電力が低い半導体装置の作製方法を提供することを課題の一とする。

【解決手段】成膜中に水素原子を含む不純物と強く結合する物質を成膜室に導入して、成膜室に残留する水素原子を含む不純物と反応せしめ、水素原子を含む安定な物質に変性することで、高純度化された酸化物半導体層を形成する。水素原子を含む安定な物質は酸化物半導体層の金属原子に水素原子を与えることなく排気されるため、水素原子等が酸化物半導体層に取り込まれる現象を防止できる。水素原子を含む不純物と強く結合する物質としては、例えばハロゲン元素を含む物質が好ましい。

(もっと読む)

半導体装置

【課題】良好な特性を維持しつつ、微細化を達成した、酸化物半導体を用いた半導体装置を提供することを目的の一とする。

【解決手段】酸化物半導体層と、酸化物半導体層と接するソース電極及びドレイン電極と、酸化物半導体層と重なるゲート電極と、酸化物半導体層とゲート電極との間に設けられたゲート絶縁層と、酸化物半導体層に接して設けられた絶縁層と、を有し、酸化物半導体層は、該酸化物半導体層の端面において、ソース電極またはドレイン電極と接し、且つ該酸化物半導体層の上面において、絶縁層を介して、ソース電極またはドレイン電極と重なる半導体装置である。

(もっと読む)

半導体装置

【課題】電力が供給されない状況でも記憶内容の保持が可能で、かつ、書き込み回数にも制限が無い、新たな構造の半導体装置を提供することを目的の一とする。

【解決手段】第1のトランジスタと第2のトランジスタと容量素子とを各々含む複数のメモリセルをマトリクス状に配置し、メモリセルの一と他のメモリセルとを接続する配線(ビット線とも呼ぶ)と、第1のトランジスタにおけるソース電極またはドレイン電極と、が、第2のトランジスタにおけるソース電極またはドレイン電極を介して電気的に接続した構成とした半導体装置を提供する。これにより、第1のトランジスタにおけるソース電極またはドレイン電極と、第2のトランジスタにおけるソース電極またはドレイン電極と、を異なる配線に接続する場合と比較して配線の数を削減することができるため、半導体装置の集積度を向上させることができる。

(もっと読む)

半導体装置

【課題】不揮発性記憶装置と揮発性記憶装置の双方のメリットを享受する記憶装置を提供する。

【解決手段】基板または基板上に設けられた第1のトランジスタと、第1のトランジスタよりも上に設けられた第2のトランジスタを有する半導体装置において、第1のトランジスタと第2のトランジスタの少なくとも一部を重畳させ、第1のトランジスタのゲート電極と、第2のトランジスタのソース電極またはドレイン電極を電気的に接続させる。第1のトランジスタとしてはシリコン単結晶により設けられたものが好ましく、第2のトランジスタとしてはオフ電流が極端に小さい酸化物半導体により設けられたものが好ましい。

(もっと読む)

半導体装置

【課題】電力が供給されない状況でも記憶内容の保持が可能で、かつ、書き込み回数にも制限が無い、新たな構造の半導体装置を提供することを目的の一とする。

【解決手段】ソース線と、ビット線と、第1の信号線と、第2の信号線と、ワード線と、ソース線とビット線との間に、接続されたメモリセルと、ビット線と電気的に接続された第1の駆動回路と、第1の信号線と電気的に接続された第2の駆動回路と、第2の信号線と電気的に接続された第3の駆動回路と、ワード線及びソース線と電気的に接続された第4の駆動回路と、を有し、第1のトランジスタは、酸化物半導体以外の半導体材料を用いて構成され、第2のトランジスタは、酸化物半導体材料を含んで構成される。

(もっと読む)

全NMOS−4トランジスタ不揮発性メモリセル

ゲート電極が共通ストレージノードに接続される複数の全NMOS−4トランジスタNVMセルを含むNVMセルアレイプログラム方法。第1NMOSプログラム、第2NMOS読出、第3NMOS消去、第4NMOS制御トランジスタのドレイン、バルク領域、ソース、ゲート電極が正基準電圧にし、プログラム用に選択されるセル毎に、読出トランジスタのソース、ドレイン、バルク領域電極に禁止電圧を印加し、プログラムトランジスタのソース、ドレイン電極を正基準電圧に、バルク領域電極を正基準電圧又は禁止電圧に維持する。選択されないセル毎に、読出及びプログラムトランジスタのソース、ドレイン、バルク領域電極を禁止電圧にし、プログラムするセルに、プログラム時間中、制御トランジスタのソース、ドレイン、バルク領域電極を正基準電圧から所定の負制御電圧に、消去トランジスタのソース、ドレイン、バルク領域電極を正電源電圧から所定の負消去電圧に傾斜減少させる。プログラムするセル毎に、この時間の終わりに、制御トランジスタのソース、ドレイン、バルク領域電極を所定の負制御電圧から電源電圧に、消去トランジスタのソース、ドレイン、バルク領域電極を所定の負消去電圧から正基準電圧に傾斜増加させる。NVMセル毎に、プログラム、消去、制御トランジスタのソース、ドレイン、バルク領域電極を正基準電圧に戻し、読出トランジスタのソース、ドレイン、バルク領域電極を禁止電圧にする。

(もっと読む)

(もっと読む)

半導体装置

【課題】電力が供給されない状況でも記憶内容の保持が可能で、かつ、書き込み回数にも制限が無い、新たな構造の半導体装置を提供することを目的とする。

【解決手段】チャネル形成領域と、第1のゲート絶縁層と、第1のゲート電極と、第1のソース電極及び第1のドレイン電極と、を有する第1のトランジスタと、酸化物半導体層と、第2のソース電極及び第2のドレイン電極と、第2のゲート絶縁層と、第2のゲート電極と、を有する第2のトランジスタと、第2のソース電極または第2のドレイン電極の一方と、第2のゲート絶縁層と、第2のゲート絶縁層上に第2のソース電極または第2のドレイン電極の一方と重畳するように設けられた電極と、を有する容量素子と、を有し、第1のゲート電極と、第2のソース電極又は第2のドレイン電極の一方とは電気的に接続されている。

(もっと読む)

不揮発性メモリセルを含む電子デバイス用の回路および電子デバイスの製造方法

不揮発性メモリセル(10、20、30、40、50、60、70、80、90、100)に用いられる回路は、電荷変更端子(102,202,302,402,502,602,702,802,902,1001)および出力端子(108,208,308,408,508,608,708,808,908,1008)を備えている。回路は、電気的にフローティングの状態にあるゲート電極と電流伝達電極を備えるアクティブ領域とを有する第1のトランジスタ(11,21,31,41,51,61,71,81,91,1021)をさらに備え、電流伝達電極は出力端子に結合する。回路は第1および第2の電極を有する第2のトランジスタ(12,22,32,42,52,62,72,82,92,1002)をさらに備え、第1の電極は第1のトランジスタのゲート電極に、第2の電極は電荷変更端子に結合する。メモリセルの状態を変更するときには、第2のトランジスタをアクティブにし、第1のトランジスタのゲート電極とアクティブ領域の間に有意量の電荷の流出は生じない。他の実施例は電子デバイス自体およびその製法に関する。  (もっと読む)

(もっと読む)

不揮発性半導体記憶装置及びその使用方法

【課題】 セル面積の著しい増加を招かず、しかし、ディスターブの問題を解決した不揮発性記憶素子を提供すること。

【解決手段】 半導体基板に形成され第1の端子に接続されたp型の第1のウェルと、第1のウェルに形成され、第2の端子と第3の端子の間に直列に接続された第1のNMOSトランジスタ及び第2のNMOSトランジスタと、半導体基板に形成され第4の端子に接続されたn型の第2のウェルと、第2のウェルに形成され、第5の端子と第6の端子の間に直列に接続された第1のPMOSトランジスタ及び第2のPMOSトランジスタとを含み、第1のNMOSトランジスタのゲートは第7の端子を構成し、第1のPMOSトランジスタは第8の端子を構成し、第2のNMOSトランジスタと第2のPMOSトランジスタのゲートは共通に接続され、かつ、フローティング状態にあることを特徴とするメモリセルを含む不揮発性半導体記憶装置。

(もっと読む)

不揮発性半導体記憶装置、不揮発性メモリアレイ、および不揮発性半導体記憶装置の製造方法

【課題】不揮発性半導体記憶装置の構造を簡便化する。

【解決手段】半導体基板20の上にゲート絶縁膜30を介してポリシリコンからなるフローティングゲート40が設けられている。フローティングゲート40の両側壁には、側壁絶縁膜50が設けられている。拡散層60は、半導体基板20内に設けられ、フローティングゲート40から所定の距離だけ離間している。拡散層70は、半導体基板20内に設けられ、チャネル領域のチャネル幅方向およびチャネル長さ方向においてフローティングゲート40とオーバーラップしている。フローティングゲート40と容量カップリングした拡散層70に高電圧を印加することによりフローティングゲート40に電子が注入される。

(もっと読む)

不揮発性ワンタイムプログラマブル及びマルチタイムプログラマブルメモリに組み込まれた集積回路

プログラム可能な不揮発性デバイスが、ソース/ドレイン領域の一部分に重なるFETゲートとして機能する浮遊ゲートを使用する。これにより、デバイス用のプログラム供給電圧が容量結合によって浮遊ゲートに付与され、デバイスの状態を変更する。本発明は、データ暗号化、リファレンス調整、製造ID、セキュリティID及び他の多くのアプリケーションなどの各環境において使用できる。  (もっと読む)

(もっと読む)

メモリーセル、及びデータ記録方法

本発明は、少なくとも一のビット・データを記憶するメモリーセル(10)に関する。当該メモリーセルは、少なくとも二つの電気的接続(40、130)と、少なくとも一のポテンシャル井戸(200)を有するバンド曲線(EL)を伴う半導体構造(11)で構成されている。供給電圧(Us=Uspeis)を二つの電気的接続へ印加することによってポテンシャル井戸が電荷担体で帯電された状態が増大し、放電電圧(Us=Usperr)を印加することによって減少するほか、維持電圧(Us=Ubei)を印加することによってこの状態が維持されて、それぞれ帯電したポテンシャル井戸の状態がメモリーセルのビット・データ片を決定する。本発明によれば、この半導体構造が空間電荷ゾーン(Wn)を有しており、ポテンシャル井戸が半導体ヘテロ接合(80)によって形成されている。この半導体ヘテロ接合と空間電荷ゾーンは、維持電圧が印加されている場合は空間電荷ゾーン内に、供給電圧が印加されている場合は空間電荷ゾーンの周縁もしくは外に、放電電圧が印加されている場合は空間電荷ゾーン内に、半導体ヘテロ接合が位置するように、空間的に相対的な配置がなされている。 (もっと読む)

半導体装置

【課題】特に、横方向および斜め方向からの光の進入を低減でき、特性の変動が抑制された半導体装置を提供する。

【解決手段】本発明の半導体装置は、半導体層10に設けられた半導体素子と、

前記半導体素子の周囲に設けられた遮光壁50と、

前記半導体素子に電気的に接続された配線層26であって、前記遮光壁50の設けられていない開孔52から該遮光壁50の外側に延伸された配線層26と、を含み、

前記配線層26は、前記開孔52に位置している第1部分26Aと、該開孔の外側に位置し該第1部分26Aと比して大きい幅を有する第2部26B分と、を含むパターンを有し、

前記第2部分26Bの幅は、前記開孔52の幅と同一以上の幅である。

(もっと読む)

21 - 40 / 41

[ Back to top ]