Fターム[5F083EP60]の内容

半導体メモリ (164,393) | EPROM、EEPROMの構造 (21,423) | 絶縁膜 (4,144) | 積層ゲートを覆う多層絶縁膜(平坦化膜を除く) (33)

Fターム[5F083EP60]に分類される特許

1 - 20 / 33

半導体記憶装置及びその製造方法

【課題】メモリセルの高集積化を図ることができる半導体記憶装置及びその製造方法を提供する。

【解決手段】実施形態に係る半導体記憶装置は、半導体基板上に設けられた複数本の第1積層体と、前記複数本の第1積層体が配置された領域の外側に配置された第2積層体と、前記第1積層体及び前記第2積層体を覆う層間絶縁膜と、を備える。前記第1積層体と前記第2積層体との距離は、隣り合う前記第1積層体間の距離よりも長く、前記層間絶縁膜における前記第1積層体の相互間には第1の空隙が形成されており、前記層間絶縁膜における前記第1積層体と前記第2積層体との間には第2の空隙が形成されている。そして、前記第2の空隙の下端は、前記第1の空隙の下端よりも上方に位置している。

(もっと読む)

半導体装置及びその製造方法

【課題】半導体装置の製造工程を増加させることなく絶縁破壊耐性に優れた信頼性に懸念のない、小さな占有面積で所期の容量を確保する容量密度の高いパスコンを備えた半導体装置を実現する。

【解決手段】パスコンについて、第1の容量絶縁膜が、記憶素子のトンネル絶縁膜と共に第1の絶縁膜23で形成され、下部電極である第1の電極26が、記憶素子の浮遊ゲート電極25と共にドープト・アモルファスシリコン膜24(結晶化されたもの)で形成され、第2の容量絶縁膜が、周辺回路の5Vのトランジスタのゲート絶縁膜と共に第2の絶縁膜33で形成され、上部電極である第2の電極37が、記憶素子の制御ゲート電極36及び周辺回路のトランジスタのゲート電極41と共に多結晶シリコン膜34で形成される。

(もっと読む)

不揮発性半導体記憶装置

【課題】微細化した場合でもメモリセルの絶縁耐圧を確保し精密なしきい値分布を制御可能なセル構造を実現する。

【解決手段】半導体基板Sの表面層に形成された複数の素子分離絶縁膜DIと、素子分離絶縁膜DIに画定された複数の素子領域AAと、トンネル酸化膜10を介して半導体基板S上に形成された電荷蓄積層FGとゲート絶縁膜20を介して電荷蓄積層FG上に形成された制御ゲートCGとをそれぞれ含む複数のゲート構造と、前記ゲート構造直下の半導体基板Sの表面層を間に挟むように素子領域AAに形成された複数の不純物拡散層IDLと、前記ゲート構造の間を埋め込むように酸化シリコンで形成された絶縁膜60と、前記ゲート構造の側壁に接するように窒化シリコンで形成された絶縁膜40と、を備える不揮発性半導体記憶装置において、ゲート絶縁膜40の底面を、電荷蓄積層FGの高さの少なくとも半分以上半導体基板Sの表面から離隔させる。

(もっと読む)

半導体装置の製造方法

【課題】不揮発性半導体記憶装置の周辺回路領域において用いられる高耐圧トランジスタの特性及び信頼性を向上させることのできる半導体装置の製造方法を提供する。

【解決手段】半導体装置の製造方法は、シリコン基板3に周辺回路の高耐圧トランジスタHVTr用のゲート絶縁膜29を形成する工程と、ゲート絶縁膜29上にゲート電極HVGを形成する工程と、ゲート電極HVGの両側部のシリコン基板3上に位置するゲート絶縁膜29を剥離する工程と、不純物拡散領域30を形成する工程と、ゲート電極HVG及び不純物拡散領域30の表面に亘りシリコン酸化膜を堆積する工程と、シリコン酸化膜をエッチングしてゲート電極HVGの側壁部に形成されるとともに、シリコン基板3表面に延長するようにスペーサ22を形成する工程と、スペーサ22の表面にシリコン窒化膜23を形成する工程とを備える。

(もっと読む)

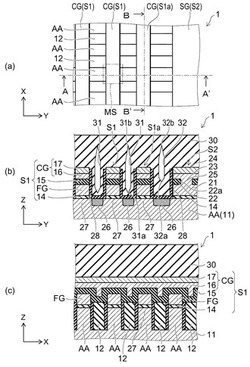

不揮発性半導体記憶装置及びその製造方法

【課題】動作信頼性を向上させる不揮発性半導体記憶装置及びその製造方法を提供する。

【解決手段】基板100上に形成された蓄積層105と蓄積層上に形成された制御ゲート電極107を備えた第1電極MTと、基板100上に形成された第2電極ST2及び第3電極ST2と、ゲート長方向に沿って対向する第2電極と第3電極ST2との側壁及び基板100上に形成された第2絶縁膜112と、第2、第3ゲート電極ST2間に埋設された第1絶縁膜113と、第2電極ST2及び第1電極MT間に埋設された第2絶縁膜109、110と、第1ゲート電極MT、第2ゲート電極ST2、第3ゲート電極ST2、及び第1、第2絶縁膜上113、112にそれぞれ形成され、且つ第1絶縁膜113における水素原子の拡散を防止する第3絶縁膜114とを具備する。

(もっと読む)

フラッシュメモリ、およびその製造方法

【課題】 潜在的な不良を抱えたメモリセルトランジスタを含み、半導体基板とゲート電極の間またはゲート電極内に異物が存在する異常構造のメモリセルトランジスタを除去可能なフラッシュメモリ、およびその製造方法を提供する。

【解決手段】 本発明は、半導体基板としてのシリコン基板1上に、上面が平坦な正常構造の正常ゲート電極G1と、上面の少なくとも一部に突起部8aを有する異常構造の異常ゲート電極G2とが配置されたフラッシュメモリにおいて、正常ゲート電極G1は、第一の拡散層3に接続される第一のコンタクト電極30とビット線16とを接続するビア15と電気的に分離され、異常ゲート電極G2は、ビア15と、異常ゲート電極G2上面の突起部8aにおいて電気的に接続されている。

(もっと読む)

半導体記憶装置

【課題】ゲート絶縁膜の劣化が抑制され、また、書き込み効率の向上化が図られる半導体記憶装置を提供する。

【解決手段】素子分離領域61によって挟まれた半導体基板1の領域に素子形成領域が形成されている。素子分離領域61では、所定の深さのトレンチ10にシリコン酸化膜11が充填されている。消去ゲート電極54は、シリコン酸化膜11の内部に埋め込まれる態様で、素子分離領域61内に形成されている。素子形成領域の上には、ゲート酸化膜6を介在させてフローティングゲート電極51が形成され、さらに、その上にONO膜17を介在させてコントロールゲート電極52が形成されている。隣接するフローティングゲート電極51とフローティングゲート電極51との間には、消去ゲート電極54を覆うように、絶縁膜16が形成されている。

(もっと読む)

半導体装置の製造方法及び半導体装置

【課題】一度の酸化処理でONO膜の上側酸化膜を下側酸化膜よりも厚く形成することができるミラービットの半導体装置の製造方法を提供する。

【解決手段】基板10上に第1酸化膜11、この第1酸化膜11よりも膜厚が薄い窒化膜12、第1酸化膜11よりも膜厚が薄い第2酸化膜13、及びゲート電極14を積層する工程と、第1酸化膜11の端部及び第2酸化膜13の端部を除去して窒化膜12を一部露出する工程と、第1酸化膜11が除去された基板10上に第3酸化膜15を形成すると同時に、窒化膜12の露出部分を酸化して第4酸化膜16を形成し且つゲート電極14の周囲に第5酸化膜17を形成して、第4酸化膜16と第5酸化膜17とが一体化した、第3酸化膜15よりも厚い酸化膜を形成する工程と、第3酸化膜15と第4酸化膜16との間に電荷蓄積層18aを形成する工程と、をこの順に行う。

(もっと読む)

半導体記憶装置の製造方法

【課題】信頼性が高く、コスト増加を抑制した半導体記憶装置の製造方法を提供する。

【解決手段】ワードラインWL及び選択トランジスタSTを加工する工程と、ワードラインWL間、選択トランジスタST間、及び選択トランジスタSTとこの選択トランジスタに隣接するワードラインWL1との間に、上面が制御ゲート電極5の上面より低くなるようにレジスト膜10を形成する工程と、ワードラインWL間を埋め込むように絶縁膜11を形成する工程と、レジスト膜10を除去して空洞12を形成する工程と、選択トランジスタST間を埋め込む絶縁膜14を形成する工程と、絶縁膜6を除去し、電極5の上面を露出する工程と、電極5のシリサイド化を行う工程と、を備える。

(もっと読む)

不揮発性半導体記憶装置の製造方法および不揮発性半導体記憶装置

【課題】積層ゲート電極間に自己整合的なコンタクト構造を適用した場合に、側壁絶縁膜によるゲート絶縁膜の保護性能を保持して信頼性を向上できるようにする。

【解決手段】RTO膜11が、制御ゲート電極CG、ゲート間絶縁膜7、浮遊ゲート電極FGの側壁に沿って形成されている。シリコン窒化膜13がゲート電極MG1、MG2の上面および側面、RTO膜11の上端11aおよび側面を覆うように形成されている。コンタクトホールDHが、シリコン窒化膜13の外面に沿ってシリコン基板2の上面上に至るまで形成されている。

(もっと読む)

半導体素子及びこの半導体素子を用いた装置

【課題】高速な書込み及び消去動作を比較的低電圧で行い、かつ書換え劣化を抑えることで、メモリウインドウが大きく信頼性の高いメモリ素子を、低コストで提供する。

【解決手段】メモリ素子は、絶縁基板上に設けられた半導体層と、P型の導電型を有する第1の拡散層領域及び第2の拡散層領域と、第1の拡散層領域と第2の拡散層領域との間のチャネル領域を覆い、チャネル領域より電荷を注入され得る電荷蓄積膜と、電荷蓄積膜をはさんでチャネル領域とは反対側に位置するゲート電極とを有する。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】ゲート電極膜とコンタクトプラグとの接触を避け且つ距離の短縮が可能な半導体装置及び半導体装置の製造方法を提供する。

【解決手段】半導体基板5と、半導体基板5の表面上に、ゲート絶縁膜11、浮遊ゲート膜13、ゲート間絶縁膜15、及び、上側部に切欠き部18が形成された制御ゲート膜16が順次積層されたゲート電極膜と、制御ゲート膜16の切欠き部18に形成されたスペーサ23と、ゲート電極膜、スペーサ23及び半導体基板5の表面を覆うよう形成され、スペーサ23と被エッチング性の異なる層間絶縁膜27と、ゲート電極膜に隣接して、層間絶縁膜27を貫通して形成されたコンタクトプラグ29とを備える。

(もっと読む)

半導体装置の製造方法および半導体装置

【課題】電極間絶縁膜に生じるシームなどの埋込み欠陥の露出を抑制できるようにしてゲート電極間ショートを防止できるようにする。

【解決手段】多結晶シリコン層6bを種として選択成長された選択成長部6cがシリコン酸化膜8、9上に突出して張り出して形成される。その後、多結晶シリコン層6b、6cをシリサイド化することで、金属反応領域を拡大することができ、制御ゲート電極CG(ワード線WL)を低抵抗化することができる。

(もっと読む)

フラッシュメモリー素子の製造方法

【課題】素子分離膜の形成時または層間絶縁膜の形成時にボイドの発生を防止することができるフラッシュメモリー素子の製造方法を提供する。

【解決手段】本発明による方法は、半導体基板上に絶縁膜パターンを形成する段階と、絶縁膜パターンをマスクで半導体基板を蝕刻してトレンチを形成する段階と、トレンチを含んだ半導体基板上に第1絶縁膜を形成する段階と、第1絶縁膜が形成された半導体基板上に湿式蝕刻工程を進行する段階と、半導体基板上に第2絶縁膜を形成する段階と、第1及び第2絶縁膜に平坦化工程を進行する段階及び絶縁膜パターンを除去する段階と、を含むことを特徴とする。

(もっと読む)

半導体記憶装置及びその製造方法

【課題】

高信頼性で高歩留まりの半導体装置及びその製造方法を提供する。

【解決手段】

半導体基板10上に形成された第1ゲート電極19と、この第1ゲート電極の一方の側

面下の半導体基板中に形成された第1拡散層20と、第1ゲート電極の他方の側面下の半

導体基板中に形成された第2拡散層18と、この第2拡散層の上に側面が形成された第2

ゲート電極13と、第1ゲート電極と第2ゲート電極間を埋め込み、第1拡散層上では、

第1ゲート電極と第2ゲート電極間を埋め込む厚さよりも薄く形成され、窒素を主成分と

しない第1絶縁膜25と、この第1絶縁膜上に形成された第2絶縁膜26と、この第2絶

縁膜上に形成され、この第2絶縁膜とは主成分が異なる層間絶縁膜27と、第1拡散層に

接続され、第1絶縁膜、第2絶縁膜及び層間絶縁膜中に形成されたコンタクト電極23と

を有する半導体装置である。

(もっと読む)

半導体装置及びその作製方法

【課題】外部から局所的に圧力がかかっても破損しにくい半導体装置を提供する。また、外部からの局所的押圧による非破壊の信頼性が高い半導体装置を歩留まり高く作製する方法を提供する。

【解決手段】単結晶半導体領域を用いて形成された半導体素子を有する素子基板上に、有機化合物または無機化合物の高強度繊維に有機樹脂が含浸された構造体を設け、加熱圧着することにより、有機化合物または無機化合物の高強度繊維に有機樹脂が含浸された構造体及び素子基板が固着された半導体装置を作製する。

(もっと読む)

不揮発性メモリ素子及びその製造方法

【課題】高集積化が容易で、且つ高い信頼性を有する不揮発性メモリ素子及びその製造方法を提供する。

【解決手段】本発明の不揮発性メモリ素子は、複数の第1半導体層、複数の第2半導体層、複数の第1ストレージノード、及び複数の第1制御ゲート電極を備える。複数の第1半導体層は、基板上に積層され、複数の第2半導体層は、複数の第1半導体層の間にそれぞれ介在して複数の第1半導体層の間に複数の第1トレンチを限定するように複数の第1半導体層の一端からリセスされ、複数の第1ストレージノードは、複数の第1トレンチの内部の第2半導体層の表面上に提供され、複数の第1制御ゲート電極は、複数の第1トレンチを満たすように複数の第1ストレージノード上に形成される。

(もっと読む)

SONOSフラッシュメモリ素子及びその形成方法

【課題】SONOSフラッシュメモリ素子及びその製造方法を提供する。

【解決手段】本発明は、素子分離領域によって限定された活性領域を有する基板と、前記活性領域及び前記素子分離領域上に提供されたゲートラインと、前記ゲートラインと交差する活性領域上にのみ提供されたメモリ膜を含み、前記活性領域上のゲートラインの上部面は前記素子分離領域上のゲートラインの上部面より低く、前記活性領域上のゲートラインの下部面は前記素子分離領域上のゲートラインの下部面より低い非揮発性メモリ素子である。

(もっと読む)

半導体装置およびその製造方法

【課題】コンタクトプラグと半導体基板との間の接触面積を十分に確保できるようにする。

【解決手段】一対の選択ゲートトランジスタのゲート電極SG間に、シリコン窒化膜11を介してBPSG膜14が形成される。BPSG膜14の上面部14aの高さ位置は各ゲート電極SGの上面部SGaの高さ位置より高さHだけ高く形成される。BPSG膜14上、ゲート電極SG上、シリコン窒化膜11上にシリコン窒化膜12が形成される。シリコン窒化膜12がシリコン窒化膜11の内側下方に延出することが無いので、一対のシリコン窒化膜11で挟まれる領域において、コンタクトホール径がシリコン窒化膜12に当接して小さくなることが無くなる。

(もっと読む)

不揮発性半導体記憶装置及びその製造方法

【課題】バーズ・ビークの形成が抑制されて素子特性のばらつきが抑制された信頼性の高い不揮発性半導体記憶装置を提供する。

【解決手段】半導体基板201と、半導体基板201表面部のチャネル領域202上に形成された第1の絶縁膜204と、第1の絶縁膜204上に形成された電荷蓄積層205と、電荷蓄積層205上に形成された第2の絶縁膜206と、第2の絶縁膜206上に形成された制御ゲート電極207と、電荷蓄積層205の底面、表面及び側面に形成されたSi−N結合を含む第3の絶縁膜208と、を備える

(もっと読む)

1 - 20 / 33

[ Back to top ]