Fターム[5F083ER05]の内容

半導体メモリ (164,393) | EPROM、EEPROMの書込、消去方法 (6,790) | キャリア制御 (6,786) | 電子注入 (2,236) | ドレイン側から注入 (159)

Fターム[5F083ER05]に分類される特許

1 - 20 / 159

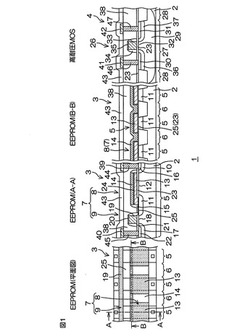

半導体装置および半導体装置の製造方法

【課題】トンネルウィンドウやセレクトゲートの加工寸法のばらつき、およびセレクトゲートのアライメント精度を考慮する必要がなく、セルサイズを小さくすることができる半導体装置およびその製造方法を提供すること。

【解決手段】不揮発性メモリセル7を半導体基板2上に選択的に備える半導体装置1が製造される。この製造方法は、ゲート絶縁膜23上において不揮発性メモリセル7用のアクティブ領域5に、セレクトゲート19を選択的に形成する工程と、セレクトゲート19に対して自己整合的に導入することによってn型トンネル拡散層11を形成する工程と、ゲート絶縁膜23の一部セレクトゲート19に対して自己整合的に除去し、その後の熱酸化によりトンネルウィンドウ25を形成する工程とを含む。

(もっと読む)

半導体装置

【課題】メモリセルの動作を従来よりも高速化できる半導体装置を提供する。

【解決手段】フローティングゲートFGとコントロールゲートCG、第1導電型ソース13s及び第1導電型ドレイン13dを有する第1導電型MOSトランジスタ13と、前記フローティングゲートFGと前記コントロールゲートCG、第2導電型ソース14s及び第2導電型ドレイン14dを有する第2導電型MOSトランジスタ14と、前記第1導電型ドレイン13d及び前記第2導電型ドレイン14dに接続される第1のソース/ドレイン11bと、第2のソース/ドレイン11aと、ゲートを有する選択トランジスタ11と、前記第1導電型ソースに接続される第1電源線VpLと、前記第2導電型ソースに接続される第2電源線VnLと、前記選択トランジスタ11の第2のソース/ドレイン11aに接続されるビット線BLと、前記選択トランジスタ11のゲートに接続されるワード線WLと、を有する。

(もっと読む)

半導体記憶装置及び半導体記憶素子

【課題】素子の面積を増大させることなく、かつ、コントロールゲート電圧を制御しなくとも、低電圧で書き込み量を大幅に増やすことが可能であり、また、安定して十分な書き込みを行うことが可能である不揮発性半導体装置を提供すること。

【解決手段】ドレインアバランシェホットエレクトロンにより書き込みを行う半導体記憶素子であって、第1導電型の半導体基板に形成された第2導電型の第1の半導体層と、前記第1の半導体層上に絶縁膜を介して設けられたフローティングゲートと、前記フローティングゲート下部の前記第1の半導体層の表面に形成されたチャネル領域と、前記チャネル領域に接触するように前記第1の半導体層上に設けられた第1導電型のソース領域及びドレイン領域とを有するMOSトランジスタであって、前記チャネル領域が2種類以上のキャリア濃度の分布をもつ半導体記憶素子とした。

(もっと読む)

不揮発性半導体記憶装置

【課題】高速で動作し得る不揮発性半導体記憶装置を提供する。

【解決手段】選択トランジスタとメモリセルトランジスタMTとを有するメモリセルMCがマトリクス状に配列されて成るメモリセルアレイ10と、ビット線BLの電位を制御する列デコーダ12と、第1のワード線WL1の電位を制御する電圧印加回路14と、第2のワード線WL2の電位を制御する第1の行デコーダ16と、ソース線SLの電位を制御する第2の行デコーダ18とを有し、列デコーダは電圧印加回路及び第2の行デコーダより耐圧の低い回路により構成されており、第1の行デコーダは電圧印加回路及び第2の行デコーダより耐圧の低い回路により構成されている。ビット線と第2のワード線とが高速で制御され得るため、メモリセルトランジスタに書き込まれた情報を高速で読み出すことができる。

(もっと読む)

半導体装置の製造方法

【目的】幅寸法が異なるワード線に対する書き込み電圧の設定の適正化を図ることが可能な半導体装置の製造方法を提供することを目的とする。

【構成】実施形態の半導体装置の製造方法は、線幅の異なる複数のワード線の組が繰り返し配置された半導体記憶装置における全ページのそれぞれの書き込み電圧を取得する工程と、すべての組における前記複数のワード線のうちの第1のワード線に対応するページの書き込み電圧の第1の平均値を演算する工程と、すべての組における前記複数のワード線のうちの、前記第1のワード線と隣り合う第2のワード線に対応するページの書き込み電圧の第2の平均値を演算する工程と、各組の第1のワード線に対応するページに対する書き込み電圧を前記第1の平均値に設定し、各組の第2のワード線に対応するページに対する書き込み電圧を前記第2の平均値に設定する工程と、を備えた。

(もっと読む)

不揮発性半導体記憶装置

【課題】メモリブロックを縮小化可能な不揮発性半導体記憶装置を提供する。

【解決手段】一態様に係る不揮発性半導体記憶装置は、半導体基板、メモリストリング、複数の第1導電層、第2導電層、及び第3導電層を有する。メモリストリングは、半導体基板に対して垂直方向に直列接続された複数のメモリセル、ダミートランジスタ、及びバックゲートトランジスタを有する。複数の第1導電層は、メモリセルのゲートと電気的に接続されている。第2導電層は、ダミートランジスタのゲートと電気的に接続されている。第3導電層は、バックゲートトランジスタのゲートと電気的に接続されている。第2導電層は、第3導電層と短絡している。

(もっと読む)

プリント不揮発性メモリ

【課題】低コストで高スループットなプリント技術を使用した不揮発性メモリセルを提供する。

【解決手段】同一水平レベルにおいて所定の距離で離間している第1及び第2の半導体アイランドであって、第1の半導体アイランド2が制御ゲートを構成し、第2の半導体アイランド3がソース端子及びドレイン端子を構成する、当該第1及び第2の半導体アイランドと、第1の半導体アイランド2の少なくとも一部の上のゲート誘電体層4と、第2半導体アイランドの少なくとも一部の上のトンネリング誘電体層5と、ゲート誘電体層4とトンネリング誘電体層5の少なくとも一部の上のフローティングゲート7と、制御ゲート2並びにソース端子及びドレイン端子に電気的に接触する金属層と、を備える。一つの効果的な実施形態では、不揮発性メモリセルを、「全プリント」加工技術を使用して製造することができる。

(もっと読む)

半導体不揮発性メモリ装置

【課題】占有面積を増加することなくトンネル絶縁膜の劣化を抑制して高い信頼性を持った電気的書き換え可能な半導体不揮発性メモリ装置を得ることを目的とする。

【解決手段】ドレイン領域内のトンネル領域には、ドレイン領域と同一の電位に固定されたドレイン領域に比べて不純物濃度の低い第2導電型の領域と、不純物濃度の低い第1導電型の領域とを形成し、不純物濃度の低い第2導電型の領域と、不純物濃度の低い第1導電型の領域のそれぞれの上面に、フローティングゲート電極への電子注入用と電子引き抜き用のトンネル絶縁膜を独立して設けた。また、データ書き換え時に印加されるストレスが偏らないように、電子引き抜き用のトンネル絶縁膜に比べて電子注入用のトンネル絶縁膜の面積を大きくあるいは厚くした。

(もっと読む)

半導体不揮発性メモリ装置

【課題】占有面積を増加することなくトンネル絶縁膜の劣化を抑制して高い信頼性を持った電気的書き換え可能な半導体不揮発性メモリ装置を提供する。

【解決手段】フローティングゲート電極は、高い不純物濃度領域と低い不純物濃度領域とからなり、高い不純物濃度領域は、コントロールゲート絶縁膜と接する部分に配置し、低い不純物濃度領域はトンネル絶縁膜と接する領域に配置し、フローティングゲート電極のコントロールゲート絶縁膜と接する表面部分には微細凹凸を形成した。

(もっと読む)

半導体不揮発性メモリ装置

【課題】占有面積を増加することなくトンネル絶縁膜の劣化を抑制して高い信頼性を持った電気的書き換え可能な半導体不揮発性メモリ装置を提供する。

【解決手段】トンネル領域のエッジ近傍のトンネル絶縁膜上には、トンネル絶縁膜とは異なる材質の絶縁膜からなる電界緩和層を配置した。

(もっと読む)

半導体不揮発性メモリ装置

【課題】占有面積を増加することなくトンネル絶縁膜の劣化を抑制して高い信頼性を持った電気的書き換え可能な半導体不揮発性メモリ装置を提供する。

【解決手段】トンネル領域とフローティングゲート電極との間には、膜厚の異なる複数のトンネル絶縁膜を形成した。

(もっと読む)

半導体不揮発性メモリ装置

【課題】占有面積を増加することなくトンネル絶縁膜の劣化を抑制して高い信頼性を持った電気的書 き換え可能な半導体不揮発性メモリ装置を提供する。

【解決手段】トンネル絶縁膜の上部であって、トンネル領域のエッジ部近傍の領域には、フローティングゲート電極とガード絶縁膜を介してドレイン電極と同電位に固定されたトンネル領域エッジ部ガード電極を配置した。

(もっと読む)

半導体不揮発性メモリ装置

【課題】占有面積を増加することなくトンネル絶縁膜の劣化を抑制して高い信頼性を持った電気的書き換え可能な半導体不揮発性メモリ装置を得る。

【解決手段】第2導電型のトンネル領域のフローティングゲート電極のエッジ部の下部に、第1導電型の領域からなるフローティングゲート電極エッジの電界集中防止用領域を形成する。

(もっと読む)

半導体不揮発性メモリ装置

【課題】占有面積を増加することなくトンネル絶縁膜の劣化を抑制して高い信頼性を持った電気的書 き換え可能な半導体不揮発性メモリ装置を得る。

【解決手段】ドレイン領域内のトンネル領域とフローティングゲート電極領域との間には、トンネル絶縁膜が設けられており、トンネル領域のエッジ近傍のフローティングゲート電極の不純物濃度は、その他の箇所のフローティングゲート電極の不純物濃度に比べて低く設定した。

(もっと読む)

半導体不揮発性メモリ装置

【課題】占有面積を増加することなくトンネル絶縁膜の劣化を抑制して高い信頼性を持った電気的書 き換え可能な半導体不揮発性メモリ装置を得ることを目的とする。

【解決手段】電気的書き換え可能な半導体不揮発性メモリにおいて、第2導電型のドレイン領域内のトンネル領域と前記フローティングゲート電極領域との間には、トンネル絶縁膜が設けられており、前記フローティングゲート電極は第1導電型の導電体で形成されている電気的書き換え可能な半導体不揮発性メモリ装置。

(もっと読む)

半導体装置およびその製造方法

【課題】半導体基板の結晶性の悪化を招くことなく、素子分離トレンチの幅を小さくできる半導体装置の製造方法を提供する。

【解決手段】マスク用窒化膜51およびパッド酸化膜52からなるハードマスクを用いて、シリコン基板2がエッチングされることにより、素子分離トレンチ21が形成される。素子分離トレンチ21の内面に熱酸化法によりライナー酸化膜22が形成される。続いて、半導体基板2を窒素雰囲気中に配置して、半導体基板2が熱処理される。熱処理後に、エッチングにより、ライナー酸化膜22が薄膜化される。そして、HDP−CVD法により、絶縁物23が素子分離トレンチ21内に埋め込まれる。

(もっと読む)

半導体装置およびその製造方法

【課題】半導体基板上に形成されたFETのソース側のエクステンション領域の抵抗値を低減し、半導体装置の動作速度を向上することができる技術を提供する。

【解決手段】ゲート電極4dの側壁に、ゲート電極4dのゲート長方向の幅が異なる第1サイドウォール6wおよび第2サイドウォール6nをそれぞれ形成する。これにより、第1サイドウォール6wおよび第2サイドウォール6nの形状によって第1サイドウォール6wおよび第2サイドウォール6nの下部に自己整合的に形成されるエクステンション領域37、38の半導体基板SBの上面の幅をそれぞれ異なる長さで形成する。

(もっと読む)

半導体メモリおよびその製造方法

【課題】素子分離トレンチ内の絶縁膜のエッチングとアライメントトレンチ内の絶縁膜のエッチングとを、1つのマスクを用いて同時に行える構造の半導体メモリを提供する。

【解決手段】シリコン基板2には、メモリセル領域70およびアライメントマーク領域80が設定されている。メモリセル領域70には、シリコン基板2の表層部に、アクティブ領域30を分離する素子分離トレンチ21が形成されている。アライメントマーク領域80には、シリコン基板2の表層部に、マスク合わせのためのアライメントトレンチ82が形成されている。素子分離トレンチ21内には、素子分離トレンチ21間のアクティブ領域30が突出するように、絶縁物(酸化膜)23が素子分離トレンチ21の深さ方向途中まで埋め込まれている。一方、アライメントトレンチ82内には、絶縁物23がアライメントトレンチ82の深さ方向途中まで埋め込まれている。

(もっと読む)

半導体記憶装置

【課題】書き込み/消去の繰り返しによる信頼性の低下を抑制することが可能な半導体記憶装置を提供する。

【解決手段】半導体記憶装置は、ウェル上にトンネル絶縁膜を介して形成された浮遊ゲートに蓄積する電荷量を制御することにより電気的にデータを書き換え可能な複数のメモリセルを、有するメモリセルアレイと、ウェルに印加するための出力電圧を出力する出力端子と、入力電圧を昇圧して設定された電圧を出力端子に出力する第1のポンプ回路と、入力電圧を昇圧して設定された電圧を出力端子に出力し、第1のポンプ回路よりも高い電圧を出力可能な第2のポンプ回路と、第1のポンプ回路または第2のポンプ回路の少なくとも何れか一方を昇圧動作させるためのアシスト信号を出力するポンプ切替検知回路と、出力電圧の目標電圧を設定するための設定値に基づいて、第1のポンプ回路および第2のポンプ回路の目標電圧を設定する消去パルス制御回路と、を備える。

(もっと読む)

半導体装置

【課題】不揮発性メモリを構成するメモリセルのサイズを縮小できる技術を提供する。

【解決手段】本発明では、ソース線S1がメモリセルMC1AとメモリセルMC8Aで共通となっている。これにより、メモリセルMC1AやメモリセルMC8Aごとに電気的に独立したソース線を設ける必要がなく、メモリセルのサイズを縮小化することができる。具体的に、共通するソース線S1は、ビット線D1やビット線D8と並行するように配置されているのではなく、選択ゲート線CGL1やメモリゲート線MGL1と並行するように延在している。これにより、メモリセルMC1A〜メモリセルMC8A間の間隔を狭めることができるので、メモリセルアレイ全体の占有面積を縮小化することができる。このソース線S1は、メモリセルMC1B〜メモリセルMC8Bとも共通化されている。

(もっと読む)

1 - 20 / 159

[ Back to top ]