Fターム[5F083ER06]の内容

半導体メモリ (164,393) | EPROM、EEPROMの書込、消去方法 (6,790) | キャリア制御 (6,786) | 電子注入 (2,236) | ソース側から注入 (122)

Fターム[5F083ER06]に分類される特許

121 - 122 / 122

フラッシュメモリデバイス

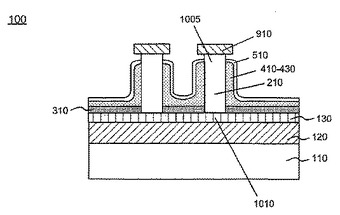

メモリデバイス(100)は、導電構造(210)、複数の誘電層(410−430)、及び、制御ゲート(510)を含む。誘電層(410−430)は導電構造(210)の周りに形成され、制御ゲート(510)は誘電層(410−430)上に形成される。導電構造(210)の一部はメモリデバイス(100)のドレイン領域(1005)として機能し、また、誘電層(410−430)の少なくとも1つは、メモリデバイス(100)の電荷蓄積構造として機能する。誘電層(410−430)は、酸化物−窒化物−酸化物層を含む。  (もっと読む)

(もっと読む)

不揮発性メモリおよびその製造方法

トランジスタの制御ゲート(28)およびウェル領域(12)に、それぞれ、第1および第2の電圧を印加するステップを含む不揮発性メモリのトランジスタ(10)の電荷蓄積場所から放電するための方法。第1の電圧はトランジスタの制御ゲートに印加され、制御ゲートは、トランジスタの選択ゲート(18)に隣接して位置する一部を少なくとも有する。トランジスタは、制御ゲートの下に位置するトランジスタの構造の誘電体(22,26)内に配置されたナノクラスタ(24)を有する電荷蓄積場所を含む。最後に、第2の電圧が、制御ゲートの下に位置するウェル領域(12)に印加される。第1の電圧および第2の電圧の印加により、電荷蓄積場所のナノクラスタから電子を放出するために前記構造の両端に電圧差が発生する。  (もっと読む)

(もっと読む)

121 - 122 / 122

[ Back to top ]