Fターム[5F083ER06]の内容

半導体メモリ (164,393) | EPROM、EEPROMの書込、消去方法 (6,790) | キャリア制御 (6,786) | 電子注入 (2,236) | ソース側から注入 (122)

Fターム[5F083ER06]に分類される特許

81 - 100 / 122

半導体装置およびその製造方法

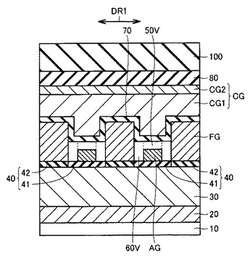

【課題】 閾値変調が抑制され、かつ、デバイス特性の安定性や生産性を確保しながら、フローティングゲート電極−アシストゲート電極間の絶縁性を向上させた半導体装置およびその製造方法を提供する。

【解決手段】 半導体装置は、半導体基板10と、半導体基板10の主表面上にゲート絶縁膜42を介して複数形成された電荷蓄積用のフローティングゲート電極FGと、半導体基板10の主表面上における複数のフローティングゲート電極FG間に形成されたアシストゲート電極AGと、フローティングゲート電極FG上からアシストゲート電極AG上にONO膜である絶縁膜70を介して設けられるコントロールゲート電極CGとを備え、複数のフローティングゲート電極FG間にエアギャップ50Vが形成され、フローティングゲート電極FG−アシストゲート電極AG間にエアギャップ60Vが形成されている。

(もっと読む)

不揮発性半導体記憶装置

【課題】 書き込み動作の効率低下を防ぐことが可能な不揮発性半導体記憶装置を提供する。

【解決手段】 不揮発性半導体記憶装置100は、付加トランジスタ2と、不揮発的にデータを記憶し、かつ、付加トランジスタ2がオン状態の場合にドレイン電流Idsを流すことが可能となるメモリトランジスタ1と、メモリトランジスタ1および付加トランジスタ2に供給する電圧を発生する電圧発生回路31と、メモリトランジスタ1に対する書き込み時、電圧発生回路31を制御することにより、付加トランジスタ2をオン状態とした後、電圧発生回路31が発生する付加トランジスタ2のゲート電圧Vg_bが付加トランジスタ2の閾値電圧に対して等しいかまたは所定値未満だけ上回る状態を第1の所定期間維持できるように付加トランジスタ2のゲート電圧Vg_bを変更する制御部32とを備える。

(もっと読む)

半導体装置

【課題】 不揮発性メモリに対するリフレッシュ動作を比較的簡単に実現する。

【解決手段】 フラッシュメモリ(1)は、電気的に書込み及び消去が可能にされる複数の不揮発性メモリセル(2)を備えるメモリアレイ(3)と、制御回路(5)とを有する。制御回路は、リフレッシュサイクルを起動するリフレッシュタイマー回路(7A)と、電源電圧が供給されているときリフレッシュサイクル毎にリフレッシュアドレスを生成するロウアドレスカウンタ(8A)とを有する。制御回路は、所定の時間間隔でアドレスを巡回させてリフレッシュサイクルを起動する。そして、制御回路は、リフレッシュ対象となる不揮発性メモリセルから記憶情報を読出し、消去動作を行わずに、読出した記憶情報を同一の不揮発性メモリセルに書込むための制御を行うから、例えば記憶情報の書込み対象となる別の不揮発性メモリセルを特定するようなウエアレベリング処理を行うことを要しない。

(もっと読む)

原子層蒸着工程を用いたシリコンリッチナノクリスタル構造物の形成方法及びこれを用いた不揮発性半導体装置の製造方法

【課題】原子層蒸着工程を用いたシリコンリッチナノクリスタル構造物の形成方法、及びこれを用いた不揮発性半導体装置の製造方法が開示される。

【解決手段】対象体上へ第1シリコン化合物を含む第1ガスを提供して対象体上にシリコンリッチ化学吸着層を形成する。シリコンリッチ化学吸着層上へ酸素を含む第2ガスを提供して対象体上にシリコンリッチ絶縁層を形成した後、シリコンリッチ絶縁層上に第2シリコン化合物を含む第3ガスを提供して前記シリコンリッチ絶縁層上にナノクリスタル層を形成する。このような過程を反復的に行って対象体上に複数のシリコンリッチ絶縁層及びシリコンナノクリスタル層を有するシリコンリッチナノクリスタル構造物を形成する。原子層蒸着工程を通じてシリコンリッチ絶縁層とシリコンリッチナノクリスタル層を含んで高いシリコン含量と優れた段差塗布性を有するシリコンリッチナノクリスタル構造物を形成することができる。

(もっと読む)

不揮発性集積メモリデバイスのセルをプログラムするためのシステムと方法

不揮発性集積メモリデバイス内の、プログラムしにくい記憶素子を迅速かつ効率的にプログラムするシステムと方法が提供される。第1のレベルに制限される記憶素子を流れる電流により、多数の記憶素子が同時にプログラミング処理を受ける。これら記憶素子の一部が所定の状態に達すると、それらはプログラムされるセルのセットから取り除かれ、引き続きプログラムされる素子に関する電流制限が引き上げられる。これらのプログラムしにくい電流レベルは、第2のさらに高い限界に引き上げられるか、または無制限となる。別の態様によれば、プログラミング動作中、セルに許される電流限界はセルがプログラムされる目標状態に応じて決まる。  (もっと読む)

(もっと読む)

不連続な記憶要素群を含んだ電子デバイス

電子デバイスは、トレンチ(22、23)内に位置する不連続な記憶要素群(64)を含んでいる。この電子デバイスはトレンチを含む基板(12)を有し、このトレンチは壁部及び底部を含み且つ基板の主表面から延在している。電子デバイスはまた、不連続な記憶要素群を含んでおり、その第1部分は少なくともトレンチ内にある。電子デバイスは更に第1のゲート電極を含んでおり、第1のゲート電極と第1のトレンチの壁部との間に、不連続な記憶要素群の部分の少なくとも一部が位置している。この電子デバイスは更に、第1のゲート電極及び基板の主表面の上に第2のゲート電極を含んでいる。  (もっと読む)

(もっと読む)

ナノクリスタルとトレンチを含むマルチビット不揮発性メモリ装置及びその製造方法

【課題】2ビット貯蔵が可能な不揮発性メモリ集積回路装置を提供する。

【解決手段】半導体基板、半導体基板内に形成されたソース/ドレーン、ソース/ドレーンの間に形成されたステップリセスチャネル、ステップリセスチャネル領域上の多数の電荷貯蔵ナノクリスタルを含むトラップ構造物及びトラップ構造物上のゲートを含む。

(もっと読む)

トレンチ内にナノ結晶記憶要素を含むプログラム可能構造

記憶セルは、トレンチを画成する半導体基板、トレンチの内側を覆う底部誘電体、及び底部誘電体上の電荷格納層を有している。電荷格納層は複数の不連続な記憶要素(DSE)を含んでいる。制御ゲート及び頂部誘電体がDSEを覆っている。記憶セルはトレンチの下にソース/ドレイン領域を有している。DSEはシリコンナノ結晶であってもよく、制御ゲートはポリシリコンであってもよい。制御ゲートは半導体基板の上面の下方までリセス化され、最も上側のDSEは縦方向で制御ゲートの上面に揃えられている。記憶セルは、トレンチの側壁に隣接するシリコンナノ結晶に横方向で揃えられ、且つ最も上側のシリコンナノ結晶から基板の上面まで縦方向に延在している酸化物ギャップ構造を含んでいる。DSE群は少なくとも2つのプログラム可能な注入領域を含んでいる。  (もっと読む)

(もっと読む)

不連続蓄積素子を含む電子デバイスを形成するための方法

電子デバイスを形成するためのプロセスは、基板(12)内に第1のトレンチ(22、23)を形成する段階を含むことができ、該トレンチは、壁部及び底部を含み且つ基板の主要面から延びる。プロセスはまた、不連続蓄積素子(64)を形成する段階と、不連続蓄積素子のうちの第1の不連続蓄積素子が第1のゲート電極(92)とトレンチの壁部との間に位置するようにトレンチ内に第1のゲート電極を形成する段階とを含むことができる。プロセスは更に、基板の主要面の上に重なる不連続蓄積素子を除去する段階を含むことができる。プロセスは更に、第1のゲート電極及び基板の主要面の上に重なる第2のゲート電極を形成する段階を含むことができる。 (もっと読む)

不揮発性記憶素子の制御方法

【課題】 ソース・ドレインに挟まれた1つのメモリセルに4ビット以上のメモリ領域を有する不揮発性記憶素子へのデータ書込を精度よく行う。

【解決手段】 不揮発性記憶素子100は、シリコン基板102に離間して設けられた第1および第2の不純物拡散領域160aおよび160bの間に並行配置されたn個(nは4以上の偶数)のコントロールゲート114〜117、およびそれらのコントロールゲートとそれぞれ対を成すメモリ領域106a〜106dを含むメモリセルを含む。不揮発性記憶素子100の制御方法は、n個のコントロールゲート114〜117を左右2分割し、電子注入対象のメモリ領域から遠い方の不純物拡散領域に低電圧、近い方の不純物拡散領域に高電圧を印加するとともに、電子注入対象のメモリ領域と対を成すコントロールゲートに他のコントロールゲートよりも高電圧を印加する工程を含む。

(もっと読む)

フラッシュメモリデバイスにおける接点形成方法

【課題】フラッシュメモリデバイスにおけるビット線とローカル配線との間の接点を形成する際に、有効な重ね合わせ割当量を増加させる方法を提供する。

【解決手段】酸化物誘電体層を堆積する前に、ローカル配線の最上部が露出した平坦面に、ハードマスク層を形成する工程を含んでいる。ハードマスク18の開口部は、最上部で露出したローカル配線との接点の位置を規定する。エッチマスクは、ビット線トレンチを規定するために、層間絶縁層上に形成される。ハードマスク18の開口部を通過するように、ローカル配線の最上部に対し下方に、例えば異方エッチングを行う。この工程で、ハードマスク及びエッチマスク層双方の開口部が重複する部分のみで、接点が確立される。特に、接続孔は、ビット線を規定するエッチマスク直下にのみ形成されるので、形成されるビット線トレンチは、均一な幅になり、かつ隣接するビット線と均一な間隙になる。

(もっと読む)

ビット線ソフト・プログラミング(BLISP)のための方法及び集積回路

【課題】BLISP方法を含む、連続した主題のビット線に適用して、ビット線上の過剰消去された浮遊ゲート・メモリセルの効率的な収束を与える集積回路(105)のためのソフト・プログラム方法を提供する。BLISP方法は、バルク・ソフト・プログラミング方法と比較して低電流消費に適応されている。

【解決手段】ソフト・プログラムは適合した選択されたビット線及び欠陥ビット線を置換える冗長ビット線に適用される。第1メモリ配列(110)内の欠陥ビット線は、ソフト・プログラムの際、使用不可にされて、第2メモリ配列(170)内に配置された対応する冗長ビット線により置換えられて、ソフト・プログラムが欠陥ビット線へ適用されないようにする。欠陥ビット線へのソフト・プログラムの適用を防止することにより、BLISP方法は、欠陥ビット線上に配置された低しきい値電圧メモリセルによりそうでなければ消費されるであろう過剰電流消費を防止する。過剰な電流はソフト・プログラム方法を大変に非効率的にする。

(もっと読む)

半導体装置

【課題】 絶縁ゲート型トランジスタを有する半導体素子を備えた半導体装置の信頼性を向上させることのできる技術を提供する。

【解決手段】 半導体基板1と、半導体基板1の主面に形成され、絶縁ゲート型トランジスタを有するメモリセルMCと、メモリセルMC上に形成された絶縁膜14と、メモリセルMCと電気的に接続され、絶縁膜14上に形成された金属配線21と、絶縁膜14および金属配線21を覆うように形成された絶縁膜22とを有する。絶縁膜14は、窒素の含有量が1atom%乃至15atom%の範囲内の酸窒化シリコン膜である。

(もっと読む)

半導体装置

【課題】 過消去状態の不揮発性メモリトランジスタに対する書き戻し処理を効率化する。

【解決手段】 半導体装置は各々に複数個の不揮発性メモリトランジスタが割り当てられたページをワード線1本に対して複数ページ有する。不揮発性メモリトランジスタは電荷蓄積領域からエレクトロンを放出させる消去処理によって閾値電圧が低くされ、電荷蓄積領域にエレクトロンを注入するプログラム処理によって閾値電圧が高くされる。制御回路(16)は初期化コマンドに応答して、ワード線単位の消去処理によって閾値電圧分布の上裾をその目標レベルよりも低くした後、その閾値電圧分布の下裾をその目標レベルよりも高くするためのページ単位のプログラム処理を行なう前に、ワード線単位のプログラム処理を行なう。ワード線単位のプログラム処理によって不揮発性メモリトランジスタの閾値電圧分布の下裾は全体として嵩上げされる。

(もっと読む)

不揮発性半導体装置およびその製造方法

【課題】サイドウォール構造を利用する自己整合スプリットゲート型メモリセルと微細MOSトランジスタの混載における最適ゲート高さの差に起因する注入イオン突き抜けの課題を解決する。

【解決手段】 自己整合スプリットゲート型メモリセルのサイドウォールゲート電極高さがロジック部のゲート電極高さを上回るように、サイドウォールを形成するメモリ部選択ゲート電極をロジック部ゲート電極より高く形成する。又、ロジック部はゲート電極形成前迄にゲート電極高さ低減処理を行う。

(もっと読む)

半導体記憶装置およびその製造方法

【課題】メモリセルの微細化に伴うオフリークを低減させることのできる半導体記憶装置およびその製造方法の提供。

【解決手段】トレンチ部1aを有する基板1と、トレンチ部1aに隣接する基板1上に絶縁膜2を介して配設されたセレクトゲート3と、セレクトゲート3下の基板1表面に設けられた第1のウェル1bと、トレンチ部1aの底部ないし側壁部表面に絶縁膜8aを介して配設されたフローティングゲート6と、フローティングゲート6下のトレンチ部1a底部表面に設けられた第2のウェル1cと、トレンチ部1a底部表面に設けられた第1の拡散領域7aと、フローティングゲート6の上に絶縁膜8を介して配設されたコントロールゲート11と、で一つの単位セルを構成し、セレクトゲート3に対してトレンチ部1aの側壁面ないし底面近傍をチャネルとし、第1のウェル1bの不純物濃度は、第2のウェル1cの不純物濃度以下である。

(もっと読む)

不揮発性半導体記憶装置およびその製造方法

【課題】 不揮発性半導体記憶装置の信頼性を向上することのできる技術を提供する。

【解決手段】 基板1の主面上に形成されたアシストゲートAGと、アシストゲートAG上に絶縁膜11を介して形成されたフローティングゲートFGと、フローティングゲートFGの一方の側壁側で絶縁膜14を介すると共に、アシストゲートAG上に絶縁膜11を介して形成されたコントロールゲートCGとの3つのゲートを有してなる複数のメモリセルを備える。

(もっと読む)

半導体集積回路装置の製造方法

【課題】 チップの主面内のパターンの解像度を向上させる。

【解決手段】 チップを含む半導体ウエハの半導体基板1の主面上にキャップ膜を形成した後、チップ内のメモリ領域Mにキャップパターン15aを形成するための露光、現像およびエッチング処理と、チップ内においてメモリ領域Mから離れた空き領域Eにキャップパターン15b1を形成するための露光、現像およびエッチング処理とをそれぞれ別々に行う。これにより、メモリ領域Mおよび空き領域Eの各々に合った条件で露光および現像等を行うことができるので、チップの主面内のパターンの解像度を向上させることができる。

(もっと読む)

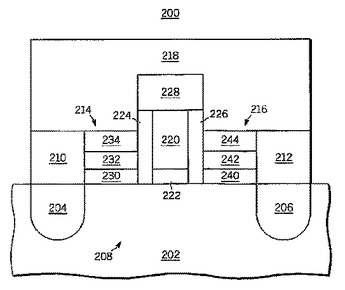

スプリットゲート型マルチビットメモリセル

チャネル領域(208)の中央部分を制御するためのコントロールゲート(220)を備えるマルチビットメモリセル(200)により、より低い電圧および電流にてより早いプログラミングを行うことを含む、向上した動作が提供される。メモリセル(200)は、基板(202)内に拡散したソース(204)およびドレイン(206)を備え、その間にチャネル領域(208)が形成される。第1の電荷保持層(214)、第2の電荷保持層(216)およびコントロールゲート(220)は、チャネル領域(208)上の基板(202)上に形成され、ゲート(218)は、ソース(204)、ドレイン(206)、第1の電荷保持層(214)、第2の電荷保持層(216)およびコントロールゲート(220)の上に形成される。絶縁材料(210,212,224,226,228)は、ソース(204)およびドレイン(206)をゲート(218)から、ならびにコントロールゲート(220)を第1の電荷保持層(214)、第2の電荷保持層(216)およびゲート(218)から分離する。  (もっと読む)

(もっと読む)

不揮発性半導体記憶装置

【課題】 ホットエレクトロン書き込み、及び、バンド間トンネリングによるホットホール消去が可能で低電圧動作及び大容量化に適した不揮発性半導体記憶装置を提供する。

【解決手段】 メモリ機能体18と制御ゲート19からなる第1メモリトランジスタ部15と第2メモリトランジスタ部16、及び、ゲート絶縁膜20と補助ゲート21からなる補助トランジスタ部17を2つの拡散領域13間に有するスプリットゲート構造のメモリセルユニット10を、直列に複数接続したNAND型構成のメモリセルユニット群30を備えてなり、メモリセルユニット群30が、隣接するメモリセルユニット10間で一方の拡散領域13を共有し、共有した拡散領域13にコンタクトを具備しない。また、メモリセルユニット10単位で、第1及び第2メモリトランジスタ部15,16の制御ゲート19に同一電圧が印加可能である。

(もっと読む)

81 - 100 / 122

[ Back to top ]