Fターム[5F083ER06]の内容

半導体メモリ (164,393) | EPROM、EEPROMの書込、消去方法 (6,790) | キャリア制御 (6,786) | 電子注入 (2,236) | ソース側から注入 (122)

Fターム[5F083ER06]に分類される特許

101 - 120 / 122

記憶装置、半導体装置、およびそれらの駆動方法

【課題】低消費電力で動作し、記憶情報の信頼性が高く、小型で軽量、安価な記憶装置とその駆動方法を提供することを課題とする。さらに低消費電力で動作し、記憶情報の信頼性が高く、無線通信距離の長い、小型で軽量、安価な半導体装置とその駆動方法を提供することを課題とする。

【解決手段】記憶装置は、少なくとも記憶素子がマトリックス状に配置されたメモリセルアレイと、書き込み回路とを有し、記憶素子は第一の導電層と、第二の導電層と第一の導電層と第二の導電層とに挟まれて設けられた有機化合物層とを有し、書き込み回路は、複数回印加する電圧を発生させる電圧発生回路と、電圧の出力時間を制御するタイミング制御回路とを有することを特徴とする。

(もっと読む)

埋め込まれたフローティングゲート構造を持つフラッシュメモリセル及びその製造方法

【課題】埋込型フローティングゲート構造のフラッシュメモリセル、及び、そのフラッシュメモリセルの製造方法を提供すること。

【解決手段】本発明は、埋め込み型フローティングゲート構造を持つフラッシュメモリセル及びその製造方法に関し、本発明のフラッシュメモリセルは、半導体基板の上部に形成され、第1の導電膜から形成されたコントロールゲートと、半導体基板の表面とコントロールゲートとの間に形成された誘電体膜と、誘電体膜下の半導体基板の内部に埋め込まれ、第2の導電膜から形成されるフローティングゲートと、半導体基板の内部にフローティングゲートを取り囲みながら形成され、フローティングゲートのボトムコーナー(bottom corner)部分でより厚いトンネル酸化膜と、そして、半導体基板内のフローティングゲートとトンネル酸化膜とを挟んで離隔されているソース及びドレインと、を含む。ソースとドレインとのジャンクションの深さは、互いに異なるので、ソースのジャンクションの深さが、フローティングゲートの深さよりも浅く、ドレインのジャンクションの深さは、フローティングゲートの深さと同じであることができる。あるいは、フラッシュメモリセルのソースとドレインとのジャンクションの深さは、フローティングゲートの深さと同じであり、ソースとドレインとのジャンクションの深さが、フローティングゲートの深さよりも浅かったり、ソースとドレインとのジャンクションの深さが、フローティングゲートの深さよりも深いことができる。

(もっと読む)

不揮発性半導体記憶装置およびその製造方法

【課題】 不揮発性半導体記憶装置の高集積化、高性能化を推進する。

【解決手段】 メモリセルは、浮遊ゲート221b、ワード線WLを構成する制御ゲート222aおよび補助ゲート223aを有するMOSトランジスタで構成される。補助ゲート223aのゲート酸化膜213の厚さは、浮遊ゲート221bのゲート酸化膜211の厚さよりも薄く、ワード線WLの延在方向における補助ゲート223aの寸法(ゲート幅)は、ワード線WLの延在方向における浮遊ゲート221bのゲート長よりも小さい。また、補助ゲート223aの下部のチャネル不純物濃度は、浮遊ゲート221bの下部のチャネル不純物濃度よりも低い。

(もっと読む)

半導体装置の製造方法

【課題】フラッシュメモリを有する半導体装置のメモリセルの動作速度を安定させることのできる技術を提供する。

【解決手段】ゲート電極5aの形成工程において、(1)導体膜5および酸化シリコン膜6の合計の厚さを測定する、(2)隣接するゲート電極5aおよび酸化シリコン膜6からなるパターンのスペースの目標とするアスペクト比と前記(1)の結果とを基にしてゲート電極5aの線幅および隣接するゲート電極5aのスペース幅を修正する、(3)前記(2)の結果をリソグラフィ工程へフィードフォワードしてレジストパターン7の寸法を調整することにより、目標とするアスペクト比を満たすスペースを形成する。

(もっと読む)

半導体装置およびその製造方法

【課題】 フローティングゲート絶縁膜の膜厚のばらつきが抑制されるとともに、リーク電流の低減が図られる半導体装置と、その製造方法を提供する。

【解決手段】 半導体基板1の主表面上にアシストゲート絶縁膜2aを介在させ互いに間隔を隔てて複数のアシストゲート電極33が形成されている。隣り合うシストゲート電極33によって挟まれた半導体基板1の領域の表面上を充填するようにシリコンエピタキシャル成長部13が形成されている。シリコンエピタキシャル成長部13の表面上にフローティングゲート絶縁膜8が形成されている。フローティングゲート絶縁膜8上にフローティングゲート電極99が形成されている。フローティングゲート電極99上にONO膜10を介在させて、ポリシリコン膜11および金属シリサイド膜12からなるコントロールゲート電極34が形成されている。

(もっと読む)

半導体装置およびその製造方法

【課題】フラッシュメモリを有する半導体装置の信頼性を向上させることのできる技術を提供する。

【解決手段】半導体基板1の主面にメモリセルのゲート絶縁膜およびゲート電極5aを形成した後、窒化雰囲気中または窒素を含んだ酸化雰囲気中で半導体基板1に熱処理を施して、露出した半導体基板1の主面に窒素を含む絶縁膜9を形成する。これに続いて、絶縁膜9をエッチングストッパとして、半導体基板1の主面上に堆積した酸化シリコンを主成分とする絶縁膜を異方性のドライエッチングによりエッチバックすることにより、ゲート電極5aの側壁にサイドウォール10を形成し、半導体基板1へのダメージ層の形成を防ぐ。

(もっと読む)

不揮発性電荷蓄積メモリセルをプログラムするための基板電子注入技法

フラッシュメモリ用のプログラミング技法によって、基板からメモリセルの電荷蓄積素子内に電子が注入されることが可能になる。共通の線に印加される電圧によってプログラムされる、共通のワード線または他の共通のコントロールゲート線に沿ったメモリセルのソースおよびドレイン領域が、電気的に浮遊するようにされ、その一方で、プログラムされないメモリセルのソースおよびドレイン領域は、そこに印加される電圧を有する。このプログラミング技法は、NORまたはNAND構造のいずれかを有するメモリセルの大きなアレイに適用される。  (もっと読む)

(もっと読む)

半導体装置およびその製造方法

【課題】 信頼性の高いゲート絶縁膜を有する半導体装置およびその製造方法を提供する。

【解決手段】 半導体装置は、主表面を有する半導体基板8と、半導体基板8の主表面上にゲート絶縁膜12を介して形成され、半導体基板8に反転層を形成するアシストゲート電極3と、半導体基板8の主表面上においてアシストゲート電極3と隣り合う位置に断続的に形成され、半導体基板8およびアシストゲート電極3と電気的に絶縁された孤立パターンであるフローティングゲート電極20と、アシストゲート電極3上にシリコン酸化膜13Aを介して形成され、ゲルマニウムが注入されたシリコン窒化膜13Bと、シリコン窒化膜13B上からフローティングゲート電極20上に形成される絶縁膜15と、フローティングゲート電極20が位置する絶縁膜15上に設けられたコントロールゲート電極2とを備える。

(もっと読む)

半導体装置およびその製造方法、フォトマスク

【課題】 パターンの埋め込み不良の発生が抑制された半導体装置およびその製造方法ならびにフォトマスクを提供する。

【解決手段】 半導体装置の露光工程において用いられるフォトマスク200は、その主表面上に形成された光を遮る残しパターン22(遮光パターン)と、主表面上に形成された光を透過させる抜きパターン23(透光パターン)とを備え、抜きパターン23は、その延在方向の終端部230におけるパターン幅が、中央部側に位置する部分におけるパターン幅よりも広くなるように形成されている。

(もっと読む)

不揮発性半導体記憶装置および不揮発性半導体記憶装置の書込方法、読出方法、消去方法

【課題】pチャネルMONOSメモリセルにおいて、データ書込時のデータ転送レートの高速化を実現する。

【解決手段】ビットラインをGND〜VCCで動作させるために、プログラム時にセルウェルに4Vのバックゲート電圧を印加する。プログラムモードとベリファイモードとの切り換えを高速化するために、ベリファイも4Vのバックゲート電圧が印加されたままの状態で行う。このため、ベリファイ時にはワードライン(ゲート)に−5Vの読出モード時よりも大きい(絶対値)電圧を印加する。

(もっと読む)

不揮発性半導体記憶装置およびその製造方法

【課題】 フローティングゲートとコントロールゲート間の層間絶縁膜をエッチングする際に下地の絶縁膜がエッチングされることに起因するデバイス特性劣化を防止することができる不揮発性半導体記憶装置を提供する。

【解決手段】 半導体基板1と、ゲート絶縁膜2と、半導体基板1の主表面の法線と成す角度θが0度より大きく45度以下となるように傾斜する側面を含み、上方に向かうに従って幅寸法が漸次狭くなるように形成された複数のフローティングゲート8a〜8cと、フローティングゲート8a〜8c間に形成された絶縁膜30と、層間絶縁膜9と、コントロールゲートとを備え、絶縁膜30上でフローティングゲート8a〜8cが分断され、層間絶縁膜9の厚みをTとした場合に絶縁膜30の厚みが、T/sinθ以上である。

(もっと読む)

マルチレベルの仮想接地メモリのための読出方法

この発明は、両面ONOフラッシュメモリセル(500)におけるビットのレベルを決定するための技術(800)に関する。この場合、両面ONOフラッシュメモリセルのビットの各々は複数のレベル(540、542、544)にプログラミング可能である。この発明の1つ以上の局面は、1つのビット上の電荷のレベルが相補ビット妨害として公知である他のビットに及ぼす恐れのある影響を考慮に入れている。相互コンダクタンスとして公知の測定基準が、より高い解像度および精度をもたらすようビットレベルを決定する際に用いられる。この態様では、この発明の1つ以上の局面に従ったビットレベルの決定により、偽のまたは誤った読出が軽減される。  (もっと読む)

(もっと読む)

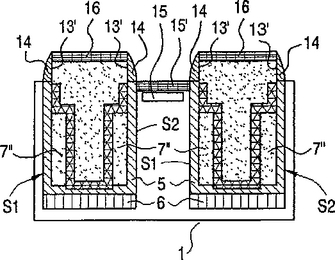

縦型スプリット・ゲート不揮発性メモリ・セルおよび製造方法

半導体基板上に、少なくとも1つのビットを記憶する縦型スプリット・ゲート不揮発性メモリ・セルを備え、基板上に、トレンチと、第1の活性領域と、第2の活性領域と、トレンチの側壁に沿って延びるチャネル領域とを含み、このトレンチは、第1の方向に延びる長さと、それに垂直な第2の方向に延びる幅を有し、トンネル酸化物によって側壁が覆われており、少なくとも1つの浮遊ゲートおよび制御ゲートのゲート・スタックを含み、制御ゲートがトレンチの底部まで延び、第1の浮遊ゲートが、制御ゲートと共に第1のスタックを形成するようにトレンチの左壁に位置するとともに、第2の浮遊ゲートが、制御ゲートと共に第2のスタックを形成するようにトレンチの右壁に位置する半導体デバイス。  (もっと読む)

(もっと読む)

フィン電界効果トランジスタメモリセル、フィン電界効果トランジスタメモリセルアレイおよびフィン電界効果トランジスタメモリセルの製造方法

本発明は、フィン電界効果トランジスタメモリセル(200)、フィン電界効果トランジスタメモリセルアレイおよびフィン電界効果トランジスタメモリセルの製造方法に関するものである。フィン電界効果トランジスタメモリセル(200)は、第1ソース/ドレイン領域(201)および第2ソース/ドレイン領域(202)と、ゲート領域とを有している。メモリセル(200)は、さらに、上記第1ソース/ドレイン領域(201)と第2ソース/ドレイン領域(202)との間にチャネル領域を有する半導体フィン(204)を有し、少なくとも一部が上記ゲート領域上に形成されてなる電荷蓄積層(207・208)を有している。上記電荷蓄積層の少なくとも一部の領域上には、ワード線領域(205・206)が形成されている。フィン電界効果トランジスタセルへの所定の電位の印加により、電荷キャリアを選択的に上記電荷蓄積層へ注入または該電荷蓄積層から放出することができる。  (もっと読む)

(もっと読む)

半導体装置の製造方法

【課題】 複数のコントロールゲート電極間のショートが抑制された半導体装置を提供する。

【解決手段】 半導体装置の製造方法は、アシストゲート電極3および窒化シリコン膜4を形成する工程と、アシストゲート電極3および窒化シリコン膜4の側壁上にアシストゲート電極3および窒化シリコン膜4よりも上方に突出するサイドウォール絶縁膜7を形成する工程と、サイドウォール絶縁膜7上にフローティングゲート電極8となるポリシリコン層を形成する工程と、半導体基板1の主表面に向かって厚みが徐々に増加するように窒化シリコン膜4より上方にサイドウォール絶縁膜7を残存させながらサイドウォール絶縁膜7をエッチングする工程と、窒化シリコン膜4よりも上方に位置する部分に残存したサイドウォール絶縁膜7を除去する工程と、フローティングゲート電極8上にONO膜9およびコントロールゲート電極10を形成する工程とを備える。

(もっと読む)

半導体記憶装置

【課題】

フラッシュメモリでは、微細化するにあたりトランジスタのチャネル長が短くなるため、リーク電流を抑制することが求められている。補助電極を有したAND型メモリアレイはMOSトランジスタを用いたフィールドアイソレーションによって、メモリセル面積を低減しているが、さらに微細化が進むとチャネル方向のリーク電流が大きくなり、書込み特性の劣化や消費電流の増大、読出し不良などが問題となる。

【解決手段】

上記目的を達成するために、本発明は書込みおよび読出し動作において、互いに平行に配線された補助電極のうち少なくとも1本の補助電極を負の電位に設定し、前記補助電極近傍の半導体基板表面を非導通にすることによって、電気的に素子分離を行うことを特徴とする。

(もっと読む)

不揮発性メモリ

【課題】 記憶情報に対する読出し性能を向上させることができる不揮発性メモリを提供することにある。

【解決手段】 メモリトランジスタ21と制御トランジスタ22が繰り返し直列された回路を複数並列に有し、前記制御トランジスタはオンされることにより前記直列方向とは交差する方向に反転層を形成し、読み出し動作において前記制御トランジスタ22をオンさせてメモリトランジスタに流れる電流を制御トランジスタの反転層に引き込み可能とする。前記制御トランジスタ22のゲート電極に供給する信号電圧に正の温度特性を与える特性調整回路を有する。前記反転層は半導体基板の表面に形成され、負の温度特性を有する。反転層の負の温度特性を相殺するのに、反転層を形成する制御トランジスタのゲート電極には正の温度特性を有する電圧を与える。

(もっと読む)

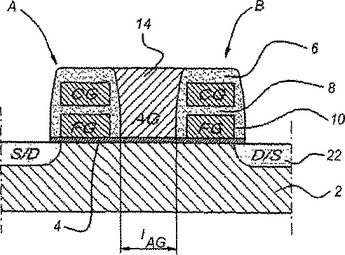

自己整合型の2ビット「ダブル・ポリCMP」フラッシュ・メモリ・セル

第1の浮遊ゲート・スタック(A)と、第2の浮遊ゲート・スタック(B)と、中間アクセス・ゲート(AG)とを含むメモリ・セルの製作。浮遊ゲート・スタック(A、B)は、第1のゲート酸化物(4)と、浮遊ゲート(FG)と、制御ゲート(CG;CGl、CGu)と、ポリ間誘電体層(8)と、キャッピング層(6)と、側壁スペーサ(10)とを含む。メモリ・セルはさらに、ソースおよびドレイン接触部(22)を含む。このメモリ・セルの製作は、浮遊ゲート・スタックを等しい高さにするために同じ処理工程で画定すること、ポリSi層(12)を浮遊ゲート・スタックの高さよりも大きな厚みで浮遊ゲートを覆って堆積させること、ポリSi層(12)を平坦化すること、浮遊ゲート・スタック間のポリSi層上にアクセス・ゲート・マスクを使用するマスキング工程およびポリSiエッチング工程によって、平坦化されたポリSi層(14)内に中間アクセス・ゲート(AG)を画定することを含む。  (もっと読む)

(もっと読む)

半導体記憶装置およびその製造方法並びに携帯電子機器

【課題】微細化が容易な半導体記憶装置を提供する。

【解決手段】半導体基板211上には、ゲート絶縁膜214を介して単一のゲート電極217を形成している。ゲート電極217の両側には、第1,第2のメモリ機能体261,262を形成している。半導体基板211のゲート電極217側の表面部にはP型のチャネル領域472を形成し、チャネル領域472の両側にN型の第1,第2の拡散領域212,213を形成している。チャネル領域472は、第1,第2のメモリ機能体261,262下に位置するオフセット領域401と、ゲート電極217下に位置するゲート電極下領域402とで構成されている。オフセット領域401にP型の導電型を与える不純物の濃度は、ゲート電極下領域402にP型の導電型を与える不純物の濃度に比べて実効的に薄くなっている。

(もっと読む)

不揮発性半導体記憶装置

【課題】 複数のスタックゲート型メモリセルを含むフラッシュメモリにおいて、消去前書込動作を不要とすることにより一括消去動作に要する時間を短縮し、データの書換動作に要する時間も短縮することである。

【解決手段】 消去時に、複数のメモリセルのソース1003からフローティングゲート1005に同時に電子を注入する。それにより、複数のメモリセルのしきい値電圧が上昇する。プログラム時に、選択されたメモリセルのフローティングゲート1005からドレイン1002に電子を放出する。それにより、選択されたメモリセルのしきい値電圧が下降する。

(もっと読む)

101 - 120 / 122

[ Back to top ]