Fターム[5F083FR06]の内容

半導体メモリ (164,393) | 強誘電体メモリ (1,733) | MFS型(非破壊読出型) (230) | MFIS型 (67)

Fターム[5F083FR06]に分類される特許

1 - 20 / 67

半導体装置

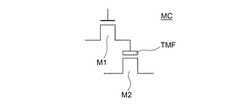

【課題】頻繁なリフレッシュ動作が不要で、正常な読み出しを行うことのできる2トランジスタ型のDRAMを備えた半導体装置を提供する。

【解決手段】本実施形態の半導体装置は、ゲートが第1配線に接続され、第1ソース/ドレインの一方が第2配線に接続された第1トランジスタと、ゲート絶縁膜、ゲート電極、および前記ゲート絶縁膜と前記ゲート電極との間に設けられしきい値を変調するしきい値変調膜を有するゲート構造と、第2ソース/ドレインとを備え、前記ゲート電極が前記第1トランジスタの前記第1ソース/ドレインの他方に接続され、前記第2ソース/ドレインの一方が第3配線に接続され、前記第2ソース/ドレインの他方が第4配線に接続された第2トランジスタと、を備えている。

(もっと読む)

マンガン酸化物、マンガン酸化物を備える強誘電体メモリ素子、および強誘電体メモリ装置

【課題】主成分として有害物質鉛元素を含まずに、強誘電性を示しかつ外部磁場によって分極の大きさを制御可能な新規なマンガン酸化物、およびそのメモリへの利用を提供する。

【解決手段】マンガン酸化物は、ペロブスカイト構造を有する、式(1)Sr1−xBaxMnO3(1≧x>0.4)・・・(1)で表されるマンガン酸化物である。単位格子1の対称中心には磁性イオンであるMnイオン3が存在する。単位格子1の対称中心をMnサイトとする。単位格子1が有する8個の頂点には、SrイオンおよびBaイオンのうちいずれか一方が存在している。単位格子1が有する頂点をSrサイト2とする。単位格子1が有する6面の面心には、Oイオン4が存在する。

(もっと読む)

半導体構造

【課題】多くの半導体装置に必要な低温処理と両立しない高温操作を必要とするような欠点がない、半導体構造を提供することを目的とする。

【解決手段】下部誘電層(151)へ接合された基板(103)、および、下部電極(121)を通じて前記下部誘電層(151)と接合される垂直方向半導体装置(111)を含む半導体構造であって、前記垂直方向半導体装置(111)は、n+−p−n+層(124)を有する隔離構造(135)を含む。

(もっと読む)

半導体集積回路

【課題】 不揮発記憶保持用途の電界効果トランジスタと、論理演算用途の電界効果トランジスタの製造工程を別々に設けることなく前記2用途の電界効果トランジスタを同一半導体基板上に同一構造に作製できるようにする。

【解決手段】 ゲート絶縁構造体12に記憶保持材料を含むnおよびpチャネル型電界効果トランジスタで半導体集積回路のメモリ回路とロジック回路の両方を構成し、ゲート絶縁構造体に記憶保持材料を含むnおよびpチャネル型電界効果トランジスタのゲート-基板領域間に印加する電圧の大きさと印加タイミングを制御することによって、論理演算状態と記憶書込み状態と不揮発記憶保持状態を電気的に切り替える。

(もっと読む)

不揮発性半導体メモリ

【課題】新たなコンセプトに基づく不揮発性半導体メモリを提供する。

【解決手段】本開示の不揮発性半導体メモリは、半導体基板11上の半導体層12と、半導体層12を貫通する複数のコントロールゲートCG11〜CG17と、第1方向の2つの端部における半導体層12内にそれぞれ配置される2つの第1導電型拡散層14と、半導体層12上で第1方向に延びる複数のセレクトゲート線SG1〜SG5と、複数のセレクトゲート線SG1〜SG5上で第2方向に延びる複数のワード線WL1〜WL7とを備える。複数のセレクトゲート線SG1〜SG5の各々は、第1方向に並ぶ複数のコントロールゲートCG11〜CG17と複数のワード線WL1〜WL7との間に接続される複数のセレクトトランジスタに共有されるセレクトゲートとして機能する。半導体層12及び複数のコントロールゲートCG11〜CG17は、メモリセルアレイを構成する。

(もっと読む)

半導体記憶装置

【課題】従来の強誘電体メモリと比べてメモリセルのサイズを縮小し、かつ、メモリ容量を増大させることができる半導体記憶装置を提供する。

【解決手段】メモリは、半導体基板の表面に形成された第1の拡散層と、第1の拡散層上に設けられたボディ領域と、ボディ領域上に設けられた第2の拡散層と、ボディ領域の第1の側面に設けられた強誘電体膜を含む第1のゲート絶縁膜と、ボディ領域の第2の側面に設けられた強誘電体膜を含む第2のゲート絶縁膜と、ボディ領域の第1の側面に第1のゲート絶縁膜を介して設けられている第1のゲート電極と、ボディ領域の第2の側面に第2のゲート絶縁膜を介して設けられている第2のゲート電極とを備え、第1および第2の拡散層、ボディ領域、第1および第2のゲート絶縁膜、並びに、第1および第2のゲート電極はメモリセルを構成し、各メモリセルは、第1および第2のゲート絶縁膜の分極状態によって複数の論理データを記憶する。

(もっと読む)

半導体記憶装置

【課題】従来と比べて製造プロセスを複雑にすることなく、メモリ容量を増大させることがきる半導体記憶装置を提供する。

【解決手段】半導体記憶装置は、半導体層と、半導体層内に設けられたソース層およびドレイン層と、ソース層とドレイン層との間の半導体層に設けられ、論理データを記憶するために電荷を蓄積し、あるいは、電荷を放出する電気的に浮遊状態のボディ領域と、ボディ領域上に設けられ、分極特性を有する強誘電体膜を含むゲート絶縁膜と、ゲート絶縁膜を介してボディ領域上に設けられたゲート電極とを含むメモリセルを複数備え、各メモリセルは、ボディ領域に蓄積された電荷量および強誘電体膜の分極状態によって複数の論理データを記憶する。

(もっと読む)

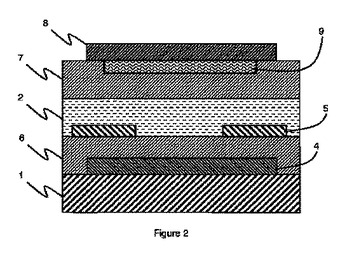

有機デュアルゲートメモリおよびその製造方法

有機メモリデバイスは、第1のゲート電極(4)と、第1のゲート誘電体(6)と、有機半導体材料(2)と、第2のゲート誘電体(7)と、第2のゲート電極(8)とを備えるデュアルゲートトランジスタである。ソース・ドレイン電極(5)が、有機半導体材料(2)中に配置されるとともに、電極間表面を規定する。捕捉領域(9)が、有機半導体材料(2)とゲート電極(4,8)のうちの一方との間に配置されるとともに、ゲート電極(4,8)のうちの一方または有機半導体材料(2)と電気的に接触する。捕捉領域(9)は少なくとも電極間表面と対向する。  (もっと読む)

(もっと読む)

不揮発性メモリセル及びその製造方法

【課題】同一の基板上に形成されたメモリトランジスタ及び駆動トランジスタを備える透明不揮発性メモリセル及びその製造方法を提供する。

【解決手段】本発明による不揮発性メモリセルは、基板上に形成された半導体膜、バッファー膜、有機強誘電体膜及びゲート電極を含むメモリトランジスタと;前記基板上に形成された前記半導体膜、前記バッファー膜、ゲート絶縁膜及び前記ゲート電極を含む駆動トランジスタと;を備える。本発明によれば、同一の基板上に形成されたメモリトランジスタ及び駆動トランジスタを備え、可視光領域で透明な不揮発性メモリセルを提供することができる。

(もっと読む)

絶縁ゲート型半導体装置の製造方法

【課題】非ヒステリシストランジスタとヒステリシストランジスタとを混載する場合において、欠陥や不純物混入リスクの少ない良好な基板界面を保ったまま、同一材料の絶縁膜を用いて、ヒステリシストランジスタと非ヒステリシストランジスタとを同一基板上に混載することができる絶縁ゲート型半導体装置の製造方法を提供する。

【解決手段】第1及び第2のトランジスタ形成領域上に第1のトランジスタにヒステリシス特性を与える絶縁膜1を形成し、これを第1のトランジスタのゲート絶縁1膜とする工程、及び、第2のトランジスタ形成領域上の絶縁膜1を部分的にエッチング除去することにより、第2のトランジスタにヒステリシス特性を与えない絶縁膜とし、これを第2のトランジスタのゲート絶縁膜とする工程を含む。

(もっと読む)

半導体記憶装置の製造方法

【課題】製造歩留まりを低減することなく、大容量の不揮発性メモリを備えた半導体記憶装置を製造することのできる技術を提供する。

【解決手段】半導体基板1の主面にゲート絶縁膜4を形成した後、ライン幅が最小加工寸法よりも小さく、ピッチが最小加工寸法の2倍のライン状のダミーゲートを形成する。続いて、ダミーゲートの側壁にサイドウォールを形成した後、ダミーゲートを除去する。その後、半導体基板1上に強誘電体材料および上部電極材料を形成し、これら強誘電体材料および上部電極材料をCMP法を用いて加工することにより、メモリセル毎に分離された強誘電体5を形成する。これにより、ビット線の延在方向に沿って最小加工寸法と同じピッチでメモリセルを配置できるので、メモリセル面積が4F2未満、例えば2F2のメモリセルを形成することができる。

(もっと読む)

強誘電体及び記憶装置

【課題】数nm程度のセルサイズを実現可能な強誘電体及び記憶装置を提供すること。

【解決手段】強誘電体2は、分子内で正に帯電された水素原子群(第一原子群)15と負に帯電された酸素原子群(第二原子群)16とが結合された水分子(極性分子)17同士が、さらに水素原子群15又は酸素原子群16が一端2a又は他端2bに配されるよう一方向に交互に配列された5本の一次元鎖13A〜13Eを有するアイスナノチューブ11Aと、アイスナノチューブ11Aを内包するカーボンナノチューブ(ナノチューブ)11Bと、を備えている。

(もっと読む)

半導体不揮発記憶装置

【課題】本発明は、複数電圧源を用意することなくFeFET単体へ多値記憶を行うことができる半導体不揮発記憶装置を提供することを課題とする。

【解決手段】強誘電体に、同一高さで、異なる幅のパルス電圧を印加して、異なる総分極量を与え、その総分極量の違いに応じた異なる記憶状態を作る多値強誘体メモリセルを有する半導体不揮発記憶装置である。

(もっと読む)

強誘電体ゲート有機電界効果トランジスタ、それを用いたメモリ素子及び強誘電体ゲート有機電界効果トランジスタの製造方法

【課題】強誘電体膜及びゲート電極間のリーク電流値を低減させると共に耐絶縁性を向上させる。

【解決手段】Si基板1と、Si基板1上に少なくともHfSiON膜2、強誘電体膜3HfSiON膜4及びC60膜6が、この順で積層されたゲート構造を有しており、強誘電体膜3の、HfSiON膜4と接する側の表面におけるRa値とRms値との和の第1絶対値が、HfSiON膜4の膜厚以下であり、かつ、HfSiON膜4の、C60膜6と接している側の表面におけるRa値とRms値との和の第2絶対値が3.0nm以下である。

(もっと読む)

強誘電体膜、強誘電体膜を有する半導体装置、及びそれらの製造方法

【課題】 従来よりも小型化が可能で安定した動作が可能であり、下地との密着性に優れた強誘電体膜、強誘電体膜を用いた半導体装置、その製造方法および強誘電体膜を用いた強誘電体デバイスを提供する。

【解決手段】 半導体装置71は基板55、絶縁体56、酸化タンタル膜66、強誘電体膜(STN膜)57、上部電極膜62を有している。

酸化タンタル膜66は強誘電体膜(STN膜)57を結晶化する際に下地となる。

酸化タンタル膜66は酸素を含み、格子情報が強誘電体膜(STN膜)57の結晶と近似している。

そのため、酸化タンタル膜66上にSTNを結晶化すると、酸素欠損がなく、結晶粒径が100nm以下の強誘電体膜(STN膜)57が得られる。

(もっと読む)

半導体記憶装置

【課題】簡単な動作で、MFSFETに記憶された多値データを読み出すことのできる半導体記憶装置を提供することにある。

【解決手段】強誘電体膜13からなるゲート絶縁膜と、半導体膜14からなるチャネルとを有する第1の電界効果トランジスタ21で構成されたメモリセルと、メモリセルに直列に接続された読み出し用の負荷素子24とを備え、メモリセルは、強誘電体膜13の分極状態に応じた、少なくとも3値以上のチャネル抵抗値を多値データとして記憶している。メモリセルに記憶された多値データは、メモリセルと負荷素子24との間の中間電位を検出することによって読み出され、読み出し動作は、メモリセルに記憶された多値データを、チャネル抵抗値の高い状態から順に判別することによって実行される。

(もっと読む)

強誘電体膜、強誘電体膜を有する半導体装置、及びそれらの製造方法

【課題】従来よりも小型化が可能で安定した動作が可能であり、下地との密着性に優れた強誘電体膜、強誘電体膜を用いた半導体装置、その製造方法および強誘電体膜を用いた強誘電体デバイスを提供する。

【解決手段】半導体装置71は基板55、絶縁体56、酸化イットリウム膜66、強誘電体膜(STN膜)57、上部電極62を有している。酸化イットリウム膜66は強誘電体膜(STN膜)57を結晶化する際に下地となる。酸化イットリウム膜66は酸素を含み、格子情報が強誘電体膜(STN膜)57の結晶と近似している。そのため、酸化イットリウム膜66上にSTNを結晶化すると、酸素欠損がなく、かつ抗電界が200kV/cm以上の強誘電体膜(STN膜)57が得られる。

(もっと読む)

強誘電体メモリセルおよび強誘電体メモリ

【課題】強誘電体メモリセルに保持されたデータの読み出しマージンの低下を防止する。

【解決手段】強誘電体トランジスタFTRは、ゲート絶縁膜に強誘電体膜FFを有し、読み出しワード線RWLにソース/ドレインの一方が接続され、読み出しビット線RBLにソース/ドレインの他方が接続され、プレート線PLにウエルNWが接続されている。選択トランジスタSTRは、書き込みワード線WWLにゲートが接続され、書き込みビット線WBLにソース/ドレインの一方が接続され、強誘電体トランジスタのゲートにソース/ドレインの他方が接続されている。強誘電体トランジスタのソースおよびドレインを用いて読み出し動作を行うことで、読み出し動作時に、強誘電体トランジスタのゲート絶縁膜を構成する強誘電体膜に電圧が印加されることを避けることができ、強誘電体膜の分極状態が変化することを防止できる。

(もっと読む)

強誘電体メモリ

【課題】 強誘電体メモリセルに保持されたデータの読み出しマージンの低下を防止する。

【解決手段】 強誘電体トランジスタは、ゲート絶縁膜に強誘電体膜を有し、ソース/ドレインの一方がプレート線に接続され、ソース/ドレインの他方およびウエルが接続ノードに接続され、ゲートがドライブ線に接続されている。選択トランジスタは、ゲートがワード線に接続され、ソース/ドレインの一方がビット線に接続され、ソース/ドレインの他方が接続ノードに接続されている。プレート線およびドライブ線は、第1方向に並ぶメモリセルの列に共通に接続されている。ビット線は、第1方向に交わる第2方向に並ぶメモリセルの列に共通に接続されている。ワード線は、第1および第2方向に対して斜めに配線されている。第1方向に並ぶメモリセルおよび第2方向に並ぶメモリセルは、互いに異なるワード線に接続されている。

(もっと読む)

強誘電体膜、金属酸化物、半導体装置、及びそれらの製造方法

【課題】 強誘電体膜厚が薄く、長期のデータ保持特性を有する強誘電体メモリー装置に用いられる半導体装置、その製造方法、その製造装置、強誘電体膜及び強誘電体膜の製造方法を提供すること。

【解決手段】 強誘電体膜57は、膜材料として、Sr、Ta、及びNbを主成分とする強誘電体材料が用いられ、10日以上のデータ保持時間を有する。強誘電体膜を製造する方法は、強誘電体膜57を形成する膜形成工程と、前記強誘電体膜57を酸素ラジカル58によって酸化する酸素導入工程とを有する。

(もっと読む)

1 - 20 / 67

[ Back to top ]