Fターム[5F083GA16]の内容

Fターム[5F083GA16]に分類される特許

1 - 20 / 100

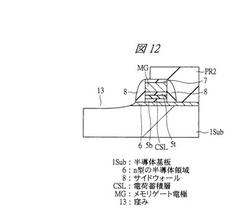

半導体装置

【課題】スプリットゲート型メモリセル構造を採用し、電荷蓄積層として窒化膜を用いる不揮発性メモリを有する半導体装置において電気的特性を向上させる。

【解決手段】半導体基板1Subの主面にn型の半導体領域6を形成した後、その上にスプリットゲート型のメモリセルのメモリゲート電極MGおよび電荷蓄積層CSLを形成する。続いて、そのメモリゲート電極MGの側面にサイドウォール8を形成した後、半導体基板1Subの主面上にフォトレジストパターンPR2を形成する。その後、フォトレジストパターンPR2をエッチングマスクとして、半導体基板1Subの主面の一部をエッチングにより除去して窪み13を形成する。この窪み13の形成領域では上記n型の半導体領域6が除去される。その後、その窪み13の形成領域にメモリセル選択用のnMISのチャネル形成用のp型の半導体領域を形成する。

(もっと読む)

不揮発性半導体記憶装置

【課題】選択メモリセルトランジスタに電荷を蓄積する際の電圧を従来よりも自由に設定し得る不揮発性半導体記憶装置を提案する。

【解決手段】不揮発性半導体記憶装置1では、選択メモリセルトランジスタ115に電荷を蓄積させる際、電圧の高い書き込み禁止電圧をP型MOSトランジスタ9bから印加し、電圧の低い書き込み電圧をN型MOSトランジスタ15aから印加して、選択メモリセルトランジスタ115又は非選択メモリセルトランジスタ116へ電圧を印加する役割分担を、P型MOSトランジスタ9b及びN型MOSトランジスタ15aに分けたことで、P型MOSトランジスタ9b及びN型MOSトランジスタ15aそれぞれのゲート電圧やソース電圧を個別に調整でき、最終的にゲート基板間電圧を例えば4[V]等に設定し得る。

(もっと読む)

相変化メモリ

【課題】三次元構造を有する相変化メモリの熱ディスターブを抑制する。

【解決手段】三次元構造を有する相変化メモリにおいて、選択用MOSトランジスタのゲート絶縁膜として、高い熱伝導率を有する材料を使用し、相変化記録膜からSiチャネル層に伝達する熱を良好にゲート電極に拡散させる。これにより、記録ビットから発生する熱が非選択の隣接ビットに拡散し、隣接ビットのデータを消去する熱ディスターブを抑制する。高い熱伝導率を有するゲート絶縁膜材料としては、BN、Al2O3、AlN、TiO2、Si3N4、ZnOなどを挙げることができる。

(もっと読む)

半導体装置の製造方法

【課題】第1MISFETのゲート電極と第2MISFETのゲート電極とを別工程で形成する半導体装置の製造技術において、第1MISFETと第2MISFETの信頼性向上を図ることができる技術を提供する。

【解決手段】半導体基板20上にゲート絶縁膜26、電荷蓄積膜27、絶縁膜28、ポリシリコン膜29、酸化シリコン膜30、窒化シリコン膜31およびキャップ絶縁膜32からなる積層膜を形成する。そして、フォトリソグラフィ技術およびエッチング技術を使用して、低耐圧MISFET形成領域および高耐圧MISFET形成領域に形成されている積層膜を除去する。その後、半導体基板20上にゲート絶縁膜34、36、ポリシリコン膜37およびキャップ絶縁膜38を形成する。そして、低耐圧MISFET形成領域および高耐圧MISFET形成領域にゲート電極を形成した後、メモリセル形成領域にゲート電極を形成する。

(もっと読む)

半導体装置

【課題】従来は、外部機器側で情報の書き込みが正常に成されたか否かを判断していた。また、半導体装置ないに大掛かりな回路を構成しなければ、正しく書き込みを判断できなかった。

【解決手段】外部機器から入力される書込パルスのうち、そのパルス長で、搭載する不揮発性記憶手段に情報が正しく書き込まれたか否かの判定を行なう判断手段を設けた。判断手段は、書込パルスのパルス長が所定の範囲にあるか否かや、書込パルスの到来と同時に時間を計測する計時手段などを用いることで、パルス長が正しいか否かを判定する。これにより、簡便な構成で、正しい情報の書き込みを判断できる。

(もっと読む)

不揮発性半導体記憶装置の製造方法

【課題】カーボンナノチューブを可変抵抗素子として用い消費電力の抑制とスイッチの誤作動の低減を両立した不揮発性半導体記憶装置の製造方法を提供する。

【解決手段】実施形態の不揮発性半導体記憶装置の製造方法は、半導体基板9上に、下部電極を形成する工程と、前記下部電極の上にカーボンナノチューブを含む可変抵抗層11を形成する工程と、前記可変抵抗層に電子線或いは光子線を照射する照射工程と、前記照射工程の後に、前記可変抵抗層の上に上部電極を形成する工程とを含む。

(もっと読む)

半導体装置及びその製造方法

【課題】モリセル領域内と周辺回路領域内およびそれらとの間に実施的に段差がない状態でメタル積層配線を形成し、段差部でメタル積層配線が断線する問題を回避する。センスアンプを構成するNMOSトランジスタとPMOSトランジスタのアンバランス動作を解消して動作遅延を軽減する。

【解決手段】半導体装置は、半導体基板上にメモリセル領域と周辺回路領域とを有し、メモリセル領域と周辺回路領域に跨って延在し、メモリセル領域ではビット線を構成し、周辺回路領域では周辺回路用配線の一部とゲート電極の一部を構成するメタル積層配線を有する。メモリセル領域に配置されるメタル積層配線の底面の半導体基板上面からの高さが、周辺回路領域に配置されるメタル積層配線の底面の半導体基板上面からの高さと実質的に同じである。

(もっと読む)

半導体装置

【課題】電力が供給されない状況でも記憶内容の保持が可能で、かつ、書き込み回数にも制限が無い、新たな構造の半導体装置を提供する。

【解決手段】トランジスタのオフ電流を十分に小さくすることができる材料、例えば、ワイドギャップ半導体である酸化物半導体材料を用いて半導体装置を構成する。トランジスタのオフ電流を十分に小さくすることができる半導体材料を用いることで、長期間にわたって情報を保持することが可能である。また、書き込みワード線に電気的に接続する容量素子またはノイズ除去回路を設けることで、駆動回路等からメモリセルに入力されうる制御信号とは異なる短パルスやノイズ等の信号を低減または除去することができる。これにより、メモリセルが有するトランジスタが瞬間的にオンすることでメモリセルに書き込まれたデータが消失してしまう誤動作を防ぐことが可能である。

(もっと読む)

不揮発性半導体記憶装置

【課題】安定した動作を実行可能な不揮発性半導体記憶装置を提供する。

【解決手段】不揮発性半導体記憶装置は、複数のセルユニットを有し且つ複数のセルユニットに保持されたデータを消去する消去動作実行の単位とされる複数のメモリブロックを備える。セルユニットは、メモリストリング、第1トランジスタ、第2トランジスタ、及びダイオードを備える。第1トランジスタは、メモリストリングの一端に一端を接続されている、第2トランジスタは、メモリストリングの他端と第2配線との間に設けられている。ダイオードは、第1トランジスタの他端と第1配線との間に設けられている。ダイオードは、基板に対して垂直方向に延びる第1導電型の第2半導体層と、第2半導体層の上面に接して基板に対して垂直方向に延びる第2導電型の第3半導体層とを備える。

(もっと読む)

不揮発性半導体記憶装置

【課題】データリテンションの特性を向上しつつ消去動作や書き込み動作に要する時間を短縮する。

【解決手段】

不揮発性半導体記憶装置は、第1書き込み領域と第2書き込み領域を有し、複数のメモリセルを含むメモリセルアレイを備える。制御回路は、複数のメモリセルに対して印加する電圧を制御する。制御回路は、複数のメモリセルに対し消去動作を実行する場合に、第2書き込み領域のメモリセルに隣接する第1書き込み領域のメモリセルを除いた第1書き込み領域のメモリセルに第1閾値電圧を与える一方、第2書き込み領域のメモリセル及び第2書き込み領域のメモリセルに隣接する第1書き込み領域のメモリセルに第1閾値電圧より電圧値が大きい消去状態を示す正の第2閾値電圧を与えるよう制御する。

(もっと読む)

不揮発性半導体記憶装置及びその製造方法

【課題】不揮発性半導体記憶装置の高信頼性及び高集積化を図る。

【解決手段】実施形態に係わる不揮発性半導体記憶装置は、第1の方向に積み重ねられる第1乃至第iのメモリストリング(iは、2以上の自然数)を有し、第2の方向に延び、第3の方向に隣接する第1及び第2のフィン型積層構造9−1,9−2と、第1のフィン型積層構造9−1の第2の方向の一端に接続され、第3の方向の幅が第1のフィン型積層構造9−1のそれよりも広い第1の部分7aと、第2のフィン型積層構造9−2の第2の方向の一端に接続され、第3の方向の幅が第2のフィン型積層構造9−2のそれよりも広い第2の部分7bとを備える。第1乃至第iのメモリストリングは、それぞれ、複数のメモリセルとアシストゲートトランジスタとを備える。アシストゲートトランジスタのアシストゲート電極AG1,AG2は、電気的に独立である。

(もっと読む)

不揮発性記憶装置とその制御方法

【課題】スイッチング歩留りを向上させることができる不揮発性記憶装置を提供する。

【解決手段】実施形態によれば、不揮発性記憶装置は、下部電極膜BEと、上部電極膜TEと、前記下部電極膜BEと前記上部電極膜TEとの間に挟持される抵抗変化層RWと、を備える。前記抵抗変化層RWは、前記上部電極膜TE側から前記下部電極膜BE側に流れる電気的信号によって、複数の異なる抵抗状態間を可逆的に変化させることが可能なSi,Cを主成分とし、Nを含むアモルファスの膜からなる。また、前記上部電極膜TEは、前記下部電極膜BEよりも窒素濃度が低い材料によって構成される。

(もっと読む)

不揮発性半導体メモリ

【課題】新たなコンセプトに基づく不揮発性半導体メモリを提供する。

【解決手段】本開示の不揮発性半導体メモリは、半導体基板11上の半導体層12と、半導体層12を貫通する複数のコントロールゲートCG11〜CG17と、第1方向の2つの端部における半導体層12内にそれぞれ配置される2つの第1導電型拡散層14と、半導体層12上で第1方向に延びる複数のセレクトゲート線SG1〜SG5と、複数のセレクトゲート線SG1〜SG5上で第2方向に延びる複数のワード線WL1〜WL7とを備える。複数のセレクトゲート線SG1〜SG5の各々は、第1方向に並ぶ複数のコントロールゲートCG11〜CG17と複数のワード線WL1〜WL7との間に接続される複数のセレクトトランジスタに共有されるセレクトゲートとして機能する。半導体層12及び複数のコントロールゲートCG11〜CG17は、メモリセルアレイを構成する。

(もっと読む)

半導体装置及びその製造方法

【課題】デバイス特性及びプロセスのばらつきを低減できる半導体装置及びその製造方法を提供する。

【解決手段】半導体装置は、基板10と、下部ゲート層BGと、積層体と、ダミー電極層DWLと、絶縁膜30と、チャネルボディ20,45とを備えた。下部ゲート層BGは、基板10上に設けられた。積層体は、下部ゲート層BG上にそれぞれ交互に積層された複数の絶縁層と複数の電極層WLとを有する。ダミー電極層DWLは、下部ゲート層BGと積層体との間に設けられ、電極層WLと同じ材料からなり、各々の電極層WLよりも厚い。絶縁膜30は、積層体及びダミー電極層を貫通して形成されたホールMHの側壁に設けられた電荷蓄積膜を含む。チャネルボディ20,45は、ホールMH内における絶縁膜30の内側に設けられた。

(もっと読む)

不揮発性半導体記憶装置

【課題】各メモリセルの書込消去特性を極力一定にできる不揮発性半導体記憶装置を提供する。

【解決手段】複数のメモリセルトランジスタMTは、活性領域Saが素子分離溝2によって互いに分離している。これらのメモリセルトランジスタMTは、それぞれ、活性領域Saの上面上または上方にトンネル絶縁膜3を介して電荷蓄積機能を有する電荷トラップ膜4を備えている。積層絶縁膜Bは、トンネル絶縁膜3および電荷トラップ膜4を少なくとも含んで構成され、トンネル絶縁膜3が素子分離溝2の内面に沿って形成されると共に電荷トラップ膜4がトンネル絶縁膜3の上面に沿って積層されており、素子分離溝2内の全領域に埋込まれている。

(もっと読む)

半導体装置およびその製造方法

【課題】電荷を蓄積可能な電荷蓄積膜を有する不揮発性メモリセルを含む半導体装置において、データ保持特性劣化を改善し、その信頼性を向上させることにある。

【解決手段】半導体基板の主面に不揮発性メモリセルを含む半導体装置であって、不揮発性メモリセルは、半導体基板上に第1絶縁膜と、導電膜と、第2絶縁膜と、電荷を蓄積可能な電荷蓄積膜とを有する。また、電荷蓄積膜上に第3絶縁膜と、第1ゲート電極と、第1絶縁膜から前記第1ゲート電極までの一連の積層膜と接するように第4絶縁膜と、第1絶縁膜と並ぶように前記半導体基板上に第5絶縁膜とを有する。さらに、第5絶縁膜上に形成され、第4絶縁膜の側面に前記第1ゲート電極と隣り合うように第2ゲート電極と、第1ゲート電極と第2ゲート電極を挟むように半導体基板にソース領域およびドレイン領域とを有する。半導体装置は、導電膜と電荷蓄積膜が平面的に重なり合うように形成されている。

(もっと読む)

不揮発性記憶装置

【課題】データの消去または書き込み時の誤動作を防止することができる不揮発性記憶装置を提供する。

【解決手段】抵抗変化層RWを有する不揮発性記憶装置において、抵抗変化層RWは、金属酸化膜に、25at%以下の濃度で、金属酸化膜を構成する金属元素に比して電気陰性度の大きな元素が含まれる膜によって構成される。

(もっと読む)

不揮発性半導体記憶装置

【課題】高効率的に書き込みを行うことができる不揮発性半導体記憶装置を提供する。

【解決手段】直列接続された複数のメモリセルトランジスタMTと、メモリセルトランジスタの一端とソース線との間に接続された選択ゲートトランジスタST2と、メモリセルトランジスタの他端とビット線との間に接続された選択ゲートトランジスタST1と、ソース線に第1の電圧を印加し、ビット線に第1の電圧よりも高く且つ第1の電圧との差がトンネル絶縁膜のバリアハイトに対応する電圧よりも小さい第2の電圧を印加し、書き込み対象のメモリセルトランジスタMTとソース線との間に位置し、且つ書き込み対象のメモリセルトランジスタに隣接する隣接メモリセルトランジスタMTの導通状態を、他のメモリセルトランジスタMTの導通状態よりも弱くすることで書き込み対象のメモリセルトランジスタに書き込みを行う制御回路と、を具備する。

(もっと読む)

不揮発性メモリ消去オペレーションにおけるワード・ライン補正

【課題】NANDストリング内のメモリ・セル毎に消去速度を一様とする消去技術を提供する。

【解決手段】複数のメモリ・セルの消去オペレーションを等化するために、消去オペレーション中に補正電圧を不揮発性メモリ・システムに印加する。補正電圧は、他のメモリ・セル及び/又は選択ゲートからNANDストリングのメモリ・セルに静電容量カップルされた電圧を補正する。補正電圧を1又は複数のメモリ・セルに印加して、メモリ・セルの消去オペレーションを実質的に好適化できる。補正電圧をNANDストリングの端部メモリ・セルに印加することで、その消去オペレーションをNANDストリングの内部メモリ・セルと等しくすることができる。

(もっと読む)

不揮発性半導体記憶装置

【課題】書き込み/消去におけるディスターブを抑制し、かつ面積の増大を抑えた不揮発性半導体記憶装置を提供する。

【解決手段】複数のメモリセルMCを含む第1セルアレイ32が形成された第1導電型の第1のウェル領域と、複数のメモリセルMCを含む第2セルアレイ32が形成された第1導電型の第2のウェル領域と、第1、第2のウェル領域を含む第2導電型の第3のウェル領域とを備える。さらに、第1セルアレイ32が含むメモリセルと第2セルアレイ32が含むメモリセルとに共通に接続されたビット線BLと、ビット線BLに接続されたカラムデコーダ13とを備える。

(もっと読む)

1 - 20 / 100

[ Back to top ]