Fターム[5F083JA03]の内容

半導体メモリ (164,393) | 材料 (39,186) | キャパシタ絶縁膜材料、ゲート絶縁膜材料 (10,102) | 酸化物系 (9,104) | 酸化膜を含む複合膜 (2,564)

Fターム[5F083JA03]の下位に属するFターム

シリコン酸化膜とシリコン窒化膜による複合膜 (1,945)

Fターム[5F083JA03]に分類される特許

601 - 619 / 619

不揮発性半導体記憶装置およびその製造方法

【課題】 積層絶縁膜(非導電性電荷トラップ層)内に離散的に電荷を蓄積する不揮発性半導体記憶装置において、工程中のチャージアップを抑制し、しきい値電圧ばらつきを低減する。

【解決手段】 基板1上に形成された積層絶縁膜2に離散的に電荷を蓄積する不揮発性半導体記憶装置であって、基板の中層に埋め込まれた埋め込み絶縁膜1aと基板中の所定領域に形成された素子分離絶縁膜3とによって囲まれて島状に形成された活性領域上に形成されている。また、シリコン基板1上に形成された離散的に電荷を蓄積する積層絶縁膜2よりなるゲート絶縁膜と、ゲート電極4と、基板1の表面層にゲート電極4を挟持するように形成されたソース又はドレインとして機能する一対の拡散領域5とを有する。ここで、積層絶縁膜2は、下部酸化膜2aと、シリコン窒化膜2bと上部熱酸化膜2c及びCVD酸化膜2dから成る。

(もっと読む)

絶縁膜、および半導体装置

【課題】 酸素欠陥量の少ない絶縁膜を提供する。

【解決手段】 絶縁膜は、正の価数を有する構成元素の酸化物または酸窒化物を含み、構成元素の価数より大きな価数の添加元素を3×10-8at%以上1.6×10-3at%未満含む。

(もっと読む)

半導体メモリ素子およびその製造方法

【課題】 半導体メモリ素子の構造およびその製造方法を提供する。

【解決手段】 半導体基板21上に形成されたゲート積層物26と、前記半導体基板上におけるゲート積層物の下部に導電性不純物が注入されて形成され、チャンネル領域を介在して所定間隔離隔された第1および第2不純物領域27a,27bと、第1または第2不純物領域の側部の前記半導体基板上に形成されたコンタクト層34と、を含む半導体メモリ素子である。

(もっと読む)

誘電体膜の形成方法、及びこれを用いる半導体素子のキャパシタの形成方法

誘電特性及び漏れ電流特性を向上させることのできる半導体素子の誘電体膜の形成方法が提供される。本発明の実施形態によれば、誘電体膜の形成方法は、ウェーハ上に、連続的に形成されない厚さに酸化亜鉛(ZrO2)膜を形成するステップと、前記ZrO2膜が形成されていない前記ウェーハ上に、連続的に形成されない厚さに酸化アルミニウム(Al2O3)膜を形成するステップとを含む。 (もっと読む)

半導体装置の製造方法

【課題】 高誘電体膜上にシリコン含有の電極を有し、長期信頼性の優れたMISFET、MISキャパシタで成る高性能な半導体装置の製造を可能にする。

【解決手段】 半導体基板上に高誘電体膜を形成する工程、この高誘電体膜に対して酸化性雰囲気中の第1の熱処理(第1のPDA)を施す工程、第1のPDA後に、前記高誘電体膜表面に窒化シリコン層を形成する工程、前記窒化シリコン層により被覆された高誘電体膜および窒化シリコン層に対して第2の熱処理(第2のPDA)を施す工程、窒化シリコン層上にシリコン含有の半導体膜もしくは導電体膜を形成する工程、を通して高誘電体ゲート絶縁膜およびゲート電極等を形成することで、長期信頼性の優れた高性能のMISFET等が実現できる。

(もっと読む)

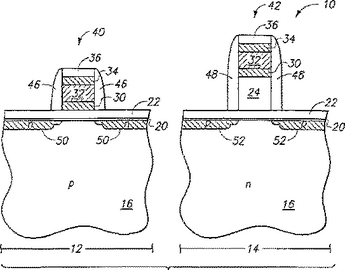

半導体MOS装置及びCMOS装置、コンデンサ、及び製造方法

回路装置の作製方法を提供する。導電性にドープされたシリコンと誘電材との間に厚さ20Å以下(または70以下のALDサイクルで生じた厚さ)の金属含有材を形成する。導電性にドープされたシリコンとしてn型を用いることができ、誘電材は高k誘電材を用いることができる。金属含有材は誘電層上へ直接形成でき、導電性にドープされたシリコンは金属含有材上へ直接形成できる。回路装置はコンデンサ構造体あるいはトランジスタ構造体とすることができる。回路装置がトランジスタ構造体である場合はCMOS装置中へ組み入れることができる。本発明による種々装置はメモリ構造体中へ組み入れられる他、電子システムへも組み入れることができる。  (もっと読む)

(もっと読む)

不揮発性半導体記憶装置及びその製造方法

【課題】SONOS構造の不揮発性メモリセルを有する不揮発性半導体記憶装置に関し、高速化・高集積化の2つの要求を同時に実現しうる不揮発性半導体記憶装置の構造及びその製造方法を提供する。

【解決手段】半導体基板内に形成されたチャネル領域と、チャネル領域上に、電荷保持絶縁膜を介して形成されたゲート電極と、第1の方向にチャネル領域を挟んで配置された第1のソース/ドレイン領域対と、第1の方向と交差する第2の方向にチャネル領域を挟んで配置された第2のソース/ドレイン領域対とを有し、第1のソース/ドレイン領域対を有する第1のメモリセルトランジスタと、第2のソース/ドレイン領域対を有する第2のメモリセルトランジスタとが、チャネル領域及びゲート電極を共用している。

(もっと読む)

強誘電体メモリ、多値データ記録方法、および多値データ読出し方法

【課題】 多値記録可能な強誘電体メモリ装置を提供する。

【解決手段】 第1導電型のチャネル領域を含む半導体基体と、前記半導体基体上に、前記半導体基体中のチャネル領域に対応して、強誘電体膜を介して形成されたゲート電極と、前記半導体基体中、前記チャネル領域の両側にそれぞれ形成された、第2導電型の第1および第2の拡散領域とを含む強誘電体メモリ装置において、前記強誘電体膜中は、前記第1の拡散領域の近傍に位置する第1の領域と、前記第2の拡散領域の近傍に位置する第2の領域と、前記第1および第2の領域の中間に位置する第3の領域を形成し、前記第1、第2および第3の領域に、独立に分極を誘起する。

(もっと読む)

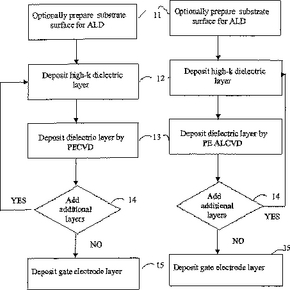

誘電体スタックの形成方法

本発明は、集積回路の中に誘電体スタックを形成する方法を提供し、(i)半導体基板上に高−k誘電体層を形成するステップと、(ii)高−k誘電体層を有する半導体基板を、プラズマ化学気相成長方法(PECVD)またはプラズマ原子層化学気相成長法(PEALCVD)において、窒素含有気相反応物およびケイ素含有気相反応物で処理するステップとを含む。さらに、本発明は、(i)少なくとも高―k材料を含む高―k誘電体層と、(ii)少なくともケイ素および窒素を含む誘電体層と、(iii)前記高―k誘電体層と前記誘電体層の間に配設された中間層とを含む集積回路中の誘電体スタックを提供し、前記中間層は前記高―k材料、ケイ素および窒素を含む。  (もっと読む)

(もっと読む)

原子層の積層方法、これを用いたゲート構造物の製造方法、及びキャパシタの製造方法

【課題】 原子層の積層方法、これを用いたゲート構造物の製造方法、及びキャパシタの製造方法が開示される。

【解決手段】 第1反応物質としてTEMAHを基板の上部に導入した後、第1反応物質の第1部分は基板上に化学吸着させ、第2部分は物理吸着させる。その後、第1反応物質の第1部分と酸化剤を化学的に反応させると、基板上にはハフニウムシリコン酸化物を含む第1固状物質が形成される。その後、第2反応物質としてTEMASを第1固状物質の上部に導入した後、第2反応物質の第1部分は第1固状物質上に化学吸着させ、第2部分は物理吸着させる。その後、第2反応物質の第1部分と酸化剤を化学的に反応させると、第1固状物質上にはシリコン酸化物を含む第2固状物質が形成されるので、基板上にはハフニウムシリコン酸化膜が形成される。

(もっと読む)

複合誘電膜の形成方法、及びこれを用いる半導体装置の製造方法

【課題】 基板と隣接する界面部位における窒素濃度を減少させた複合誘電膜を前記基板上に形成する方法を提供すること。

【解決手段】 半導体基板上に高誘電率物質から構成される第1誘電膜とシリコンを含む予備誘電膜を形成する。前記予備誘電膜を選択的にプラズマ窒化処理して前記予備誘電膜から窒素を含む第2誘電膜を修得する。前記プラズマ窒化処理を行う期間、窒素はイオンエネルギーによって前記第1誘電膜よりは前記予備誘電膜に含まれたシリコンと結合するので、前記半導体基板と前記複合誘電膜との間の界面部位にて窒素濃度を減少させることができる。

(もっと読む)

半導体不揮発性メモリへの情報の記録方法

【課題】半導体不揮発性メモリセルに対して電流効率よく情報の記録を行う方法を提供する。

【解決手段】半導体不揮発性メモリ101は、制御電極30と、第1主電極領域21及び第2主電極領域22とを有するトランジスタ、抵抗変化部23,26、及び電荷蓄積部を備えている。抵抗変化部は、半導体基板の表層領域のうち、第1及び第2主電極領域のうちの少なくとも一方の電極領域と、制御電極と対向するチャネル形成領域12とによって挟まれる部分に第1及び第2主電極領域よりも不純物濃度の低い第2導電型で設けられている。電荷蓄積部は、抵抗変化部上に設けられていて、絶縁層を含みかつ電荷を蓄積可能である。電荷蓄積部に、予め電荷を蓄積することで情報が消去されている半導体不揮発性メモリに情報を記録するに当たり、第1導電型がp型であってかつ第2導電型がn型の場合には、一方の主電極領域に正の高電圧を印加するステップと、他方の主電極領域を接地電圧とするステップと、制御電極に、チャネル形成領域が弱反転する正の電圧を印加するステップとを含んでいる。

(もっと読む)

半導体記憶装置およびその製造方法並びに携帯電子機器

【課題】微細化が容易な半導体記憶装置を提供する。

【解決手段】半導体基板211上には、ゲート絶縁膜214を介して単一のゲート電極217を形成している。ゲート電極217の両側には、第1,第2のメモリ機能体261,262を形成している。半導体基板211のゲート電極217側の表面部にはP型のチャネル領域472を形成し、チャネル領域472の両側にN型の第1,第2の拡散領域212,213を形成している。チャネル領域472は、第1,第2のメモリ機能体261,262下に位置するオフセット領域401と、ゲート電極217下に位置するゲート電極下領域402とで構成されている。オフセット領域401にP型の導電型を与える不純物の濃度は、ゲート電極下領域402にP型の導電型を与える不純物の濃度に比べて実効的に薄くなっている。

(もっと読む)

不揮発性半導体メモリ装置

【課題】 正負両極のいずれの高電界においてもリーク電流を低減することができ、且つ単独の高誘電体膜では困難な低電界から高電界の広い電界領域でリーク電流を抑制する。

【解決手段】 第1導電型の半導体基板10の主面上にトンネル絶縁膜11を介して選択的に形成されたフローティングゲート電極12と、フローティングゲート電極12上に電極間絶縁膜13を介して形成されたコントロールゲート電極14と、各ゲート電極12,14に対応して基板の主面に形成された第2導電型のソース・ドレイン領域15とを備えた不揮発性半導体メモリ装置であって、電極間絶縁膜13は、2種類以上の高誘電体材料13a,13b,13cによる3層以上の積層構造を有する。

(もっと読む)

ナノ構造単層の形成方法および形成デバイスならびにかかる単層を含むデバイス

ナノ構造配列の形成またはパターニング法が提供される。この方法は、ナノ構造会合基を含んでなるコーティング上での配列形成、レジストを使用するパターニングおよび/または配列形成を促進するデバイスの使用を含む。またナノ構造配列を含むデバイス(例えばメモリーデバイス)のように、ナノ構造配列の形成のための関連デバイスも提供される。 (もっと読む)

NROMデバイス

【課題】1セルに対して複数のビットが記憶可能な高性能のフラッシュメモリトランジスタを提供する。

【解決手段】NROMフラッシュメモリセルのアレイは、4F2あたり少なくとも2ビットを記憶するように構成される。スプリット縦型チャネルは、隣接する柱状部の各側面に沿って形成される。単一の制御ゲートが柱状部及び柱状部間のトレンチ内にわたって形成される。スプリットチャネルは、トレンチ底部のn+領域、又はトレンチ底部を覆うように形成されるチャネルによって接続され得る。各ゲート絶縁層は、チャネル長の増大により、他の電荷記憶領域から十分に分離した状態で電荷を記憶することができる。

(もっと読む)

縦型EEPROMNROMメモリデバイス

【課題】電荷捕獲領域の重なりがなく、過消去特性が改善された、より狭い素子間隔の高密度なNROMメモリアレイを製造する方法及び構造体を提供する。

【解決手段】NOR又はNAND型高密度メモリ構成において縦型NROMメモリセル及び縦型選択ゲートを有効に利用するNROM EEPROMメモリデバイス及びアレイが開示される。本発明に係るメモリの実施形態では、縦型選択ゲート及び縦型NROMメモリセルを用いて、NOR及びNAND型NROM構成のメモリセル列、メモリセグメント及びメモリアレイを形成する。これらNROMメモリセル構成によって、構成要素として選択ゲートを有するメモリデバイス又はメモリアレイをより高密度にすることが可能となる。これらメモリデバイス又はメモリアレイにおいては、半導体製造プロセスによって作製可能な加工寸法を利用することができ、かつ、典型的なマルチビットNROMセルにおいて存在する電荷分離に関する問題を被ることがない。さらに、上述のメモリセル構造体は、NROMメモリセルからそれらに関連したビット/データ線及び/又はソース線とを絶縁する選択ゲートの後ろに、NROMメモリセルを配置することによって、擾乱及び過消去問題を軽減することが可能となる。

(もっと読む)

極薄シリコンにおけるNROM型フラッシュメモリデバイス

【課題】SOI技術を取り入れたCMOSデバイスにおける浮遊ボディの影響を抑制可能とする。

【解決手段】極薄シリコン・オン・インシュレータ構造においてNROMフラッシュメモリセルを実現する。平面型デバイスでは、ソース/ドレイン領域間のチャネルが通常時に完全空乏化されている。ソース/ドレイン領域と上方のゲート絶縁層との間に酸化物層を形成することで絶縁層を設ける。制御ゲートがゲート絶縁層の上部に形成される。縦型デバイスでは、ソース/ドレイン領域に側面が接する酸化物柱状体を基板から延伸させる。エピタキシャル再成長により、酸化物柱状体の側面に沿って極薄シリコンボディ領域が形成される。本構造の上部には、第2のソース/ドレイン領域が形成される。さらにその上部にゲート絶縁層及び制御ゲートが形成される。

(もっと読む)

自己整合型電荷分離構造NROMフラッシュメモリ

【課題】電荷捕獲領域が重ならずにセルを小さくすることが可能なトランジスタを提供する。

【解決手段】窒化物リードオンリーメモリ(NROM)セルは、窒化物層を有し、前記窒化物層は、トランジスタの中心部の下方に配置されない。前記窒化物層を有するゲート絶縁層は、2つの部分を有する。各部分は、構造分離された(structurally defined and separated)電荷捕獲領域を有する。電荷は、トランジスタの動作方向に応じて、ある特定の捕獲領域に蓄積される。前記ゲート絶縁層の前記2つの部分は、ポリシリコンゲート構造体の中間部分から外側部分を分離する。

(もっと読む)

601 - 619 / 619

[ Back to top ]