Fターム[5F083LA21]の内容

半導体メモリ (164,393) | レイアウト・回路設計(平面図中心) (10,937) | コンタクトの配置レイアウト (1,397)

Fターム[5F083LA21]に分類される特許

1,381 - 1,397 / 1,397

記憶素子

【課題】 容易にかつ高密度に製造することが可能となる構成の記憶素子を提供する。

【解決手段】 2つの電極1,4の間に記録層2,3を有して成り、これら2つの電極1,4に極性の異なる電位を印加することにより、可逆的に記録層2,3の抵抗値が変化する抵抗変化素子10によりメモリセルが構成され、隣接する複数のメモリセルにおいて、抵抗変化素子10の記録層を構成する少なくとも一部の層2,3が同一層により共通に形成されている記憶素子を構成する。

(もっと読む)

スタガ配置のメモリ・セル・アレイ

セルをアレイ中に配置する方法が開示されている。方法は、第1のアレイ中にセルを複数回(600、602、604)配置する工程を含む。セルは、また第2のアレイ中にも複数回(606、608、610)配置される。第2のアレイは、第1のアレイからオフセット距離(O2)だけ離して隣接して配置される。  (もっと読む)

(もっと読む)

半導体装置

【課題】 SRAMセルにMIMノードキャパシタを備えた構造のものであって、このMIMキャパシタを簡単な構造で形成できソフトエラー対策を施すことができるようにする。

【解決手段】 シリコン半導体基板1に対して垂直柱状に形成された第1および第2のコンタクトプラグP1およびP2の上に第1のノード接続導電層NC1が形成されている。第3および第4のコンタクトプラグP3およびP4の上に第2のノード接続導電層NC2が形成されている。これらの第1および第2のノード接続導電層NC1およびNC2の上にキャパシタ絶縁膜CIおよびキャパシタ電極層CEが形成されている。

(もっと読む)

ストラップ領域を有する不揮発性の半導体メモリ素子及びその製造方法

【課題】 ストラップ領域を有する不揮発性の半導体メモリ素子及びその製造方法を提供する。

【解決手段】 メモリセルアレイ領域、及びメモリセルアレイ領域に均一電圧を提供するストラップ領域を備える不揮発性の半導体メモリ素子であり、ストラップ領域では、メモリセルアレイ領域のワードライン及びソースラインと分離されないように、ワードライン及びソースラインがロー方向に延びて、かつ一字型に形成されており、ワードライン及びソースラインのそれぞれには、ワードラインコンタクト及びソースラインコンタクトが形成されている。これにより、本発明は、ワードライン間に発生するブリッジ現象を防止でき、容易にストラップ領域を形成できる。

(もっと読む)

シングルイベントアップセットに対する抵抗力を増加する集積回路構造

フィールドプログラマブルゲートアレイ(「FPGA」)の集積回路(「IC」)デバイスのコンフィギュレーション・メモリセル(「CRAM」)は、シングルイベントアップセット(「SEU」)に対する増加された抵抗力を与えられる。CRAMの入力ノードのゲート構造の一部分は、そのゲート構造の残りの部分の名目上のサイズに対して、サイズが増加される。拡大されたゲート構造の部位はICのNウェル領域に容量的に近くに配置され、別の部位はICのPウェル領域に容量的に近くに配置される。この配置は、その入力ノードのロジックレベルに関係なく、その入力ノードに、SEUに抵抗するための増加された静電容量を与える。本発明はまた、SEUへの抵抗力を増加させることが所望される任意のタイプのメモリセルの任意のノードに対しても応用可能である。  (もっと読む)

(もっと読む)

半導体記憶装置

【課題】 1交点方式(オープンビット線型)のダイナミック型RAMにおいて、隣接するビット線間に生じる干渉ノイズを有効に減少させる。

【解決手段】 センスアンプ列7を中心に左右にサブアレイ8、8が配置される。この各サブアレイは多数のダイナミック型メモリセルMC…を有する。センスアンプ列7の左方及び右方に位置するサブアレイ8、8において、同一行のビット線同士(BL0、NBL0)〜(BLn、NBLn)により相補のビット線対が構成されていて、オープンビット線型となっている。各サブアレイ8、8において、各ビット線BL0〜BLn、NBL0〜NBLn間には、各々、これらのビット線と平行に且つ同一配線層に形成された第1の配線パターンSLDが配置される。これらの配線パターンSLDは全て電源電位などの固定電位に設定される。

(もっと読む)

半導体装置の製造方法

【課題】 SRAMセルのサイズが縮小化された場合、ゲート電極配線の抵抗要素の抵抗値を調整してSRAMセルを形成できるようにする。

【解決手段】 SRAMセルの製造時において、1回目に不純物イオンを注入するときにはイオン濃度を比較的高く低加速電圧の条件でイオン注入し、ソース/ドレイン拡散層13を形成する。2回目に不純物イオンを注入するときには、イオン濃度を比較的低く高加速電圧の条件でイオン注入し、第1の多結晶シリコン膜6の抵抗値を調整する。

(もっと読む)

不揮発性半導体記憶装置

【課題】配線間の容量カップリングに起因する誤読み出しを防止する。

【解決手段】ブロックBLOCKi−1,BLOCKi内には、それぞれ選択ゲート線SG1(149 )が配置される。シャント領域QQには、ブロックBLOCKi−1内の選択ゲート線SG1(149 )に対するコンタクト部X1が設けられている。選択ゲートバイパス線21i−1は、ブロックBLOCKi−1内の選択ゲート線SG1(149 )に接続されるものであるが、ブロックBLOCKi−1に隣接するブロックBLOCKi内に配置されている。

(もっと読む)

半導体記憶装置

【課題】 1交点方式(オープンビット線型)のダイナミック型RAMにおいて、隣接するビット線間に生じる干渉ノイズを有効に減少させる。

【解決手段】 センスアンプ列7を中心に左右にサブアレイ8、8が配置される。この各サブアレイは多数のダイナミック型メモリセルMC…を有する。センスアンプ列7の左方及び右方に位置するサブアレイ8、8において、同一行のビット線同士(BL0、NBL0)〜(BLn、NBLn)により相補のビット線対が構成されていて、オープンビット線型となっている。各サブアレイ8、8において、各ビット線BL0〜BLn、NBL0〜NBLn間には、各々、これらのビット線と平行に且つ同一配線層に形成された第1の配線パターンSLDが配置される。これらの配線パターンSLDは全て電源電位などの固定電位に設定される。

(もっと読む)

半導体記憶装置およびダミーセルの回路のレイアウト

【課題】 メモリアレイと、センスアンプ回路と、レプリカビット線に接続されたレプリカ回路、ダミーセルおよびセンスアンプ制御回路とを有する半導体記憶装置であって、レプリカビット線をダミーセルのリーク電流により速く引き抜いてしまい、所望のセンスアンプ起動タイミングが得られない。

【解決手段】 ダミーセル109Bが2つの直列に接続されたオフ状態のトランジスタ501、502を含み、片方を定電圧源に、もう片方をレプリカビット線REPBLに接続する。これによりレプリカビット線REPBLからダミーセル109Bへのリーク電流を抑え、最適な起動タイミングをセンスアンプ回路に提供できる。

(もっと読む)

半導体記憶装置

SRAMメモリセルをFD-SOIトランジスタで構成し、駆動トランジスタを構成するSOIトランジスタの埋め込み酸化膜の下の層の電位を制御して、メモリセルの性能を向上させる。

【課題】

低電源電圧状態でのSRAM回路の性能を向上させる。

【解決手段】

FD-SOIトランジスタを用いて構成されたSRAMメモリセルにおいて、駆動トランジスタのBOX層下のウエル電位を制御することでVthを制御して電流を増加させて、メモリセルの安定動作を可能とする。

(もっと読む)

分離領域上に消去ゲートを有する不揮発性メモリ

本発明は、不揮発性メモリ装置及びそのような装置の製造方法を提供する。この装置は、浮遊ゲート(16)と、制御ゲート(19)と、分離した消去ゲート(10)とを備える。消去ゲート(10)は、基板(1)内に設けられた分離領域(2)中に、又はその上に設けられる。そのため消去ゲート(10)は、セル・サイズを増加させない。消去ゲート(10)と浮遊ゲート(16)との間の容量は、制御ゲート(19)と浮遊ゲート(16)との間の容量に比べて小さく、消去ゲート(10)と浮遊ゲート(16)との間の酸化物層を介してファウラー・ノルドハイム・トンネルによって浮遊ゲート(16)の帯電が消去される。  (もっと読む)

(もっと読む)

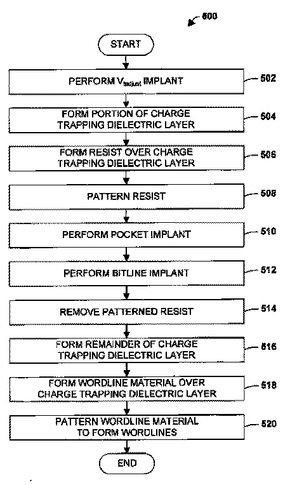

SONOSメモリセルの相補ビット妨害および蓄電の改善のためのポケット注入

デュアルビットメモリコアのアレイの少なくとも一部を形成する方法が開示される。最初に、電荷トラップ誘電層(608)の一部が基板(602)上に形成され、電荷トラップ誘電層(608)の一部の上にレジスト(614)が形成される。レジスト(614)がパターニングされ、ポケット注入(630)が所定の角度で実行され、基板(602)内にポケット注入部(620)が形成される。次に、基板(602)内に埋込みビット線(640)を形成するためにビット線注入(634)が実行される。次に、パターニングされたレジストが除去され、電荷トラップ誘電層(608)の残部が形成される。電荷トラップ誘電層の残部の上にワード線の材料(660)が形成されて、それはビット線(640)上にワード線(662)を形成するためにパターニングされる。ポケット注入部(620)は、特に、微細化によって生じるおそれのある相補ビット妨害(CBD)を軽減するのに役立つ。このように、ここに記載する発明思想により、半導体デバイスを小型化でき、高い実装密度を実現することができる。  (もっと読む)

(もっと読む)

アレイ状に配置された垂直型カーボン・ナノチューブ電界効果トランジスタを製造する方法、並びに、それによって形成された電界効果トランジスタ及びアレイ

【課題】 カーボン・ナノチューブ電界効果トランジスタと、カーボン・ナノチューブ電界効果トランジスタのアレイと、デバイス構造体とを製造するための方法、及び、該方法によって形成されたデバイス構造体のアレイを提供する。

【解決手段】 本方法は、ゲート電極層と、各々がソース/ドレイン・コンタクトと電気的に結合された触媒パッドとを含む積層構造体を形成することを含む。ゲート電極層は多数のゲート電極に分割され、少なくとも1つの半導体カーボン・ナノチューブが、化学気相堆積プロセスによって触媒パッドの各々の上に合成される。完成したデバイス構造体は、ゲート誘電体によって覆われた側壁を有するゲート電極と、該ゲート電極の該側壁に隣接する少なくとも1つの半導体カーボン・ナノチューブとを含む。ソース/ドレイン・コンタクトを半導体カーボン・ナノチューブの両端と電気的に結合することによって、デバイス構造体が完成する。多数のデバイス構造体は、メモリ回路又は論理回路のいずれかとして構成することができる。

(もっと読む)

セルフタイミング回路を有する半導体メモリ

半導体メモリのセルフタイミング回路(61)において、第1の状態に設定されたセルフタイミング用ダミーメモリセル(SDMC11、12)及び第1の状態と反対の第2の状態に設定された負荷用ダミーメモリセル(LDMC11、12)を有するダミービット線(XDBL1)と、第3の状態に設定されたセルフタイミング用ダミーメモリセル(SDMC21、22)及び前記第3の状態と同一の第4の状態に設定された負荷用ダミーメモリセル(LDMC21、22)を有するダミービット線(XDBL2)と、ダミービット線(XDBL1、XDBL2)の電位の変化速度の差に対応する期間だけ遅延させて、セルフタイミング信号(SLF)を出力するタイミング制御回路(62)とを備える。 (もっと読む)

半導体集積回路装置

記憶回路STCと比較回路CPとを用いたメモリセルで構成されるメモリアレイにおいて、比較回路CPを構成する複数のトランジスタのうち、ゲート電極がサーチ線に接続されるトランジスタのソースまたはドレインのいずれか一方の電極を高電圧にプリチャージされる方のマッチ線HMLrに接続する。また、マッチ線判定回路MDrを低電圧にプリチャージされるマッチ線LMLrに配置して、情報の比較結果に応じてこのマッチ線に発生した比較信号電圧を弁別する。このようなメモリアレイ構成と動作により、マッチ線対におけるサーチ線駆動雑音の影響を回避しつつ、低電力かつ高速に比較動作を行うことができる。このため、検索動作を高速に行うことが可能な低電力コンテント・アドレッサブル・メモリを実現することができる。 (もっと読む)

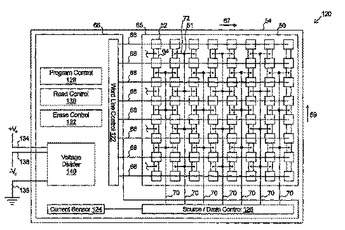

スタガー式ローカル接続構造を持つメモリセルアレイ

メモリセルアレイ(50)は、半導体基板(54)に製造された、2次元アレイのメモリセル(52)を含む。メモリセル(52)は、行方向(67)を形成する複数の行と、列方向(69)を形成する複数の列で並べられている。メモリセル(52)の各列は、複数の交互に配置されたチャネル領域(58)及びソース/ドレイン領域(64)を含む。各ソース/ドレイン領域(64)上には導電性インターコネクト(72)が配置されており、この導電性インターコネクト(72)はただ1つのその他のソース/ドレイン領域(64)に結合する。この1つのソース/ドレイン領域(64)とは、その列に隣接する第2の列に存在する領域である。導電性インターコネクト(64)は、1つおきの導電性インターコネクト(64)がその列の右側に隣接する列に接続するように、また、1つおきの導電性インターコネクトが、その列の左側に隣接する列に接続するように、配置される。複数のソース/ドレインコントロールライン(70)は、隣接するメモリセル(52)の列間に延在し、また、その隣接する列と列との間を結合する各導電性インターコネクト(72)に電気的に結合する。  (もっと読む)

(もっと読む)

1,381 - 1,397 / 1,397

[ Back to top ]