Fターム[5F083MA18]の内容

Fターム[5F083MA18]に分類される特許

201 - 220 / 481

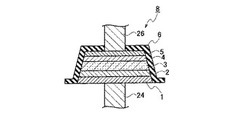

強誘電体メモリ装置およびその製造方法

【課題】酸素バリア性と水素バリア性を有し、強誘電体キャパシタの構造が簡単で製造方法が容易な強誘電体メモリ装置およびその製造方法を提供する。

【解決手段】プラグ電極24に接続された導電性バリア膜1と、導電性バリア膜1上に配置され、導電性バリア膜1を介してプラグ電極24に接続された下部電極2と、下部電極2上に配置された強誘電体膜3と、強誘電体膜3上に配置された上部電極4と、上部電極4上に配置された導電性水素バリア膜5と、導電性水素バリア膜5上に配置され、導電性水素バリア膜5を介して上部電極4に接続されたVIA電極26と、導電性水素バリア膜5上、および導電性バリア膜1,下部電極2、強誘電体膜3,上部電極4,および導電性水素バリア膜5の側壁上に配置された絶縁性水素バリア膜6とを備える。

(もっと読む)

強誘電体素子及びその製造方法

【課題】強誘電体キャパシタを含む強誘電体素子において、強誘電体膜の配向方向を制御して従来よりも残留分極特性を向上させることを目的とする。

【解決手段】基板10の上方にストライプ状の凹凸を有する第1絶縁膜11を形成し、その上にHDPCVD法によりテーパ部12aを有する下地絶縁膜12を形成する。この下地絶縁膜12の上に、下地絶縁膜の上面に垂直な方向が(111)方向となるように自己配向したPt膜を形成しこれを平坦化して第1導電膜14aを形成する。その上に、強誘電体膜15としてPZT膜を形成し、その上に上部電極16を形成する。PZT膜は第1導電導電膜14aと同じ方向に配向するため、分極軸である(001)方向が、上下の電極間を結ぶ方向(印加電界方向)に揃う。これにより強誘電体膜15の単位面積当たりの残留分極量が増加し、強誘電体素子の残留分極特性が向上する。

(もっと読む)

半導体装置及びその製造方法

【課題】コンタクトホールの開口が容易であり、歩留まりが改善され、キャパシタ特性が向上した強誘電体メモリ等の半導体装置の製造方法を提供する。

【解決手段】半導体基板1上に層間絶縁膜6を形成する工程と、層間絶縁膜6を貫通し半導体基板表面を露出する第1のホール及び第2のホールを形成する工程と、第1のホール及び第2のホールにそれぞれ導電膜を埋め込んで第1のプラグ10及び第2のプラグ10を形成する工程と、層間絶縁膜6上に第1のプラグ10と接続し、順に積層された導電性バリア膜、下部電極、誘電体膜、及び上部電極を有するキャパシタCを形成する工程と、キャパシタC、層間絶縁膜6、及び第2のプラグ10を覆うように少なくとも1つのAlON層を有する水素バリア膜20を形成する工程と、を備える。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】製造コストを低減し且つチップサイズを大きくすることなく容量素子部の容量を大きくする。

【解決手段】半導体装置は、フローティングゲート及びコントロールゲートを備える。半導体装置は、容量素子部において、半導体基板上に形成されたゲート絶縁膜101と、ゲート絶縁膜101上に形成された下部電極102cと、下部電極102c上に形成された、下部電極102cを露出する開口部を有するキャップ絶縁膜103と、キャップ絶縁膜103の側面上及び開口部により露出された下部電極102c上に形成されたゲート間絶縁膜106と、ゲート間絶縁膜106上に形成された上部電極108と、を備える。

(もっと読む)

強誘電体薄膜及び常誘電体薄膜の形成方法、半導体デバイス

【課題】ガラス基板あるいはプラスチック基板の絶縁素材基板上への強誘電体薄膜及び常誘電体薄膜の形成方法、およびそれを利用した強誘電体メモリの製造方法を提供する。

【解決手段】絶縁素材基板1上にスピンコート法により非晶質のPZT薄膜2を堆積し、ライン状に整形された532nmの波長をもつ連続発振レーザビーム4を酸化物2の表面3にスキャン照射して結晶化させることで、優れた強誘電特性が得られる。対象となる酸化物2に集中的にしかも短時間で最適な熱を与えることができるため、基板1や他の層の温度上昇を押さえることが可能である。また、レーザービーム照射により酸化膜の温度が急激に上昇しても短時間での処理となり、蒸発などによる組成のずれを最小限にすることが可能である。特にガラス基板あるいはプラスチック基板の絶縁素材基板1を用いるため、基板への熱損失が少なく、有効に結晶化を行うことができる。

(もっと読む)

半導体装置及びその製造方法

【課題】ビット線及びワード線の抵抗の低い半導体装置、及びその製造方法を提供する。

【解決手段】第1のシリサイド層及び第1のポリシリコン層6を含むビット線BLと、ビット線BL上に形成された基部14a及び基部14aに立設された柱状のボディ部14cを有する第2のシリコン層14と、基部14aに形成されたソースドレイン領域SD1と、ビット線BLの一部を貫通して基板1と第2のシリコン層14を連結する第1のシリコン層13と、ボディ部14cを覆うゲート絶縁膜17を介してボディ部14cを覆うゲート電極18と、ボディ部14c上に形成されてゲート電極18に接続される第2のシリサイド層及び第2のポリシリコン層23を含むワード線WLと、ワード線WLを貫通してボディ部14cの上方に接続されるソースドレイン領域SD2を有する第3のシリコン層34とを具備してなる。

(もっと読む)

半導体記憶装置及びその製造方法

【課題】DRAMセルのキャパシタに適用できる膜厚まで薄膜化しても、高い誘電率を得るのに十分な結晶性を確保する誘電体膜を提供する。

【解決手段】トランジスタとワード線3、ビット線6がシリコン基板1上に形成されており、そのトランジスタの拡散層15の片側から、ポリシリコンで形成された導電性プラグ5が引き出されている。その上部に、さらに第2の導電性プラグ8が接続されており、これは反応バリア層9を介して円筒型のキャパシタ下部電極10につながっている。下部電極10の表面には、ニッケルまたはコバルトを0.5%から10%の範囲で添加した二酸化チタン11が形成されており、上部電極12と下部電極10、および二酸化チタン11でキャパシタが構成されている。

(もっと読む)

半導体記憶装置

【課題】動作速度が速くかつ単位セルサイズの小さい強誘電体メモリを提供する。

【解決手段】半導体記憶装置は、ワード線と、ビット線と、プレート線と、ビット線に接続されたサブビット線と、強誘電体キャパシタの一端に接続されたドレイン、および、ワード線に接続されたゲートを含むセルトランジスタと、強誘電体キャパシタおよびセルトランジスタを含む複数のメモリセル、リセットトランジスタ、および、ブロック選択トランジスタを含むセルブロックであって、セルトランジスタのソースがプレート線に接続され、強誘電体キャパシタの他端がサブビット線に接続され、ブロック選択トランジスタのソースおよびドレインがそれぞれサブビット線およびビット線に接続され、リセットトランジスタのソースがプレート線に接続され、リセットトランジスタのドレインがサブビット線に接続されたセルブロックとを備え、複数のセルブロックによってメモリセルアレイを構成する。

(もっと読む)

半導体装置及びその製造方法

【課題】メモリセルにおけるメモリキャパシタである第1のキャパシタと、メモリキャパシタ以外の第2のキャパシタとを混載してなる半導体装置において、大容量化及び微細化、低電圧化という第1のキャパシタに対する要請と、大容量化及び高耐圧化という第2のキャパシタに対する要請という異なる要求を共に十分に満たす。

【解決手段】下部電極51と上部電極52とにより強誘電体膜45を挟持してなり、情報の記憶容量に用いられる第1のキャパシタ30と、下部電極66と上部電極67とにより強誘電体膜64を挟持してなり、記憶容量以外の容量に用いられる第2のキャパシタ50と備えており、第1のキャパシタ30と第2のキャパシタ50とは、半導体基板10の表面からの高さが相異なる層位置に形成されている。

(もっと読む)

半導体装置及び半導体装置の製造方法並びにデータ処理システム

【課題】動作特性の制御が容易で微細化に有利なトランジスタを有する半導体装置およびその製造方法並びにデータ処理システムを提供する。

【解決手段】活性領域K内に設けられたトレンチ100と、トレンチ100と第1素子分離領域S1との間の活性領域Kに形成されたフィン型チャネル領域185と、第1素子分離領域S1に埋設され、第1ゲート絶縁膜141を介してフィン型チャネル185と接する第1ゲート電極151と、トレンチ100に埋設され、第2ゲート絶縁膜191を介してフィン型チャネル185と接する第2ゲート電極225と、フィン型チャネル185と接続され、活性領域K内において第2ゲート電極225を挟んでトレンチ100の両側に位置するソース/ドレイン拡散領域241とを具備してなるトレンチゲート型MOSトランジスタTrを有する半導体装置1を採用する。

(もっと読む)

半導体装置及びその製造方法

【課題】配向が優れた誘電体膜の存在に基づいて高いスイッチング電荷量を得ることができる半導体装置及びその製造方法を提供する。

【解決手段】Ir膜23を形成した後、このIr膜23上にIr酸化膜を形成する。次に、MOCVD法によりIr酸化膜上に初期PZT膜25aを形成すると共に、Ir酸化膜を還元によりIr膜24aに変化させる。次に、初期PZT膜25a上に、初期PZT膜25aよりも厚く、初期PZT膜25aよりも酸化度が高いコアPZT膜25bを形成する。

(もっと読む)

半導体装置及びその製造方法

【課題】ゾルゲル法又はスパッタ法により強誘電体膜等の容量絶縁膜を形成する場合であっても、その配向をより一層揃えながらリーク電流を抑制することができる半導体装置及びその製造方法を提供する。

【解決手段】Ir膜53上に柱状晶化しているIr酸化膜54aを形成した後、アモルファス状のIr酸化膜54bを形成する。次に、Ir酸化膜54b上にPt膜91を形成する。Ir酸化膜54bがどの方位にも配向していないため、Pt膜91は自己配向し、表面のミラー指数は(111)となる。次に、Pt膜91上に、スパッタ法により容量絶縁膜55を形成する。次に、酸素を含む雰囲気中でRTAを行うことにより、容量絶縁膜55の全体を柱状晶にする。容量絶縁膜55を構成する柱状晶は、Pt膜91の配向を引き継ぐため、その表面のミラー指数も(111)となる。また、Ir膜53中のIrの容量絶縁膜55への拡散はIr酸化膜54aにより抑制される。

(もっと読む)

金属膜作製装置及びキャパシタ製造装置及び強誘電体メモリ製造装置及び金属膜作製方法

【課題】貴金属薄膜を作製するため、ダメージを抑える金属膜(特に高融点金属)を基板の、特に微細な穴の底面だけに、均一にしかも高速に作製することができる金属膜作製装置とする。

【解決手段】タンタル(Ta)製の被エッチング部材11が備えられたチャンバ1内にハロゲンを含有する原料ガスとしてのCl2ガスを供給し、被エッチング部材11に対してプラズマを発生させCl2ガスで被エッチング部材11をエッチングすることにより被エッチング部材に含まれるTa成分とCl2ガスとの前駆体TaClを生成し、表面に微細穴(トレンチ)が形成された基板側の温度を被エッチング部材の温度よりも低くし、トレンチの(底面の金属被覆厚/壁面の金属被覆厚)である被覆率を1より大きくするような状態にCl2ガス成分量を調整してトレンチの底面だけにTa成分を成膜させる。

(もっと読む)

半導体装置及びその製造方法

【課題】ゾルゲル法又はスパッタ法により強誘電体膜等の容量絶縁膜を形成する場合であっても、その配向をより一層揃えることができる半導体装置及びその製造方法を提供する。

【解決手段】下部電極膜の一部であるアモルファス状のIr酸化膜54を形成した後、その上にPt膜91を形成する。Ir酸化膜54がどの方位にも配向していないため、Pt膜91は自己配向し、表面のミラー指数は(111)となる。次いで、Pt膜91上にPt膜92を形成する。Pt膜92はPt膜91の配向を引き継ぐため、Pt膜92の表面のミラー指数も(111)となる。その後、Pt膜92上に、スパッタ法により容量絶縁膜55を形成する。続いて、酸素を含む雰囲気中でRTAを行うことにより、容量絶縁膜55の全体を柱状晶にする。容量絶縁膜55を構成する柱状晶は、Pt膜92の配向を引き継ぐため、その表面のミラー指数も(111)となる。

(もっと読む)

強誘電体メモリ装置及びその製造方法

【課題】コンタクトホールへのプラグ導電部の埋設時などに、水素バリア膜と上部電極との界面を通って水素が侵入し、強誘電体膜が特性劣化してしまうのを防止した、強誘電体メモリ装置とその製造方法を提供する。

【解決手段】基板21上方に設けられた第1電極32、強誘電体膜33、第2電極34を有する強誘電体キャパシタ3と、強誘電体キャパシタ3の第2電極34の上面を覆って形成された水素トラップ膜4と、水素トラップ膜4及び強誘電体キャパシタの側面とを覆って設けられた絶縁性水素バリア膜5と、絶縁性水素バリア膜5を覆って設けられた層間絶縁膜6と、層間絶縁膜6と絶縁性水素バリア膜5と水素トラップ膜4とを貫通して第2電極34に通じるコンタクトホール70と、コンタクトホール70内に設けられたプラグ導電部7と、を含む強誘電体メモリ装置1。

(もっと読む)

半導体装置及びその製造方法

【課題】ビット線、ワード線の抵抗率を低くすることにより、低電力で安定した駆動特性を有する半導体装置、及びその製造方法を提供する。

【解決手段】ゲート電極とゲート電極に接すると共に第1不純物拡散領域よりも上の領域を第1の方向に延在する金属配線Aとを有するワード線と、第1不純物拡散領域の側面の少なくとも一部に接するように設けられた接続部と接続部に接すると共に半導体領域よりも下の領域を第1の方向と直交する第2の方向に延在する金属配線Bとを有するビット線と、を備えたことを特徴とする半導体装置。

(もっと読む)

強誘電体メモリ装置及びその製造方法

【課題】工数の増加及び強誘電体メモリ装置の特性劣化を生じさせることなく、コンタクトホールのアスペクト比が小さい強誘電体メモリ装置を実現できるようにする。

【解決手段】強誘電体メモリ装置は、基板11の上に形成された第1の層間絶縁膜13と、第1の層間絶縁膜13の上に選択的に形成された強誘電体キャパシタ本体22及び第2の層間絶縁膜21を含むメサ部24と、メサ部24の側壁上に形成されたサイドウォール25と、上部電極20の上面及びサイドウォール25と接してこれを覆う絶縁性の上部水素バリア膜26と、第1の層間絶縁膜13の上に形成され、上部水素バリア膜26を覆う第3の層間絶縁膜27と、メサ部24と間隔をおいて形成され、第1の層間絶縁膜13及び第3の層間絶縁膜27を貫通する配線コンタクトプラグ29とを備えている。

(もっと読む)

半導体装置及びその製造方法

【課題】コンタクトプラグ上にキャパシタが形成されるような構造に関して、新たな構造を提供する。

【解決手段】基板と、前記基板の上方のコンタクトホールに埋め込まれたコンタクトプラグと、前記コンタクトプラグ上に形成されており、前記コンタクトホールに埋め込まれた部分を有する下部電極と、前記下部電極の一部分上に形成された第1のキャパシタ絶縁膜と、前記下部電極の他の部分上に形成された第2のキャパシタ絶縁膜と、前記第1のキャパシタ絶縁膜上に形成された第1の上部電極と、前記第2のキャパシタ絶縁膜上に形成された第2の上部電極と、を備えることを特徴とする半導体装置。

(もっと読む)

セラミックス膜およびその製造方法、ならびに強誘電体キャパシタ、半導体装置、その他の素子

【課題】本発明の目的は、セラミックス膜の表面モフォロジを改善することができる、セラミックス膜の製造方法を提供することにある。

【解決手段】セラミックス膜の製造方法は、第1の原料液と、第2の原料液とを含むセラミックスの原料液を結晶化することにより、セラミックス膜を形成する工程を含む。前記第1の原料液と前記第2の原料液とは、種類が異なる関係にあり、前記第1の原料液は、強誘電体を生成するための原料液であり、前記第2の原料液は、ABO系などの酸化物を生成するための原料液であり、前記第1の原料液が含む溶媒と第2の原料液が含む溶媒とは、極性の異なる関係にあり、前記第1の原料液と前記第2の原料液が相分離した状態で成膜することにより、前記セラミックス膜の平面方向において、前記第1の原料液からなる第1の結晶が断続して形成され、前記第2の原料液からなる第2の結晶が前記第1の結晶相互間に介在するように形成される。

(もっと読む)

半導体装置及びその製造方法

【課題】 深さの異なる複数のコンタクトホールを有する構造であって、簡易な製造工程の下、基板に対するエッチングダメージを招来せず製造することが可能な半導体装置及びその製造方法を提供する。

【解決手段】 半導体基板1上の一部領域にフィールド酸化膜2を形成し、その後にフィールド酸化膜2の一部領域をエッチング処理して凹部構造32を形成し、その後に、少なくとも凹部構造32の底面を覆うように、フィールド酸化膜2の上層に下部電極7、酸化膜8、上部電極9を形成し、ソース・ドレイン拡散領域6を形成し、その後に全面に層間絶縁膜10を堆積する。そして、拡散領域6の上面が露出するように拡散領域6の上方領域に係る層間絶縁膜10をエッチングして第1コンタクトホール11aを形成すると共に、上部電極9の上面が露出するように凹部構造32の上方領域に係る層間絶縁膜10をエッチングすることで第2コンタクトホール11cを形成する。

(もっと読む)

201 - 220 / 481

[ Back to top ]