Fターム[5F083PR03]の内容

Fターム[5F083PR03]に分類される特許

1,161 - 1,171 / 1,171

金属系膜のエッチング加工方法および磁気記憶装置の製造方法

【課題】エッチングガスに塩素ガスと希ガスとの混合ガスを適切なる流量比で用いることで、残留塩素イオンによる悪影響を抑えてパターン形状が良好となるエッチング加工を可能とする。

【解決手段】白金もしくはマンガンを少なくとも含む金属系膜をエッチング加工する金属系膜(例えばPtMn膜113)のエッチング加工方法であって、金属系膜をエッチングする際のドライエッチングに用いるエッチングガスは塩素ガスと希ガスとの混合ガスからなり、混合ガスに対する塩素ガスの流量比は2%以上13%以下とすることを特徴とする。

(もっと読む)

ゲート型電界効果デバイス及びその製法

本発明はゲート型電界効果デバイスに関し、その製法にも関する。一例では、ゲート型電界効果デバイスはソース/ドレーン領域ペアを含み、チャンネル領域をそれらの間に有している。ゲートはソース/ドレーン領域間でチャンネル領域に近接して受領される。ゲートはソース/ドレーン領域間にゲート幅部を有している。ゲート誘電体はチャンネル領域とゲートに近接して受領される。ゲート誘電体は少なくとも2つの異なる領域をゲートの幅部に沿って有している。これら異なる領域はそれぞれ異なる誘電率kを有する2つの異質領域を提供するように異なる材料で提供される。 (もっと読む)

半導体構造、メモリ素子構造、及び半導体構造の形成方法

本発明は、垂直のソース/ドレイン領域(88)を囲むゲート線格子(94)を有する半導体構造(10)を含む。ある側面では、ソース/ドレイン領域は、ペアで提供され、各ペアのソース/ドレイン領域のうちの1つがディジットライン(120、122)に延伸し、もう1つのソース/ドレイン領域がキャパシタのようなメモリストレージ素子(145)に延伸してDRAMを形成することができる。ディジットラインに延伸するソース/ドレイン領域は、メモリストレージ素子(145)に延伸するソース/ドレイン領域とは同じ組成、または異なる組成を有することができる。本発明はさらに半導体構造を形成する方法を含む。典型的な方法では、第1の材料を含む格子は第2の材料の繰り返し領域を囲むように提供される。その後、前記第1の材料のうちの少なくとも一部はゲート線構造で置換去れ、また、本発明のうちの少なくとも一部は、垂直のソース/ドレイン領域を囲むゲート線格子を有する半導体構造を含む。ある側面では、ソース/ドレイン領域はペアで提供され、各ペアのソース/ドレイン領域のうちの1つはディジットラインまで延伸し、もう1つのソース/ドレイン領域はキャパシタのようなメモリストレージ素子まで延伸することができる。ディジットラインに延伸するソース/ドレイン領域は、メモリストレージ素子に延伸するソース/ドレイン領域とは同じ組成、または異なる組成を有することができる。本発明はさらに、第1の材料を含む格子が第2の材料の繰り返し領域を囲むように提供される方法を含む。その後、第1の材料のうちの少なくとも一部はゲート線構造で置換去れ、また、第2の材料のうちの少なくとも一部は垂直のソース/ドレイン領域で置換される。  (もっと読む)

(もっと読む)

不揮発性半導体記憶装置の製造方法

【課題】シリコン基板にダメージを与えることなく、ウェットエッチングにより剥離することなく、小さい径のトンネル窓を形成できる不揮発性半導体記憶装置の製造方法の提供。

【解決手段】第1に反射防止膜7を介してKrF線レジスト8を塗布する。これによりレジストの開口寸法自体を小さくすると共に密着性を向上させてウェットエッチング中の剥離を防止する。第2に反射防止膜7のドライエッチングの際に第1の絶縁膜2の途中でエッチングを止める。これにより反射防止膜7を除去すると共に第1の絶縁膜2をドライエッチングにより薄膜化することによってその後のウェットエッチングの時間を短くして基板面方向への広がりを抑制する。第3に第1の絶縁膜2をウェットエッチングにより除去する。これによりシリコン基板1にプラズマダメージが入ることがなくなり、トンネル絶縁膜の信頼性を向上させる。

(もっと読む)

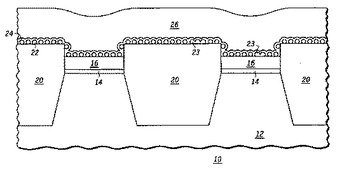

改良された表面形状を用いるメモリ構造の形成方法及びその構造。

半導体装置10のゲートカップリング比を増大させるため、超微細結晶等の個別素子22が浮遊ゲート16上に析出される。一実施形態において、個別素子22は、蒸気相中で予め形成され、静電気力によって半導体装置10に吸着される。一実施形態において、個別素子22は、それらが吸着されるチャンバとは異なるチャンバ内で予め形成される。更に別の実施例において、同じチャンバが全ての析出工程に使用される。界面層17は、必要に応じて、浮遊ゲート16と個別素子22との間に形成される。  (もっと読む)

(もっと読む)

無定形炭素層を含むマスキング構造

多数層を有するマスキング構造が形成される。そのマスキング構造は、無定形炭素層と該無定形炭素層上に形成されたキャップ層とを含む。無定形炭素層は透明無定形炭素を含む。キャップ層は非酸化物材料を含む。マスキング構造は、半導体装置の製作中、エッチング・プロセスにおけるマスクとして使用可能である。 (もっと読む)

DRAMアクセス・トランジスタ及び形成方法

【構成】自己整列リセス・ゲート構造及び形成方法が開示されている。最初に,絶縁用のフィールド酸化物領域を半導体基板内に形成する。半導体基板の上に形成された絶縁層内に複数のコラムを画定し,それに続いて,薄い犠牲酸化物層を半導体基板の露出領域の上に形成するが,フィールド酸化物領域の上には形成しない。次に,各コラムの側壁上,並びに犠牲酸化物層及びフィールド酸化物領域の一部分の上に誘電体を設ける。第1エッチングを行い,それにより,半導体基板内に第1組のトレンチを,またフィールド酸化物領域内に複数のリセスを形成する。第2エッチングを行い,それにより,コラムの側壁上に残っている誘電体残留部を除去し,かつ第2組のトレンチを形成する。次に,第2組のトレンチ内及びリセス内にポリシリコンを堆積させ,それにより,リセス導電性ゲートを形成する。 (もっと読む)

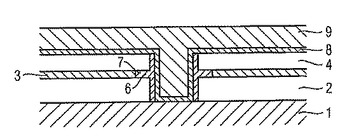

デバイス内にバリア層を有するコンタクトホールを形成する方法及び得られるデバイス

デバイスの下層(2)にコンタクトを形成する方法は、コンタクトホール(5)を形成するステップと、デバイスのコンタクトホール内にバリア材からなるコンタクトホールバリア層(7)を形成するステップと、コンタクトホールの底面のコンタクトホールバリア層をエッチングするステップと、コンタクトホール内にライナ材(8)を堆積するステップと、コンタクトホールに導電性材料(9)を充填するステップとを有する。半導体、受動素子、キャパシタ又はFeRAMなどのデバイスが上記方法に従って形成される。コンタクトホールの側壁にあるコンタクトホールバリア層(7)が、水素及び/又は酸素の側方拡散を抑制する。コンタクトホールバリア層は、ウェットエッチングプロセスによって生じる既存のバリア層(3)内のボイド(6)を充填するために上記プロセス後に、又は既存のバリア層への損傷を抑制するために上記プロセス前に行うことができる。

(もっと読む)

(もっと読む)

磁気抵抗効果型素子ならびにこれを用いた磁気記憶素子および磁気ヘッド

【課題】 ペロブスカイト型酸化物を用いて良好なトンネル接合を実現し、低磁場でも大きな磁気抵抗効果を発現する磁気抵抗効果型素子を提供する。

【解決手段】 式L2(A1-zRz)2An-1MnO3n+3+xにより表される組成を有し、結晶構造内に(L-O)2層を有する層状ペロブスカイト型酸化物と、この酸化物を挟むようにこれに接して形成された一対の強磁性体と、を含む磁気抵抗効果型素子とする。ただし、AはCa、SrおよびBaから選ばれる少なくとも1種の元素を、LはBi、TlおよびPbから選ばれる少なくとも1種の元素を、MはTi、V、Cu、Ru、Ni、Mn、Co、FeおよびCrから選ばれる少なくとも1種の元素を、Rは希土類元素をそれぞれ示し、nは1、2または3であり、x、zは、それぞれ、−1≦x≦1、0≦z<1により示される範囲内の数値である。

(もっと読む)

半導体記憶装置及びその製造方法

【課題】ビット線とセルコンタクト部の容量接続用コンタクトとのショートを防止し、容量接続用コンタクトとビット線とのマージンを大きくすることができる半導体記憶装置及びその製造方法の提供。

【解決手段】STIにより活性領域が分離形成された半導体基板上の第1の層間絶縁膜4に活性領域まで貫通するコンタクト孔5を設け、その内部に第1の層間絶縁膜上面よりも低い位置まで多結晶シリコン6を充填した後、多結晶シリコン上部にシリサイド膜12を形成し、第1の層間絶縁膜上の所定領域にポリサイド膜又はメタル膜を含むビット線7とビット線の上面及び側面にシリコン窒化膜を形成した後、ビット線で覆われていないコンタクト孔内部のシリサイド膜を除去することにより、シリンダ型容量と接続されるコンタクト孔内部の導電体とそのコンタクト孔に隣接するビット線とを分離する。その後、第2の層間絶縁膜10を堆積し、シリサイド膜を除去したコンタクト孔まで貫通するシリンダ型容量パターンを形成する。

(もっと読む)

強誘電体膜を有する半導体装置の製造方法

【課題】強誘電体膜をエッチングする際に生じる反応副生成物を形成される素子に悪影響を与えることなく除去する。

【解決手段】強誘電体膜をエッチングしたあと、燐酸水溶液を用いてウェット処理をする。レジストをマスクとして強誘電体膜をエッチングしたあと、レジストアッシング後またはアッシング前後の両方に燐酸水溶液を用いてウェット処理をする。

(もっと読む)

1,161 - 1,171 / 1,171

[ Back to top ]