Fターム[5F083PR10]の内容

半導体メモリ (164,393) | プロセス (23,970) | 側壁形成の利用で微細加工を行う (1,038) | 側壁の材料が絶縁膜(ゲート側壁は除く) (430)

Fターム[5F083PR10]に分類される特許

141 - 160 / 430

抵抗変化メモリ

【課題】可変抵抗素子の抵抗値ばらつきに起因する誤動作を抑制する抵抗変化メモリを提供する。

【解決手段】抵抗変化メモリは、第1の電極14、抵抗変化膜15、及び第2の電極16が積層された積層構造からなり、かつ記憶データに基づいて低抵抗状態又は高抵抗状態を取り得る可変抵抗素子17と、可変抵抗素子17の側面に設けられた絶縁膜19と、絶縁膜19の側面に設けられた導電膜からなり、かつ可変抵抗素子17に並列接続された固定抵抗素子20とを含む。

(もっと読む)

半導体装置及びその製造方法並びにデータ処理システム

【課題】ダミーシリコンピラーとゲートコンタクトプラグとがショートしてしまうことを防止する。

【解決手段】半導体装置10は、半導体基板1と、半導体基板1の主面に対して垂直に設けられたシリコンピラー14と、シリコンピラー14の側面の一部分を覆うゲート絶縁膜15Aと、シリコンピラー14の側面の残りの部分を覆う絶縁体ピラー15Bと、第1及び絶縁体ピラー15A,15Bを介してシリコンピラー14を覆うゲート電極16と、シリコンピラー14、第1及び絶縁体ピラー15A,15B、並びにゲート電極16の上方に設けられた層間絶縁膜30と、層間絶縁膜30に設けられたコンタクトホールに埋め込まれ、ゲート電極16及び絶縁体ピラー15Bに接するゲートコンタクトプラグGCとを備え、絶縁体ピラー15Bの横方向の膜厚TBは、ゲート絶縁膜15Aの横方向の膜厚TAに比べて厚くなっている。

(もっと読む)

半導体装置及びその製造方法

【課題】ゲートコンタクトプラグとシリコン基板とのショートを防ぐ。

【解決手段】半導体装置10は、半導体基板11と、半導体基板11の主面に対して垂直な側面を有するシリコンピラー14Bと、シリコンピラー14Bの側面を覆うゲート絶縁膜15Bと、半導体基板11の主面に対して垂直な内周側面16a及び外周側面16bを有し、ゲート絶縁膜15Bを介して内周側面16aとシリコンピラー14Bの側面とが対向するよう、シリコンピラー14Bの側面を覆うゲート電極16と、ゲート電極16の外周側面16bの少なくとも一部を覆うゲート電極保護膜17と、ゲート電極16及びゲート電極保護膜17の上方に設けられた層間絶縁膜30と、層間絶縁膜30に設けられたコンタクトホールに埋め込まれ、ゲート電極16及びゲート電極保護膜17に接するゲートコンタクトプラグGCとを備える。

(もっと読む)

ナノ構造ベースNANDフラッシュセルおよびその周辺回路の形成方法

ナノ構造に基づく電荷蓄積領域は、不揮発性メモリ装置に備えられており、選択ゲートおよび周辺回路の製造と一体に製造される。1つ以上のナノ構造コーティングは、メモリアレイ領域および周辺回路領域の基板に塗布される。選択ゲートや周辺トランジスタについての目標領域などの基板の不要な領域から、ナノ構造コーティングを除去するための様々な工程が、行われる。一例では、基盤のアクティブ領域にナノ構造を選択的に形成するために、自己組織化に基づく工程を用いて、1つ以上のナノ構造コーティングが形成される。自己組織化によって、ナノ構造コーティングのパターニングやエッチングを行うことなく、互いに電気的に分離されているナノ構造の個別のライン群を形成することができる。  (もっと読む)

(もっと読む)

パンチスルーアクセスを有する縦型不揮発性スイッチおよびその製造方法

不揮発性メモリセルにアクセスするための半導体装置が提供される。いくつかの実施形態においては、半導体装置は、ソース、ドレインおよびウェルを含む半導体層の縦型スタックを有する。半導体装置へのドレイン−ソースバイアス電圧の印加は、ウェルにわたってパンチスルー機構を生成し、ソースとドレインとの間の電流の流れを発生させる。  (もっと読む)

(もっと読む)

不揮発性半導体記憶装置

【課題】デポジッション膜を形成することなく、ゲートとコンタクトのショートを抑制する不揮発性半導体記憶装置を提供する。

【解決手段】不揮発性半導体記憶装置1のコントロールゲート14を、フローティングゲート13側に位置する第1側面と、第1側面の反対に位置する第2側面と、コントロールゲート14の第1側面側の上部に形成されたシリサイド領域22と、コントロールゲート14の第2側面側の上部に形成された突出部8とを含むように構成する。そのサイドウォール絶縁膜21は、シリサイド領域22を覆うことなく突出部8の少なくとも一部を被覆する第1部分と、第1部分から連続的に設けられ、第2側面に接触して第2側面を被覆する第2部分とを含むものとする。

(もっと読む)

半導体記憶装置及びその製造方法、並びに、データ処理システム及びデータ処理装置

【課題】選択素子としてダイオードを用いた半導体記憶装置の集積度を高めるとともに、結晶欠陥に起因するリーク電流を低減する。

【解決手段】半導体基板100の一部であり、それぞれpn接合ダイオードのアノード及びカソードの一方及び他方として機能する不純物拡散層103,104と、不純物拡散層104に接続された記録層PCと、不純物拡散層103上に設けられた筒状のサイドウォール絶縁膜106とを備える。不純物拡散層104の少なくとも一部及び記録層PCの少なくとも一部は、サイドウォール絶縁膜106に囲まれた領域内に形成されている。本発明によれば、ピラー状のpn接合ダイオードと記録層PCが自己整合的に形成されることから、集積度を高めることが可能となる。また、シリコンピラーが半導体基板の一部であることから、結晶欠陥に起因するリーク電流が低減される。

(もっと読む)

半導体装置及びその製造方法

【課題】4個の島状半導体を用いてSRAMを構成することにより、高集積なSGTを用いたSRAMからなる半導体装置を提供する。

【解決手段】第1の島状半導体層137の周囲上に少なくとも一部に接して第1のゲート絶縁膜187が存在し、第1のゲート絶縁膜187に第1のゲート電極178の一面が接し、第1のゲート電極178の他面に第2のゲート絶縁膜187が接し、第2のゲート絶縁膜187に少なくとも第2の半導体層141が接して、第1の島状半導体層137の上部に配置された第1の第1導電型高濃度半導体層161と、第1の島状半導体層137の下部に配置された第2の第1導電型高濃度半導体層162と、第2の半導体層141の上部に配置された第1の第2導電型高濃度半導体層154と、第2の半導体層141の下部に配置された第2の第2導電型高濃度半導体層156と、を有するインバータを用いてSRAMを形成する。

(もっと読む)

半導体装置及びその製造方法

【課題】4個の島状半導体を用いてSRAMを構成することにより、高集積なSGTを用いたSRAMからなる半導体装置を提供することを目的とする。

【解決手段】第1の島状半導体層の周囲上に少なくとも一部に接して第1のゲート絶縁膜が存在し、第1のゲート絶縁膜に第1のゲート電極の一面が接し、該第1のゲート電極の他面に第2のゲート絶縁膜が接し、第2のゲート絶縁膜に少なくとも第2の半導体層が接して、第1の島状半導体層の上部に配置された第1の第1導電型高濃度半導体層と、第1の島状半導体層の下部に配置された第2の第1導電型高濃度半導体層と、第2の半導体層の上部に配置された第1の第2導電型高濃度半導体層と、第2の半導体層の下部に配置された第2の第2導電型高濃度半導体層と、を有することを特徴とするインバータを用いたSRAMにより、上記課題を解決する。

(もっと読む)

半導体装置及びその製造方法

【課題】導電層を自己整合的に形成する場合において、第1の拡散層コンタクトプラグのコンタクトマージンを比較的大きく取る。

【解決手段】半導体装置10は、第1のシリコンピラー14Aと、第1のシリコンピラー14Aの上面に設けられ、導電性材料が充填されたスルーホール30aを有する層間絶縁膜30と、スルーホール30aの上側開口部に設けられた第1の拡散層コンタクトプラグDC1とを備え、スルーホール30aの下側開口部の面積は前記第1のシリコンピラー14Aの上面の面積に等しくなっているとともに、スルーホール30aの上側開口部の面積はスルーホール30aの下側開口部の面積より大きくなっており、それによって、スルーホール30a内の導電性材料の第1の拡散層コンタクトプラグDC1との接続面の面積が第1のシリコンピラー14Aの上面の面積より大きくなっている。

(もっと読む)

半導体記憶装置およびその製造方法

【課題】ビット線コンタクト内の電気抵抗、およびビット線コンタクトとソース・ドレイン領域の接続部分の電気抵抗の小さい半導体記憶装置およびその製造方法を提供する。

【解決手段】半導体記憶装置100は、素子分離領域3により区画された活性領域2を有する半導体基板1と、活性領域2上に形成され、直列接続されたスタックド・ゲート型の複数のメモリセルトランジスタと、活性領域2上に形成され、複数のメモリセルトランジスタの両端に接続された選択トランジスタと、活性領域2中の選択トランジスタに属するソース・ドレイン領域5に接続された、下部のチャネル幅方向の垂直断面の形状が裾引き形状であるビット線コンタクト8と、を有する。

(もっと読む)

不揮発性半導体記憶装置の製造方法

【課題】MONOS型の不揮発性半導体記憶装置において、ONO端部に発生する加工ダメージの影響を緩和し、電荷保持特性の劣化を抑制する。

【解決手段】不揮発性半導体記憶装置の製造方法は、半導体基板上にONO積層膜104及び犠牲窒化膜105をこの順に形成する。次に、犠牲窒化膜105及びONO積層膜104を選択的に除去して、列方向に延伸する複数のビット線形成領域を開口する開口部を形成する。次に、開口部を介して不純物を導入することにより、半導体基板100の表層部に、列方向に延伸する複数のビット線拡散層108を形成する。次に、犠牲窒化膜105の上面を露出させる一方で開口部の内部を埋め込むビット線絶縁膜110を形成する。次に、犠牲窒化膜105を除去する。次に、少なくともビット線上絶縁膜110の側面上に、HTO膜111を形成する。行方向に延伸する複数のワード線114を形成する。

(もっと読む)

集積回路の製造において複数の導電線を形成する方法、導電線アレイを形成する方法、および集積回路

集積回路の製造において導電線対を形成する方法は、基板上に受けられるダマシン材料にトレンチを形成することを含み、導電性材料34a/35aが、そのダマシン材料を覆ってそしてトレンチ内へ蒸着されてそのトレンチを過充填する。その導電性材料は、少なくともダマシン材料へと戻すように除去されて、そのトレンチ内に残っている導電性材料の少なくともいくらかが残される。エッチングがトレンチ内で導電性材料を通って縦方向に処理されて、トレンチ内に少なくとも第1および第2の導電線の長さの大部分に沿って横断面図において互いにミラー像となる第1および第2の導電線が形成される。他の装いが考えられる。  (もっと読む)

(もっと読む)

不揮発性半導体記憶装置及びその製造方法

【課題】周辺回路領域の電界効果トランジスタのゲート電極の角部の形状を改善する。

【解決手段】本発明の例に係わる不揮発性半導体記憶装置は、メモリセルアレイ領域と、メモリセルアレイ領域の周辺に形成される周辺回路領域とを具備し、周辺回路領域は、素子領域AAと、素子領域AAを取り囲む素子分離領域10と、素子領域AA上に形成され、チャネル幅方向のゲート電極13の端部及び角部が素子分離領域10上に形成される電界効果トランジスタとを有し、ゲート電極13の角部の曲率半径rは、チャネル幅方向の素子領域AAの端部からチャネル幅方向のゲート電極13の端部までの幅よりも小さく、かつ、85nmよりも小さい。

(もっと読む)

半導体装置の製造方法

【課題】絶縁膜界面の汚染を防止し、半導体基板とコントロールゲートの間の絶縁膜の破壊を抑制する。

【解決手段】半導体装置の製造方法は、半導体基板2の第1表面領域C1上にゲート絶縁膜4を介してフローティングゲート5を形成する工程と;第1表面領域C1に隣接する第2表面領域C2及びフローティングゲート5の端部を覆うようにトンネル絶縁膜8aを形成する工程と;トンネル絶縁膜8aを覆い、第2表面領域C2の上方が厚く、フローティングゲート5の上方が薄くなるように第1酸化膜33を形成する工程と;第1酸化膜33とフローティングゲート5上のトンネル絶縁膜8aの表面とをエッチバックする工程と;第2表面領域C2上の第トンネル絶縁膜8a上にコントロールゲート9を形成する工程とを具備する。

(もっと読む)

半導体装置の製造方法および半導体装置

【課題】側壁転写加工技術を用いる場合に、転写用のマスクが非対称な形状となることに起因した不具合を極力防止する

【解決手段】半導体基板1上に形成したシリコン酸化膜4にコンタクトプラグ5を形成し、シリコン窒化膜6、シリコン酸化膜7を積層し、芯材用膜を積層して芯材パターンに加工する。上面に非晶質シリコン膜を形成してスペーサ加工をしてマスクパターンを形成する。このとき、マスクパターンは、芯材パターンを挟んで対向するペア部の間隔に対して隣接部の間隔が小さくなるように形成される。芯材パターン除去の後、マスクパターンをマスクとしてシリコン酸化膜7、シリコン窒化膜6を加工して配線溝パターンを形成し、内部に導体膜8,9を埋め込み、埋め込み配線10a、10bを形成する。埋め込み配線10bは、上部で配線幅が広く形成されている。

(もっと読む)

不揮発性記憶装置及びその製造方法

【課題】集積度が高く、配線の密着性を向上した高信頼性の不揮発性記憶装置及びその製造方法を提供する。

【解決手段】第1の方向に延在する下側電極130と、下側電極130の上方に位置し、第1の方向と交差する第2の方向に延在する上側電極230と、下側電極130と上側電極230との間に設けられた金属酸化物や相変化材料を用いた記憶部300と、を備える。下側電極130及び上側電極230の少なくともいずれかは、順テーパの側壁を有する第1の電極110、210と、絶縁層150、250を介して第1の電極110と実質的に同じ平面内で隣接し、逆テーパの側壁を有する第2の電極120、220と、を有する。

(もっと読む)

半導体装置およびその製造方法

【課題】ブロック絶縁膜をゲート幅方向に連続するように構成しながら、シリコン基板の上面部のうちのワード線方向の端部とゲート電極との間の絶縁破壊の発生を抑制する。

【解決手段】素子分離領域2によって区画された活性領域3を有する半導体基板1と、活性領域3上に形成されたトンネル絶縁膜7と、トンネル絶縁膜7上に形成された電荷蓄積膜8と、電荷蓄積膜8上に形成されたブロック絶縁膜9と、ブロック絶縁膜9上に形成されたゲート電極10、11とを有してなるメモリセルトランジスタを備え、ブロック絶縁膜9をゲート幅方向に連続するように形成し、更に、電荷蓄積膜8のうちのゲート幅方向の端部8aの膜厚を厚くするように構成した。

(もっと読む)

半導体装置及びその製造方法

【課題】微細化に対応可能であり、不純物拡散領域上に形成したコンタクトプラグが近傍の導電材料とショートすることを防止する配線構造を有する半導体装置を提供する。

【解決手段】半導体基板内の不純物拡散領域22上に選択エピタキシャル成長法により、第1の層16aを形成する工程と、第1の層16a上に、選択エピタキシャル成長法により第2の層18を形成する工程と、第2の層18上に導電材料を充填することにより、コンタクトプラグ21を形成する工程と、を有する。

(もっと読む)

半導体記憶装置及びその製造方法

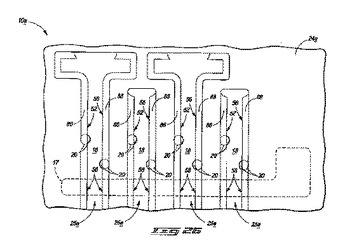

【課題】ビット線とシリコンピラーとを接続するための開口部の形成を容易化する。

【解決手段】半導体記憶装置10は、マトリクス状に配置され、それぞれの側壁にゲート絶縁膜12を介してゲート電極13が形成され、かつそれぞれの上端が記憶素子と電気的に接続される多数のシリコンピラー11と、各シリコンピラー11の間を互いに直交する方向に配線されたビット線BL及びワード線WLとを備える。ビット線BLは、両側のシリコンピラー11の下端と、1行おきに電気的に接続し、ワード線WLは、両側のシリコンピラー側壁にそれぞれ形成されたゲート電極13と、1列おきに電気的に接続する。

(もっと読む)

141 - 160 / 430

[ Back to top ]