Fターム[5F083PR10]の内容

半導体メモリ (164,393) | プロセス (23,970) | 側壁形成の利用で微細加工を行う (1,038) | 側壁の材料が絶縁膜(ゲート側壁は除く) (430)

Fターム[5F083PR10]に分類される特許

81 - 100 / 430

半導体装置の製造方法

【課題】ゲート電極上のキャップ膜が厚く、隣接するトランジスタ間の空間のアスペクト比が大きいトランジスタに、適切な濃度プロファイルを有するハロー領域を形成することのできる半導体装置の製造方法を提供する。

【解決手段】一実施の形態による半導体装置の製造方法は、基板上に第1および第2のゲート電極を形成する工程と、前記第1および第2のゲート電極下に第1および第2のハロー領域をそれぞれ形成する工程と、前記第1および第2の絶縁膜に底面および側面をそれぞれ覆われた第1および第2のキャップ膜を形成する工程と、を含む。前記第1のハロー領域は、第1の不純物を、前記第2の絶縁膜を貫通させて前記基板に打ち込むことにより形成される。前記第2のハロー領域は、第2の不純物を、前記第1の絶縁膜を貫通させて前記基板に打ち込むことにより形成される。

(もっと読む)

半導体デバイス及びその製造方法

【課題】ゲート電極と上部導電層とのショートを防止した安定動作可能な縦型MOSトランジスタを有する半導体デバイスを提供する。

【解決手段】縦型MOSトランジスタを構成する半導体ピラー5Aは、第1の幅を有する上部5Aaと第2の幅を有する下部5Abを有し、上部5Aa側面は第2の絶縁膜6aと第3の絶縁膜6bで覆われ、下部5Abは側面から第2の絶縁膜6aまでゲート絶縁膜である第1の絶縁膜11Aで覆われており、ゲート電極13Aが第2及び第3の絶縁膜6により上部導電層18と絶縁されている。

(もっと読む)

半導体素子及びその半導体素子のパターン形成方法

【課題】 フォトリソグラフィ工程の解像限界内で、具現可能なサイズのパターンを利用して超微細な幅及び間隔を持つ高密度パターンを形成できる配置構造を持つ半導体素子及びその半導体素子パターン形成方法を提供する。

【解決手段】 半導体素子は、コネクション領域に隣接するメモリセル領域を含む基板、メモリセル領域からコネクション領域まで第1方向に延びて配され、第1ライン幅及び第1ライン間隔を持つ複数の第1導電ライン、第1導電ラインそれぞれに連結されるように配され、第2ライン幅及び第2ライン間隔を持つ複数の第2導電ライン、コネクション領域に配され、第1導電ラインに電気的に連結された複数のパッド、を備える。半導体素子上のパターン形成方法は、微細ライン幅及び間隔を提供するために2段階のスペーサ形成工程を含むことができる。

(もっと読む)

ヒューズアレイと共に抵抗ランダムアクセスメモリを形成

【課題】抵抗ランダムアクセスメモリアレイが、ヒューズアレイと同一の基板上に形成する方法及びその集積回路を提供する。

【解決手段】ランダムアクセスメモリとヒューズアレイは同一の有効材料を使用する。例えば、ヒューズアレイとメモリアレイは、有効スイッチング材料としてカルコゲニド材料を使用する。主アレイはトレンチ分離82,84の直交する組のパターンを使用し、ヒューズアレイは平行なトレンチ分離82,84の一つの組のみを使用する。結果として、ヒューズアレイは、隣接するトレンチ分離82,84の間で連続して延伸する導電線を有する。いくつかの実施形態では、この連続する線はヒューズを通る導電性パスの抵抗を低減する。

(もっと読む)

半導体装置及びその製造方法

【課題】本発明は、ゲート電極と半導体基板との間のショートの発生を抑制した上で、厚さが厚く、かつ均一な厚さとされたシリサイド層を形成可能な半導体装置及びその製造方法を提供することを課題とする。

【解決手段】ゲート絶縁膜27を介して、ピラー26の側面26a,26bに設けられたゲート電極61,62と、ピラー26の上端26−1に形成されたシリサイド層38と、ゲート電極61,62を覆うと共に、ピラー26の側面を囲むように配置され、かつシリサイド層38の側面を露出する絶縁膜と、シリサイド層38の側面を覆うように設けられ、かつピラー26の上端26−1に含まれるシリコンをシリサイド化させる金属膜39と、シリサイド層38の下面38bと接触するように、ピラー26に形成された上部不純物拡散領域36と、シリサイド層38の上面38aに設けられたキャパシタ52と、を有する。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】メモリセルの素子領域の両端部に位置するラインの倒れを防止する。

【解決手段】本実施形態の半導体装置は、半導体基板と、前記半導体基板上に設けられたメモリセルの素子領域と、前記メモリセルの素子領域にラインアンドスペースパターン状に形成された活性領域および素子分離領域とを備える。前記活性領域のうちの前記メモリセルの素子領域の両端から1本目および2本目のラインは、2つ以上に分割された部分ラインで構成される。2本の部分ラインの分割側の端部は、連結パターンにより連結されて終端化されている。

(もっと読む)

不揮発性半導体メモリトランジスタ、および、不揮発性半導体メモリの製造方法

【課題】浮遊・制御ゲート間の容量を増大できる、島状半導体を用いた不揮発性半導体メモリトランジスタを提供する。

【解決手段】不揮発性半導体メモリトランジスタは、Si基板側からソース領域303、チャネル領域304及びドレイン領域302がこの順に形成された島状半導体301と、前記チャネル領域の外周を囲むように、トンネル絶縁膜305を間に介在させて配置された浮遊ゲート306と、浮遊ゲートの外周を囲むように、インターポリ絶縁膜307を間に介在させて配置された制御ゲート308aと、制御ゲートに接続され、所定方向に延びる制御ゲート線308と、を備える。浮遊ゲートは制御ゲートの下方及び上方領域、並びに、制御ゲート線の下方領域まで夫々延在され、浮遊ゲートと、制御ゲートの上面、下面及び内側面との間、及び、浮遊ゲートの、制御ゲート線の下方領域まで延在した部分と、制御ゲート線との間には、夫々インターポリ絶縁膜が介在配置される。

(もっと読む)

不揮発性記憶装置およびその製造方法

【課題】選択ゲート電極の側壁にメモリゲート電極を有する不揮発性記憶装置を微細化することができる技術を提供する。

【解決手段】選択ゲート電極CGをダミーパターンの側壁にサイドウォール形状で形成することで、メモリゲート電極MGが選択ゲート電極CGの両壁に形成されなくなり、フォトマスクの位置ずれを考慮する必要がなくなる。また、選択ゲート電極CGをサイドウォール状に形成することで、選択ゲート電極CGのゲート長が縮小しても、選択ゲート電極CGを構成する導電膜の膜厚により精度よく制御することを可能とする。

(もっと読む)

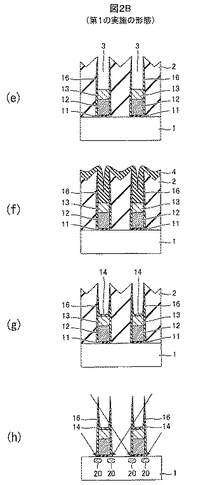

半導体装置及びその製造方法

【課題】本発明は、コンタクトプラグと埋め込み型のゲート電極との間に配置される絶縁膜の厚さを十分に確保可能な半導体装置及びその製造方法を提供することを課題とする。

【解決手段】ゲート絶縁膜16を介して、半導体基板11に形成された凹部14の凹部14の一部を埋め込むゲート電極41と、ゲート電極41の上端面41aを覆うように凹部14内を埋め込む絶縁膜18と、凹部14の一方の側面14a側に位置する半導体基板11の主面11aに形成された不純物拡散領域43と、不純物拡散領域43の上面43aを覆うシリコン層21と、半導体基板11の主面11aに形成された第1及び第2の層間絶縁膜23,31に内設され、シリコン層21の上面21aと接触し、かつ下端34bがシリコン層21の上面21aと絶縁膜18の上面18aとの間に配置されたコンタクトプラグ34と、を備える。

(もっと読む)

垂直型トランジスタと埋め込みビットラインとを有する半導体メモリ素子及びその製造方法

【課題】垂直型トランジスタのドレイン領域と埋め込みビットラインとの間に抵抗接点(ohmic contact)を形成しつつも、その製造工程が簡単な半導体メモリ素子及びその製造方法を提供すること。

【解決手段】基板に形成されたトレンチによって上部へ突出した形のアクティブ領域と、アクティブ領域の上部に配置される第1の不純物領域と、アクティブ領域の下部に配置される第2の不純物領域と、第1の不純物領域と第2の不純物領域との間のアクティブ領域の側面に沿って配置されるゲート絶縁膜と、ゲート絶縁膜上に配置されるゲート電極膜と、そして、トレンチの下部でライナー膜によって第2の不純物領域と離隔するように配置される金属膜と、金属膜上で前記第2の不純物領域と直接接触されるように配置されるポリシリコン膜とからなる埋め込みビットラインとを備えることを特徴とする。

(もっと読む)

半導体素子のパターン形成方法

【課題】互いに異なる幅のパターンを同一層で形成するにあたり、パターン間の間隔の均一度を改善することができる半導体素子のパターン形成方法を提供する。

【解決手段】セル領域及びセレクトトランジスタ領域を含む下部膜上に補助膜を形成する段階と、前記セレクトトランジスタ領域の前記補助膜上部に第1保護膜を形成する段階と、前記セレクトトランジスタ領域の前記第1保護膜上部には、前記第1保護膜の幅より狭い第1フォトレジストパターンが、前記セル領域の前記補助膜上部には前記第1フォトレジストパターンの幅より狭い第2フォトレジストパターンが形成され、前記第1及び第2フォトレジストパターン間の間隔を前記第2フォトレジストパターン間の間隔と同一に形成する段階と、を含む。

(もっと読む)

半導体装置の製造方法

【課題】側壁接合領域を有した半導体装置の製造方法を提供する。

【解決手段】基板をエッチングしてトレンチを形成するステップと、前記トレンチ底面の基板内に接合領域を形成するステップと、前記トレンチ底面を一定の深さエッチングして側壁接合領域を形成するステップと、前記側壁接合領域に接続するビットラインを形成するステップと、を含む半導体装置の製造方法。

(もっと読む)

半導体装置及びその製造方法

【課題】周期的に配列された複数本の配線と導電部材が設けられ、導電部材に配線よりも高い電圧を印加することができる半導体装置及びその製造方法を提供する。

【解決手段】実施形態に係る半導体装置は、一方向に延び、周期的に配列された複数本の第1配線と、前記複数本の第1配線からなる群の外側に配置され、前記一方向に延びる第2配線と、前記群と前記第2配線との間に設けられた第3配線と、前記第2配線から見て前記群の反対側に配置された複数の導電部材と、を備える。そして、前記第1配線と前記第3配線との最短距離、及び前記第3配線と前記第2配線との最短距離は、前記第1配線間の最短距離と等しく、前記第2配線と前記導電部材との最短距離は、前記第1配線間の最短距離よりも長い。

(もっと読む)

半導体素子及びその製造方法

【課題】半導体素子及びその製造方法を提供する。

【解決手段】基板上で第1方向に延在するラインパターンと、ラインパターンの端部から、第1方向と異なる方向に延在する分岐ラインパターンとをそれぞれ含む第1導電ライン;第2導電ライン;第3導電ラインとを含む半導体素子であり、中間に位置する導電ラインの分岐ラインパターンは、他の導電ラインの分岐ラインパターン間に位置し、長さもさらに短い。これにより、コンタクト・パッドが、導電ラインの分岐ラインパターンと一体に形成されうる。

(もっと読む)

半導体記憶装置

【課題】メモリセルから正確にデータを読み出すことができる半導体記憶装置を提供する。

【解決手段】半導体記憶装置は、第1ワード線1と、ビット線2と、抵抗変化材4とを備える。ビット線2は第1の面が第1ワード線1と対向するように第1ワード線1と交差する。抵抗変化材4は第1ワード線1とビット線2との各交差部に配置される。また半導体記憶装置は、第2ワード線3と、絶縁膜5とを備える。第2ワード線3はビット線2の第1の面とは反対側の第2の面と対向するようにビット線2と交差する。絶縁膜5は第2ワード線3とビット線2との各交差部に配置される。1つの第1ワード線1と1つの第2ワード線3とは、ビット線2を挟み込むように配置される。第2ワード線3、ビット線2、及び絶縁膜5は、各交差部において電界効果トランジスタを構成する。電界効果トランジスタと抵抗変化材4とにより1つのメモリセルが構成される。

(もっと読む)

半導体装置の製造方法

【課題】ホールパターンの寸法のばらつきを抑え、ホールパターンの未開口の発生を抑制する半導体装置の製造方法を提供する。

【解決手段】一つの実施形態によれば、半導体装置の製造方法は、第1と第2のレジストパターン形成工程を含む。第1のレジストパターン形成工程では、コンタクトホール形成領域に、開口パターン111を有する第1のレジストパターン11を形成する。第2のレジストパターン形成工程では、コンタクトホール形成領域の第1の領域R1に開口パターン112を有し、第2の領域R2に第3の開口パターン112を有する第2のレジストパターン12を形成する。第2と第3の開口パターン112は、1本おきの活性領域3上に配列した形状を有するが、互いに異なる活性領域3上に形成される。そして、先に行う第1または第2のレジストパターン形成工程では、後のリソグラフィ処理で耐性を有するレジストの不溶化処理が行われる。

(もっと読む)

シングルゲートフィンFET及びその製造方法

【課題】新規なFinFET構造及びその製造方法を提供する。

【解決手段】シングルゲートフィンFET構造100は、2つの拡大された頭部、及び当該拡大された頭部と下層の超薄型ボディとを連結する2つの徐々に細くなる首部を有するアクティブフィン構造を含む。2つのソース/ドレイン領域102,104が、2つの拡大された頭部にそれぞれドープされる。絶縁領域26が、2つのソース/ドレイン領域の間に挿入される。溝分離構造24が、音叉形状のフィン構造の一方の側に配置される。片面サイドウォールゲート電極12bが、アクティブフィン構造における、溝分離構造とは反対側の垂直なサイドウォールに配置される。

(もっと読む)

半導体装置の製造方法

【課題】溝内の一部のみを覆うマスクパターンを、フォトレジスト膜を用いて形成する必要のない半導体装置の製造方法を提供する。

【解決手段】半導体基板1に、第1溝7を形成する工程と、第1溝7に第1絶縁膜8を形成する工程と、上面が第1絶縁膜の上端よりも下方になるように第1溝7内に第1導電膜9を充填する工程と、第1溝7の側面にカーボン膜10を形成する工程と、第1溝7内を第2絶縁膜11で充填する工程と、第1溝7内の側面の一方を覆うカーボン膜10を除去し、第1絶縁膜8の一部を露出させる工程と、第2絶縁膜11と露出された第1絶縁膜8を除去し、半導体基板1の一部を露出する工程と、を有することを特徴とする。

(もっと読む)

半導体装置及びその製造方法

【課題】本発明ではフォトリソグラフィー技術解像限界付近のパターン形成を安定して形成すると共に、コンタクトプラグなどの構造物における目合わせずれや接触面積の縮小による接触電気抵抗の増大や接続不良を解決する。

【解決手段】半導体基板上に形成された絶縁材料層100に、第1の方向に延在し、底部の幅W1より上部の幅W2が広い第1の溝101を形成する工程と、第1の溝101内に、溝の上端より低い位置まで埋め込み層102を形成する工程と、埋め込み層102上に露出している第1の溝101の側壁を覆うサイドウォール103を形成する工程と、サイドウォール103をマスクとして埋め込み層102をエッチングして第1の方向に分離する工程と、

を含むことを特徴とする。

(もっと読む)

半導体装置の製造方法

【課題】サイドウォールスペーサを利用してリソグラフィー解像限界未満のパターンと任意の寸法のパターンとが混在するパターンを形成する。

【解決手段】アモルファスカーボン膜3及びシリコン酸窒化膜4からなる被エッチング部材上に塗布膜5をスピン塗布法により成膜し、塗布膜5をパターニングすることによってサイドウォールコアを形成し、サイドウォールコアの少なくとも側面を覆うシリコン酸化膜7を成膜し、シリコン酸化膜7上に有機反射防止膜8をスピン塗布法により成膜する。次いで、有機反射防止膜8をエッチングすることによって、シリコン酸化膜7の凹部7aを覆う埋込マスクを形成し、シリコン酸化膜7をエッチングすることにより、サイドウォールコアまたは埋込マスクと重ならない被エッチング部材を露出させ、被エッチング部材をエッチングすることでフォトリソグラフィー解像限界未満のパターンを得る。

(もっと読む)

81 - 100 / 430

[ Back to top ]