Fターム[5F083PR10]の内容

半導体メモリ (164,393) | プロセス (23,970) | 側壁形成の利用で微細加工を行う (1,038) | 側壁の材料が絶縁膜(ゲート側壁は除く) (430)

Fターム[5F083PR10]に分類される特許

121 - 140 / 430

半導体装置及びその製造方法

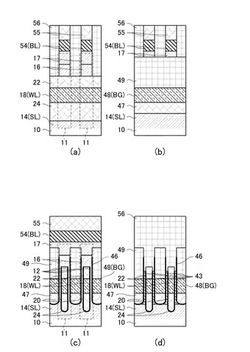

【課題】3次元的に形成したトランジスタやサイリスタのリーク電流を低減する半導体装置及びその製造方法を提供する。

【解決手段】半導体装置は、基板10の主面に対してほぼ垂直に形成されたシリコンピラー12と、シリコンピラー12の下部及び上部にそれぞれ設けられた第1及び第2の不純物拡散層14,16と、シリコンピラー12を水平方向に貫いて設けられたゲート電極18と、ゲート電極18とシリコンピラー12との間に設けられたゲート絶縁膜20と、シリコンピラー12に隣接して設けられたバックゲート電極48と、バックゲート電極48とシリコンピラー12との間に設けられたバックゲート絶縁膜46とを備える。

(もっと読む)

半導体装置

【課題】SRAM回路の動作速度を向上させる。

【解決手段】駆動MISFETと転送MISFETとそれらの上部に形成された縦型MISFETとでメモリセルを構成したSRAMにおいて、周辺回路を構成するMISFET間の電気的接続を、メモリセルの縦型MISFET(SV1、SV2)よりも下部に形成されるプラグ28および中間導電層46、47で行うとともに、縦型MISFET(SV1、SV2)よりも上部に形成されるプラグ、第1および第2金属配線層を用いて行うことにより、配線の自由度を向上でき、高集積化できる。また、MISFET間の接続抵抗を低減でき、回路の動作スピードを向上できる。

(もっと読む)

半導体装置及びその製造方法

【課題】3次元的に形成したDRAM用のトランジスタやサイリスタのリーク電流を低減する半導体装置及びその製造方法を提供する。

【解決手段】基板10の主面に対してほぼ垂直に形成されたシリコンピラー12と、シリコンピラー12の下部及び上部にそれぞれ設けられた第1及び第2の不純物拡散層14,16と、シリコンピラー12を水平方向に貫いて設けられたゲート電極18と、ゲート電極18とシリコンピラー12との間に設けられたゲート絶縁膜20とを備える。これによれば、シリコンピラー12の体積が小さくなるので、シリコンピラー12内に形成されるトランジスタやサイリスタのリーク電流を低減できる。

(もっと読む)

半導体メモリ素子及びその製造方法

【課題】電気的特性が向上した半導体メモリ素子及びその製造方法を提供する。

【解決手段】本発明の半導体メモリ素子は第1電極及び第2電極を含む。第1元素を含む可変抵抗物質パターンが第1及び第2電極の間に提供される。第1スペーサは可変抵抗物質パターンに隣接して提供される。

(もっと読む)

不揮発性メモリセル、これを有するメモリアレイ、並びに、セル及びアレイの操作方法

【課題】自己収束消去動作を容易にすると共に保持状態の期間におけるメモリデバイスの電荷蓄積層内での電荷保持能力を保持してもいるトンネル誘電体構造を有する不揮発性メモリデバイスの提供。

【解決手段】半導体基板101であって、該基板の表面より下に配置され且つチャネル領域106によって分離されたソース領域102及びドレイン領域104を備えた半導体基板と、前記チャネル領域より上に配置されたトンネル誘電体構造102であって、低いホールトンネリング障壁高さを有する少なくとも1つの層を備えたトンネル誘電体構造と、前記トンネル誘電体構造より上に配置された電荷蓄積層130と、前記電荷蓄積層より上に配置された絶縁層140と、前記絶縁層より上に配置されたゲート電極150とを有するメモリセル、該メモリセルのアレイ及び操作方法と共に開示する。

(もっと読む)

半導体装置の製造方法

【課題】パターン不良を抑制することが可能な半導体装置の製造方法を提供する。

【解決手段】被加工膜上に、ラインアンドスペース部と前記ラインアンドスペース部の外側に形成された第一のパターンとを有する第二のパターンを形成し、側壁パターンを前記第二のパターンの側壁に形成し、前記第一のパターンの側壁のうち、前記ラインアンドスペース部と反対側の側壁に形成された側壁パターンを除去し、前記第一のパターンの側壁のうち、前記ラインアンドスペース部と対向する側の側壁に形成された側壁パターンに基づき、回路パターンを形成する。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】メモリ領域の高密度化を図ることができる半導体装置及び半導体装置の製造方法を提供する。

【解決手段】半導体装置は、半導体基板10上にメモリセル領域と周辺回路領域とを有する。まず、メモリセル領域の半導体基板10に溝を形成し、メモリセル領域の溝内に酸化膜を形成し、メモリセル領域の溝内における底面の酸化膜のみを除去し、メモリセル領域の溝をシリコンで埋めることで、リソグラフィ限界以下の幅の酸化膜からなる素子分離20を形成する。

(もっと読む)

半導体装置およびその製造方法

【課題】3Dピラートランジスタにおいて、ゲートコンタクトとシリコン基板との間のショートを抑制した半導体装置及びその製造方法を得るという課題があった。

【解決手段】半導体からなる基板1と、一面1aから突出され、前記半導体からなる第1の突出部2と、一面1aに設けられた溝部1cに充填された第1の絶縁体3と、第1の突出部2に隣接して一面3aから突出され、第1の絶縁体3からなる第2の突出部4と、第1の突出部2の側面を覆うゲート絶縁膜5と、ゲート絶縁膜5を覆うゲート電極6と、第1の突出部2に設けられた上部拡散層13と、下部拡散層14と、第2の突出部4の側面を覆うとともにゲート電極6に接続された連結電極60と、第1の突出部2及び第2の突出部4を覆う層間絶縁膜と、前記層間絶縁膜を貫通して連結電極60に接するゲートコンタクト10と、を有する半導体装置及びその製造方法を用いることにより、上記課題を解決できる。

(もっと読む)

三次元メモリアレイ積層構造体

【課題】 改善された三次元メモリ(例えば、RRAM)アーキテクチャを提供すること。

【解決手段】 メモリデバイスが、平面基板と、平面基板の上方の複数の水平な導電性平面と、複数の水平な導電性平面と交互に配置される複数の水平な絶縁層とを備える。複数の導電性平面および絶縁層と直角である垂直な導電性列のアレイが、複数の導電性平面および絶縁層における開口部を通過する。メモリデバイスは、複数のプログラム可能なメモリ素子を備え、それぞれのメモリ素子が、水平な導電性平面の1つをそれぞれの垂直な導電性列に連結する。

(もっと読む)

半導体装置の製造方法

【課題】トレンチ内に形成されたビット線の底面からのリーク電流を低減する。また、トレンチのアスペクト比を大きく増加させることなく、その後の工程でトレンチ内の空間に安定して成膜して、高アスペクト比による加工性の低下といった問題が生じない半導体装置を提供する。

【解決手段】半導体基板内にトレンチを形成する。このトレンチ内壁の底面上に第一の絶縁膜を形成する。また、トレンチ内壁の側面上に熱酸化により第一の絶縁膜よりも膜厚が薄い第二の絶縁膜を形成する。トレンチ内の第一の絶縁膜上に、ビット線を形成する。

(もっと読む)

半導体装置の製造方法

【課題】RC型トランジスタのチャネル領域の高さを所望の範囲に調整するとともに、前記チャネル領域に近接して残存する薄皮状のバリ部を完全に除去して、半導体装置を製造するという課題があった。

【解決手段】半導体基板1の一面に、溝部と、溝部に囲まれ、側壁面の少なくとも一部が傾斜面である凸部39とを形成してから、溝部を埋める素子分離用絶縁膜を形成する第1工程と、素子分離用絶縁膜をマスクの一部にして半導体基板1の一面をドライエッチングして凸部39内に凹部27を設けるとともに、凹部27と素子分離用絶縁膜との間にチャネル領域4となる薄肉部41を形成する第2工程と、ウェットエッチングにより、薄肉部41の高さを調整する第3工程と、を有する半導体装置の製造方法を用いることにより、上記課題を解決できる。

(もっと読む)

半導体装置とその製造方法

【課題】ビット線の上面にハードマスク膜を形成し、ビット線の側壁に窒化膜をエッチバックして形成したサイドウォールを設けるSAC(セルフアラインコンタクト)プロセスを用いることなくビット線と容量コンタクトとの間の短絡を防止する。

【解 決手段】SAC構造を採用していない半導体装置に対して、ビット線6が形成されている場所以外のビットコンタクト層間膜13をエッチング処理により除去した後に、 ダイレクト窒化膜19をビット線6の上面および側面の全面にビット線6を覆うようにして形成する。ビット線6上の上面の窒化膜の膜厚を側面とほぼ同一にで きるため、ビット線6自体の高さが低くなり、微細化を図ることができる。また、エッチバックを必要とせずに、ビット線6の側壁に窒化膜を形成するため、 SAC構造に比べて、ビット線6の側壁に一定の膜厚を有する窒化膜を容易に形成できる。

(もっと読む)

半導体装置の製造方法、半導体装置及びデータ処理システム

【課題】第1配線の比抵抗が小さく、シリサイド異常成長が抑制された半導体装置の製造方法の提供。

【解決手段】第1溝を半導体基板1に設けた後、第1溝内に、シリコンとの間でシリサイドを形成しない材料からなる導体層6と半導体層10とを含む第1配線11を形成して、半導体層と半導体基板とを直接に接触させる工程と、半導体層に含まれるドーパントを半導体基板に拡散させて第1不純物拡散領域13を形成する工程と、第1溝と交差する方向に延在する第2溝を半導体基板に設けることで、第1不純物拡散領域を包含して半導体基板に立設されたピラー部1bを形成する工程と、第2溝の側壁面にゲート絶縁膜16を形成してから、ゲート絶縁膜を介してピラー部に対向する第2配線17を第2溝内に形成する工程と、ピラー部の先端部に、第2不純物拡散領域19を形成する工程と、を具備してなる半導体装置の製造方法を採用する。

(もっと読む)

半導体装置の製造方法

【課題】微細なパターンを精度良く形成することのできる半導体装置の製造方法を提供する。

【解決手段】本発明の一態様に係る半導体装置の製造方法は、被加工体1上にCを含む材料からなる芯材2を選択的に形成する工程と、芯材2の上面および側面を覆うように、酸素を含まない材料からなる保護膜3を形成する工程と、保護膜3を介して芯材2と被加工体1を覆うように酸化膜4を形成する工程と、芯材2の側方に少なくとも酸化膜4からなる側壁5を加工形成する工程と、少なくとも芯材2を除去した後、側壁5をマスクとして用いて被加工体1をエッチングし、側壁5のパターンを転写する工程と、を含む。

(もっと読む)

半導体装置及びその製造方法

【課題】フィンの下部に適切に不純物が導入された半導体装置及びその製造方法を提供する。

【解決手段】半導体装置としてのFinFET1は、基体としての半導体基板10と、半導体基板10上に形成された複数のフィン20とを有し、複数のフィン20は、第1の間隔と第1の間隔よりも間隔が狭い第2の間隔とを繰り返して形成され、第1の間隔を形成する側に面した第1の側面221の下部の不純物濃度が、第2の間隔を形成する側に面した第2の側面222の下部の不純物濃度よりも高い半導体領域を有する。

(もっと読む)

半導体装置のパターン構造物及び半導体装置のパターン構造物の形成方法

【課題】半導体装置のパターン構造物及び半導体装置のパターン構造物の形成方法を提供すること。

【解決手段】半導体装置のパターン構造物は、延長ラインと延長ラインの端部に連結されるパッドとを具備する。パッドは、延長ラインの幅より広い幅を有することができる。パッドは、パッドの側部から延長する突出部を含むことができる。パターン構造物は、単純化された工程を通じて製造されることができ、微細パターンとパッドを含む多様な半導体装置に適用することができる。

(もっと読む)

半導体装置及びその製造方法

【課題】深さの異なる複数のコンタクトホールの底部径のばらつきを抑制する半導体装置及びその製造方法を提供する。

【解決手段】本発明の半導体装置は、複数の導電層WL1〜WL4が階段状に加工された階段構造部を有する積層体と、階段構造部を覆って設けられた層間絶縁層43と、層間絶縁層43を貫通し、それぞれが対応する各段の導電層WL1〜WL4に達して形成された複数のコンタクトホール61〜64の内部に設けられたコンタクト電極60とを備え、複数のコンタクトホール61〜64の底部の孔径は略同じであり、下段側の導電層に達するコンタクトホールは、上段側の導電層に達するコンタクトホールよりも深く、上端部の孔径が大きい。

(もっと読む)

配線パターン形成方法および半導体装置の製造方法、半導体装置、データ処理システム

【課題】2回のリソグラフィ工程によるSADP法(Self Align Double Patterning)を用いて、第1配線パターン形成領域には解像限界未満のパターンを含む第1配線パターンを形成し、第2配線パターン形成領域には解像限界以上の通常パターンからなる第2配線パターンを簡便に形成する方法を提供する。

【解決手段】解像限界未満の寸法を有する複数の配線を含む第1配線パターンを、第1リソグラフィ工程と第1リソグラフィ工程の後に実施される第2リソグラフィ工程を用いて形成し、第1のリソグラフィ工程で形成されたパターンに対してのみサイドウォールの形成および除去処理を行い、その後、解像限界以上のパターンを生成する第2リソグラフィ工程を実施する。第2のリソグラフィ工程で形成される解像限界以上の通常パターンに対しては、単純なリソグラフィ工程とすることが可能となる。

(もっと読む)

不揮発性半導体記憶装置、不揮発性半導体記憶装置の製造方法

【課題】記憶領域の増大を抑制しつつ、より多くの情報を記憶できる不揮発性半導体記憶素子を提供する。

【解決手段】第1ソース/ドレイン拡散層(11)と、第2ソース/ドレイン拡散層(12)と、チャネル領域の上に構成され、電気的に絶縁される二つの電荷蓄積層(21)と、電気的に絶縁された二つのゲート電極(13、14)とを具備する不揮発性半導体記憶装置を構成する。第1の電荷蓄積層(2−1、2−2)は、第1領域(2−1)と第2領域(2−2)とを有し、第2の電荷蓄積層(2−3、2−4)は、第3領域(2−3)と第4領域(2−4)とを有するものとする。そして、第1のゲート電極(13)は、第1領域(2−1)と第3領域(2−3)とに跨り、第2のゲート電極(14)は、第2領域(2−2)と第4領域(2−4)とに跨る。

(もっと読む)

抵抗変化メモリ

【課題】可変抵抗素子の抵抗値ばらつきに起因する誤動作を抑制する抵抗変化メモリを提供する。

【解決手段】抵抗変化メモリは、第1の電極14、抵抗変化膜15、及び第2の電極16が積層された積層構造からなり、かつ記憶データに基づいて低抵抗状態又は高抵抗状態を取り得る可変抵抗素子17と、可変抵抗素子17の側面に設けられた絶縁膜19と、絶縁膜19の側面に設けられた導電膜からなり、かつ可変抵抗素子17に並列接続された固定抵抗素子20とを含む。

(もっと読む)

121 - 140 / 430

[ Back to top ]