Fターム[5F083PR10]の内容

半導体メモリ (164,393) | プロセス (23,970) | 側壁形成の利用で微細加工を行う (1,038) | 側壁の材料が絶縁膜(ゲート側壁は除く) (430)

Fターム[5F083PR10]に分類される特許

161 - 180 / 430

半導体記憶装置、及びその製造方法

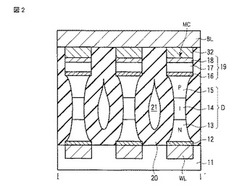

【課題】ダイオードの順方向特性を劣化させることなく逆方向特性を改善させる。

【解決手段】半導体記憶装置は、可変抵抗素子19及びダイオードDを有し、かつピラー状の第1及び第2のメモリセルと、第1のメモリセル及び第2のメモリセル間に設けられ、かつボイド21を有する絶縁層20とを含む。さらに、ダイオードDの中央部は、その上部及び下部よりも幅が狭くなっている。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】電極材料のエッチバックが不均一であっても、縦型MOSトランジスタのゲート長のばらつきを小さくして、トランジスタ特性のばらつきを小さくした半導体装置および半導体装置の製造方法を得るという課題があった。

【解決手段】半導体基板10と、半導体基板10から突出され、先端側に大径部31が設けられ、大径部31の基端側に小径部33が設けられ、かつ、大径部31の周端面31cよりも小径部33の周端面1cが後退されて段部1dが設けられたピラー部1と、ピラー部1の周端面1cに備えられた第1の絶縁膜2と、第1の絶縁膜2を介して少なくとも一部が段部1dに埋められた電極部3と、ピラー部1の基端側および先端側に設けられた不純物拡散領域15、16と、を具備し、電極部3の段部1dに埋められた部分の高さが、ピラー部1の全周に渡って均一の高さとされている半導体装置を用いることにより、上記課題を解決できる。

(もっと読む)

クロスポイント型半導体メモリ装置及びその製造方法

【課題】1つのメモリセルの大きさが4F2を下回る大きさである構成、構造を有するクロスポイント型半導体メモリ装置を提供する。

【解決手段】クロスポイント型半導体メモリ装置は、第1の方向に延びる複数の第1の配線41A、41B;第1の配線とは垂直方向に異なる所に位置し、第1の方向とは異なる第2の方向に延びる複数の第2の配線42;及び、第1の配線と第2の配線とが重複する領域に設けられたメモリ部43から構成され、奇数番目の第1の配線41Aと、偶数番目の第1の配線41Bとは、上下方向に異なる層間絶縁層21,22上に配置されている。

(もっと読む)

半導体装置の製造方法およびフォトマスク

【課題】極微細なパターンを有するSRAM領域のフィンと周辺回路領域の活性領域とを低コストかつ正確なデザインで形成することのできる半導体装置の製造方法、およびその製造方法に用いられるフォトマスクを提供する。

【解決手段】本発明の一態様に係る半導体装置の製造方法は、第1および第2の領域を有する半導体基板上にマスク材を形成する工程と、前記第1の領域の前記マスク材上に芯材をパターン形成する工程と、前記芯材の両側面に側壁マスクを形成した後、前記芯材を除去する工程と、前記芯材を除去した後、前記第1の領域の前記マスク材に前記側壁マスクのパターンを転写する工程と、前記第1の領域の前記側壁マスクのパターンを転写された前記マスク材のトリミングと、前記第2の領域の前記マスク材への所定のパターンの形成とを同時に行う工程と、を含む。

(もっと読む)

半導体装置及びその製造方法

【課題】幅の狭い溝状領域への層間絶縁膜の形成にポリシラザンを用いた場合のシリコン酸化膜への改質が良好に行われる半導体装置及びその製造方法を提供する。

【解決手段】上面及び側面をキャップ絶縁膜107及びサイドウォール絶縁膜108で覆われた複数のビット線106間に形成された溝状領域109と、N(窒素)よりもO(酸素)を多く含み溝状領域109の内表面を連続的に覆うSiON膜10と、SiON膜10を介して溝状領域109内に埋め込まれ、ポリシラザンを改質することによって形成されたシリコン酸化膜11とを備える。

(もっと読む)

可変抵抗メモリー素子及びその製造方法

【課題】可変抵抗メモリー素子及びその製造方法を提供する。

【解決手段】本発明の一実施形態による可変抵抗メモリー素子は、少なくとも1つの下部電極と、少なくとも1つの下部電極を露出するトレンチを含む第1絶縁膜と、前記トレンチの対向する側壁の上に各々位置する第1及び第2部分を含む可変抵抗物質膜と、を含み、前記可変抵抗物質膜の第1及び第2部分は、前記少なくとも1つの下部電極と電気的に連結される。前記素子は、前記トレンチの内の可変抵抗物質膜を覆う保護膜、及び前記トレンチの内に位置し、前記トレンチの内の保護膜を覆う第2絶縁膜をさらに含む。

(もっと読む)

メモリデバイス及びメモリデバイスの形成方法

【課題】プログラマブルMOSFET(105)とロジックMOSFET(110)とを含むメモリデバイスを同一チップ上に形成する。

【解決手段】半導体基板を被う層状ゲート積層体の成形から始まり、層状ゲート積層体の高kゲート電極層上で停止するよう金属ゲート電極層にパターンを形成して、半導体基板上に第1、第2ゲート金属ゲート電極(16、21)を形成するメモリデバイスの製法が提供される。次のプロセスで、高kゲート誘電体層の一部を被う少なくとも1つのスペーサ(55)を第1ゲート電極(16)に形成する。高kゲート誘電体層の露出された残存部分をエッチングし、第1金属ゲート電極のサイドウォールを越えて延びる部分を有する第1高kゲート誘電体(17)及び第2金属ゲート電極(21)のサイドウォールに整合されたエッジを有する第2高kゲート誘電体(22)を形成する。

(もっと読む)

半導体装置及びその製造方法

【課題】柱状構造体の形成の際のリソグラフィの合わせずれの許容度を拡大し、デバイス特性の劣化を抑制する半導体装置及びその製造方法を提供する。

【解決手段】第1層と、前記第1層の主面の上に設けられた第2層と、前記主面を貫通し、前記第1層と前記第2層とに延在する導電性の柱状構造体と、前記主面の前記第2層の側において前記柱状構造体の側壁に付設された側部と、を備えたことを特徴とする半導体装置を提供する。

(もっと読む)

半導体記憶装置

【課題】データの書込み速度を高く維持しつつ、非選択セルのデータの劣化を抑制することができる半導体記憶装置を提供する。

【解決手段】半導体記憶装置は、半導体層30と、半導体層内に設けられたソース層Sおよびドレイン層Dと、ソース層とドレイン層との間の半導体層に設けられ、論理データを記憶するために電荷を蓄積し、あるいは、電荷を放出する電気的に浮遊状態のボディ領域Bと、ボディ領域上に設けられたゲート絶縁膜50と、或る1つのボディ領域上にゲート絶縁膜を介して設けられ、ソース層、ドレイン層およびボディ領域を含むメモリセルのチャネル長方向に互いに分離された第1のゲート電極G1および第2のゲート電極G2とを備えている。

(もっと読む)

半導体素子及び半導体素子のパターン形成方法

【課題】多様な幅を有するパターンを同時に形成しつつ、一部領域ではダブルパターニング技術によりパターン密度を倍加させる半導体素子のパターン形成工程及び該工程を容易に適用可能な構造の半導体素子を提供する。

【解決手段】半導体素子は、第1方向に相互平行に延びている複数のラインパターンを含む。複数のラインパターンのうちから選択される複数の第1ラインパターンは、第2方向に沿って交互に選択されて両側で各々隣接している2つのラインパターンの両端部のうち、素子領域の第1端部にさらに近い各端部に比べて、第1端部からさらに遠く位置する第1端部を有する。複数のラインパターンのうちから選択される複数の第2ラインパターンは、第2方向に沿って交互に選択され、両側で各々隣接している2つのラインパターンの両端部のうち、第1端部にさらに近い各端部より、第1端部からさらに近く位置する第2端部を有する。

(もっと読む)

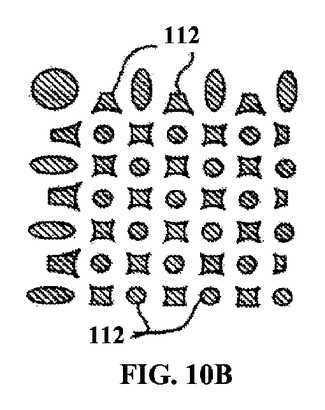

柱状構造のためのレジストフィーチャおよび除去可能スペーサピッチを倍増するパターニング法

半導体装置を製作する方法が、基板上に少なくとも1つの層を形成することと、少なくとも1つの層の上に画像形成性材料よりなる少なくとも2つの離間されたフィーチャを形成することと、少なくとも2つのフィーチャ上に側壁スペーサを形成することと、第1のフィーチャ上の第1の側壁スペーサと第2のフィーチャ上の第2の側壁スペーサとの間の空間をフィラーフィーチャで充填することと、を含む。この方法はまた、第1のフィーチャ、フィラーフィーチャおよび第2のフィーチャを互いに離間した状態で残すように、側壁スペーサを選択的に除去することと、第1のフィーチャ、フィラーフィーチャおよび第2のフィーチャをマスクとして使用して少なくとも1つの層をエッチングすることと、を含む。  (もっと読む)

(もっと読む)

可変抵抗素子及びその製造方法

【課題】 所望の電気的特性を安定的に示す可変抵抗素子を提供し、またこのような可変抵抗素子の製造方法を提供する。

【解決手段】 可変抵抗素子1は、サイドウォール絶縁膜16と第1絶縁膜13の境界において、半導体基板11の基板面と直交する方向に第1バリア膜15(15a)が成膜されている。また、サイドウォール絶縁膜16の底面にも第1バリア膜15(15b)が成膜されている。これらのバリア膜は、水素等の還元種、酸素等の酸化種、またはこれら双方の拡散を防止する拡散防止性を備えた材料で構成されている。なお、開口部30の底面に第1電極17aが形成され、絶縁膜13の上面及びサイドウォール絶縁膜16の絶縁膜13側の一部上面に第2電極17bが形成され、これら両電極の上面にまたがるように可変抵抗体18が形成されている。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】エッチングストッパ膜を有し、配線間容量の増大を抑制可能な半導体装置及び半導体装置の製造方法を提供する。

【解決手段】半導体基板11と、半導体基板11の表面上部に配設された層間絶縁膜29と、層間絶縁膜29に埋め込まれ、半導体基板11に対向する上面が層間絶縁膜29の上面と面一に配設され、互いに離間して配置された複数のビアプラグ31と、層間絶縁膜29及びビアプラグ31の表面上部に配設された層間絶縁膜39と、層間絶縁膜39によって分離され、ビアプラグ31と接続され、ビアプラグ31に対向する上面が層間絶縁膜39の上面と面一に配設され、層間絶縁膜39を挟んで相対向する側面に、層間絶縁膜29の側から順に、層間絶縁膜29とはエッチング性が異なり且つ層間絶縁膜39より比誘電率の高い側壁絶縁膜35、及び側壁絶縁膜35とはエッチング性が異なる側壁絶縁膜37を有する複数の第2配線33とを備える。

(もっと読む)

半導体装置の製造方法

【課題】半導体装置の絶縁膜の上に形成される金属配線または金属電極の接着力を向上させる。

【解決手段】窒化タングステン6bをタングステン6cの側面にまで設けて、タングステン6cと窒化タングステン6bとが接触している面積を増やす。ゲート絶縁膜2上に、ゲート絶縁膜2との接着力が強いポリシリコンサイドウォール5を配置する。タングステン6cの側面にある窒化タングステン6bにはポリシリコンサイドウォール5を密着させる。

(もっと読む)

ダイオードの形成方法

実施形態は、ダイオードを形成する方法を含む。積層が第1の導電性物質上に形成される。積層は、犠牲物質、少なくとも一の誘電物質、及び第2の誘電物質をこの順で含む。スペーサを積層と相対する側壁に沿って形成してもよい。犠牲物質の全てを除去して、第1の導電性物質と少なくとも一の誘電物質との間にギャップを残してもよい。ダイオードの形成についての実施形態によっては、層を第1の導電性物質上に形成してもよく、層は、犠牲物質内に拡散された支持物を含んでよい。層上には少なくとも一の誘電物質を形成してもよく、少なくとも一の誘電物質上に第2の導電性物質を形成してもよい。その後、犠牲物質の全てが除去される。  (もっと読む)

(もっと読む)

オープン・ボリュームを含む選択デバイス、このデバイスを含むメモリ・デバイスおよびシステム、ならびにこのデバイスの形成方法

誘電率の低い高バンドギャップ材料として機能するオープン・ボリュームを含む選択デバイスを開示する。このオープン・ボリュームは、より非線形で非対称なI-V曲線および向上した整流化挙動を選択デバイス中で実現することができる。この選択デバイスは、たとえば金属-絶縁体-絶縁体-金属(MIIM)デバイスを含むことがある。選択デバイスおよびこうした選択デバイスを含むメモリ・システムを形成するのに様々な方法を使用することができる。メモリ・デバイスおよび電子システムが、こうした選択デバイスを含む。 (もっと読む)

不揮発性半導体記憶装置及びその製造方法

【課題】ゲート電極に金属を用いた場合におけるメモリセルトランジスタ特性の劣化を防止する。

【解決手段】半導体基板上に形成された複数のメモリセルトランジスタを有する不揮発性半導体記憶装置であって、メモリセルトランジスタは、基板11上に順に形成されたトンネル絶縁膜12,電荷蓄積層13,ブロック絶縁膜15,及びゲート電極16を有し、ゲート電極16は、ブロック絶縁膜15に接する第1ゲート電極層16−1と、第1ゲート電極層16−1上に設けられた第1ゲート電極層16−1とは異なる材料からなる第2ゲート電極層16−2との、少なくとも2層が積層された構造であり、第1ゲート電極層16−1の上面及び下面のゲート長方向の長さは、第2ゲート電極層16−2の下面のゲート長方向の長さよりも長い。

(もっと読む)

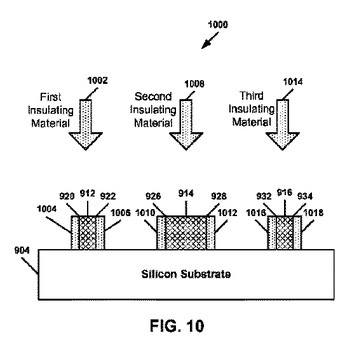

フィン電界効果トランジスタ(フィンFET)デバイスの製造方法

フィン電界効果トランジスタ(フィンFET)を用いた半導体の製造方法が開示される。特定の実施形態の方法は、第一の幅によって離隔された第一の側壁及び第二の側壁を有する第一のダミー構造体をシリコン基板上に堆積させるステップを含む。また、本方法は、第一のダミー構造体を堆積させるのと同時に第二のダミー構造体をシリコン基板上に堆積させるステップも含む。第二のダミー構造体は、第二の幅によって離隔された第三の側壁及び第四の側壁を有する。第二の幅は第一の幅よりも実質的に大きい。第一のダミー構造体を用いて略第一の幅によって離隔された第一の対のフィンを形成する。第二のダミー構造体を用いて略第二の幅によって離隔された第二の対のフィンを形成する。  (もっと読む)

(もっと読む)

半導体装置およびその製造方法

【課題】ビアホール下方でのスペーサ膜の閉塞を回避するとともに、ビアプラグの上方で隣接する配線層との間の余裕距離を確保することができる半導体装置を提供する。

【解決手段】シリコン基板1上に設けられた上面から下面まで貫通するコンタクトプラグ32を有する第1の層間絶縁膜30と、第1の層間絶縁膜30上に形成され、コンタクトプラグ32の形成位置に対応する位置の上面から下面まで貫通するビアホール41を有する第2の層間絶縁膜40と、ビアホール41内にコンタクトプラグ32と電気的に接触するように導電性材料が埋め込まれたビアプラグ43と、を備え、ビアホール41を形成する側壁は、第2の層間絶縁膜40の上面から下面に向かって、基板面に平行な方向の断面積が徐々に減少する順テーパ状を有し、ビアホールの上端部から所定の深さまでの側壁に、第2の層間絶縁膜40とは異なる絶縁性材料からなるスペーサ膜42が埋め込まれている。

(もっと読む)

半導体素子の製造方法および半導体素子

【課題】 半導体素子の微細パターン製造方法を提供する。

【解決手段】フィーチャー層310の第1領域Aには第1マスク構造物を形成し、第2領域Bには第2マスク構造物を形成する。各々デュアルマスク層とエッチングマスク層とを含むように第1マスク構造物及び第2マスク構造物を形成する。第1マスク構造物及び第2マスク構造物のエッチングマスクパターンを等方性エッチングし、第1マスク構造物からエッチングマスクパターンを除去する。第1マスク構造物及び第2マスク構造物の両側壁にスペーサ350A、350Bを形成する。第2マスク構造物上にあるエッチングマスクパターンをマスクとして第1領域Aで間にボイドが形成されるように側壁スペーサ350Aを含む第1マスクパターンと、第2領域Bで間に第2マスク構造物が介在するように側壁スペーサ350B、350Cを含む第2マスクパターンを形成する。

(もっと読む)

161 - 180 / 430

[ Back to top ]