Fターム[5F083PR44]の内容

半導体メモリ (164,393) | プロセス (23,970) | メモリセルと周辺回路の同時形成 (5,561) | メモリセル (2,770) | ゲート絶縁膜 (671)

Fターム[5F083PR44]に分類される特許

161 - 180 / 671

半導体装置の製造方法

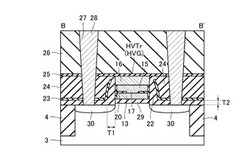

【課題】不揮発性半導体記憶装置の周辺回路領域において用いられる高耐圧トランジスタの特性及び信頼性を向上させることのできる半導体装置の製造方法を提供する。

【解決手段】半導体装置の製造方法は、シリコン基板3に周辺回路の高耐圧トランジスタHVTr用のゲート絶縁膜29を形成する工程と、ゲート絶縁膜29上にゲート電極HVGを形成する工程と、ゲート電極HVGの両側部のシリコン基板3上に位置するゲート絶縁膜29を剥離する工程と、不純物拡散領域30を形成する工程と、ゲート電極HVG及び不純物拡散領域30の表面に亘りシリコン酸化膜を堆積する工程と、シリコン酸化膜をエッチングしてゲート電極HVGの側壁部に形成されるとともに、シリコン基板3表面に延長するようにスペーサ22を形成する工程と、スペーサ22の表面にシリコン窒化膜23を形成する工程とを備える。

(もっと読む)

半導体装置およびその製造方法

【課題】FINFETにおいて、寄生抵抗の改善を図ることができる技術を提供する。

【解決手段】本発明におけるFINFETでは、サイドウォールSWを積層膜から形成している。具体的に、サイドウォールSWは、酸化シリコン膜OX1と、酸化シリコン膜OX1上に形成された窒化シリコン膜SN1と、窒化シリコン膜SN1上に形成された酸化シリコン膜OX2から構成されている。一方、フィンFIN1の側壁には、サイドウォールSWが形成されていない。このように本発明では、ゲート電極G1の側壁にサイドウォールSWを形成し、かつ、フィンFIN1の側壁にサイドウォールSWを形成しない。

(もっと読む)

半導体装置およびその製造方法

【課題】同一の半導体基板上に、高性能な低電圧MISFET、高信頼なMONOS型不揮発性メモリおよび高電圧MISFETを形成する。

【解決手段】ロジック回路などに使用される低電圧MISFETの形成領域において、キャップ酸化膜をマスクにすることによってダミーゲート電極上にシリサイドが形成されるのを防ぎ、ダマシンプロセスを用いて低電圧MISFETのゲートをhigh−k膜18およびメタルゲート電極20で形成する際の形成工程を簡略化する。また、ダミーゲート電極除去時のRIEによりダメージを受けたゲート絶縁膜を一旦除去し、新たにゲート酸化膜17を形成することで素子の信頼性を確保する。

(もっと読む)

半導体記憶装置及びその製造方法

【課題】半導体基板の表面に形成された拡散層領域における半導体基板の膨張の発生を抑制することが可能な、半導体記憶装置及びその製造方法を提供する。

【解決手段】半導体記憶装置は、半導体基板111と、半導体基板111の表面に形成され、半導体基板111の表面に平行な所定方向に沿って交互に設けられ、素子分離層121の上面の高さが活性層122の上面の高さよりも低くなっている素子分離層121及び活性層122と、活性層122の表面に形成された拡散層131と、拡散層131の上面及び側面に形成され、半導体基板111を形成する半導体よりも格子定数の小さい材料で形成されたストレスライナー132とを備える。

(もっと読む)

不揮発性半導体記憶装置およびその製造方法

【課題】本発明の目的は、さらに精度良く微細な複数のメモリセルと、高性能な複数のトランジスタと、を形成しつつ、複数の工程を1つの工程に集約させることを可能にする、不揮発性半導体記憶装置とその製造方法を提供するものである。

【解決手段】シリコン基板上に、ゲート絶縁膜用膜と浮遊ゲート電極膜用膜とゲート電極間絶縁膜用膜と制御ゲート電極膜用膜と、を積層し、制御ゲート電極膜用膜をエッチングして、同一の幅を有する複数の制御ゲート電極膜を形成する。この複数の制御ゲート電極膜の任意の数のもの毎を、それぞれトランジスタ単位となし、各トランジスタ単位におけるゲート電極間絶縁膜と浮遊ゲート電極膜とゲート絶縁膜とを形成する。各トランジスタ単位において、複数の制御ゲート電極膜に沿って形成したコンタクトホールに、コンタクトを埋め込んで、トランジスタを形成する。

(もっと読む)

半導体装置の製造方法

【課題】一つの基板上にゲート長の異なるトランジスタを形成し、ゲート長の長いトランジスタに対して少なくともESD構造を適用する場合に、ファセットの発生を抑制し、それぞれのトランジスタに適したサイドウォール(SW)幅を形成する方法を提供する。

【解決手段】基板上にゲート絶縁膜及びゲート電極材料の積層工程、第1領域にゲート長の長い第1ゲート電極の形成工程、全面に第1絶縁膜の形成工程、第2領域に第1絶縁膜を含むゲート長の短い第2ゲート電極の形成工程、全面に第2絶縁膜の形成する工程、第2ゲート電極側壁に第2絶縁膜からなる第2SW形成工程、第1ゲート電極側壁に第1及び第2絶縁膜からなる第1SW形成工程、少なくとも第1領域の露出した基板上に選択エピ層の形成工程、選択エピ層を介して基板にイオン注入し、ESD構造を形成する工程を備える製造方法。

(もっと読む)

半導体装置の製造方法

【課題】ロジック形成領域の低抵抗化と、メモリデバイスが有するキャパシタの低リーク電流化とを両立させることができる半導体技術を提供する。

【解決手段】ゲート構造5の間のソース・ドレイン領域4上と、ゲート構造55間のソース・ドレイン領域54上とに、無指向性スパッタ法を用いて金属材料を堆積する。この金属材料と半導体基板1とを互いに反応させて、ソース・ドレイン領域4,54の上面内にコバルトシリサイド膜9,59をそれぞれ形成する。そして、コバルトシリサイド膜9に電気的に接続されるキャパシタ11を形成する。ゲート構造5間の距離dmと、ゲート構造5の高さhとで規定される第1のゲートアスペクト比は、ゲート構造55間の距離dr1と、ゲート構造55の高さhとで規定される第2のゲートアスペクト比よりも大きい。

(もっと読む)

半導体記憶装置及び半導体記憶装置の製造方法

【課題】フローティングゲートとコントロールゲートとのオーバーラップ量のバラツキを抑制する。

【解決手段】基板(1)と、ゲート絶縁膜(2)を介してその基板(1)の上に設けたれたフローティングゲート(20)と、トンネル絶縁膜(30)を介してそのフローティングゲート(20)の隣に設けられたコントロールゲート(50)と、そのフローティングゲート(20)の上に設けられたスペーサー絶縁膜(9)と、そのスペーサー絶縁膜(9)とそのコントロールゲート(50)との間に設けられた保護膜(7)とを具備する半導体記憶装置(MC)を構成する。そのような半導体記憶装置(MC)において、その保護膜(7)は、スペーサー絶縁膜(9)以外の部分をエッチングするときに、スペーサー絶縁膜(9)の側面のストッパーとして機能している。

(もっと読む)

半導体装置およびその製造方法

【課題】半導体装置の性能を向上させる。

【解決手段】半導体基板1上に複数のロジック用pチャネル型MISFETQp1と、複数のロジック用nチャネル型MISFETQn1と、複数のメモリ用pチャネル型MISFETQp2と、複数のメモリ用nチャネル型MISFETQn2とが混載されている。複数のロジック用pチャネル型MISFETQp1のうちの少なくとも一部は、シリコンゲルマニウムで構成されたソース・ドレイン領域を有し、複数のロジック用nチャネル型MISFETQn1の全ては、それぞれシリコンで構成されたソース・ドレイン領域を有している。複数のメモリ用pチャネル型MISFETQp2の全ては、それぞれシリコンで構成されたソース・ドレイン領域を有し、複数のメモリ用nチャネル型MISFETQn2の全ては、それぞれシリコンで構成されたソース・ドレイン領域を有している。

(もっと読む)

不揮発性半導体記憶装置及びその製造方法

【課題】選択トランジスタの閾値が安定した不揮発性半導体記憶装置及びその製造方法を提供する。

【解決手段】不揮発性半導体記憶装置1において、シリコン基板11に複数本のSTI17を形成して、シリコン基板11の上層部分を複数本のアクティブエリアAAに区画する。また、アクティブエリアAA上にトンネル絶縁膜14及び電荷蓄積膜15を設け、STI17を覆うようにブロック絶縁膜18を設け、その上にワード電極WL及び選択ゲート電極SGを設ける。そして、STI17の上面17aにおける選択ゲート電極SGの直下域を、ワード電極WLの直下域よりも上方に位置させることにより、アクティブエリアAAの角部と選択ゲート電極SGとの間の最短距離を、アクティブエリアAAの角部とワード電極WLとの間の最短距離よりも長くする。

(もっと読む)

不揮発性半導体記憶装置及び不揮発性半導体記憶装置の製造方法

【課題】ビット線方向のセル間干渉を解消する不揮発性半導体記憶装置及び不揮発性半導体記憶装置の製造方法を提供する。

【解決手段】不揮発性半導体記憶装置は、半導体基板1と、半導体基板1を複数の素子領域に分離する素子分離絶縁膜2と、半導体基板1の素子領域上に形成されたトンネル絶縁膜3と、トンネル絶縁膜3上に形成されたフローティングゲート電極4と、積層絶縁膜5を介して、フローティングゲート電極4上及びチャネル幅方向に隣接するフローティングゲート電極4間に形成された第1コントロールゲート電極6と、半導体基板1の素子領域のチャネル幅方向に面する側面に形成されたアシスト絶縁膜7と、アシスト絶縁膜7を介して、複数の素子領域間に形成された第2コントロールゲート電極8と、を備えている。

(もっと読む)

半導体装置

【課題】不揮発性メモリセルの面積を増大することなく、かつ、製造プロセスを変更することなく、不揮発性メモリセルのデータ書き込み速度およびデータ消去速度の向上を図ることのできる技術を提供する。

【解決手段】データ書き込み・消去用の容量部CWE、データ読み出し用のMIS・FETQRおよび容量部Cを互いに異なる位置に分離した状態で配置する。容量部Cの容量電極FGC2を覆う絶縁層6上にキャップ電極CAPを設けることにより、容量部Cは、容量電極FGC2とp型のウエルHPW1との間の容量およびキャップ電極CAPと容量電極FGC2との間の容量を加算した容量を有する。また、データ書き込み・消去用の容量部CWEにおけるデータの書き換えはチャネル全面のFNトンネル電流により行う。

(もっと読む)

半導体装置の製造方法

【課題】不揮発性メモリを有する半導体装置を小型にする。

【解決手段】複数の第1電極4Gと、これに交差する複数のワード線5と、複数の第1電極4Gの隣接間であって複数のワード線5が平面的に重なる部分に配置された複数の浮遊ゲート電極6Gとを有する複数の不揮発性メモリセルMCを持つAND型のフラッシュメモリにおいて、上記複数の浮遊ゲート電極6Gの各々の断面形状を上記第1電極4Gよりも高い凸状とした。これにより、不揮発性メモリセルMCが微細化されても浮遊ゲート電極6Gを容易に加工できる上、不揮発性メモリセルMCの占有面積を増大させることなく浮遊ゲート電極6Gとワード線5の制御ゲート電極とのカップリング比を向上させることができる。

(もっと読む)

不揮発性半導体集積回路装置

【課題】不揮発性半導体集積回路装置のチップサイズを縮小させる。

【解決手段】シリコン基板上に隣り合って配置された第1および第2ゲート電極とそれらの側方下部のシリコン基板に形成された一対のソース・ドレイン領域とを有し、第2ゲート電極とシリコン基板との間に配置された第2ゲート絶縁膜に電荷を蓄えることで情報を記憶するメモリセルにおいて、メモリセルの消去動作時には、消去非選択セルの第1ゲート電極に正電圧を印加する。

(もっと読む)

半導体装置及びその製造方法

【課題】ゲートコンタクトプラグとシリコン基板とのショートを防ぐ。

【解決手段】半導体装置10は、半導体基板11と、半導体基板11の主面に対して垂直な側面を有するシリコンピラー14Bと、シリコンピラー14Bの側面を覆うゲート絶縁膜15Bと、半導体基板11の主面に対して垂直な内周側面16a及び外周側面16bを有し、ゲート絶縁膜15Bを介して内周側面16aとシリコンピラー14Bの側面とが対向するよう、シリコンピラー14Bの側面を覆うゲート電極16と、ゲート電極16の外周側面16bの少なくとも一部を覆うゲート電極保護膜17と、ゲート電極16及びゲート電極保護膜17の上方に設けられた層間絶縁膜30と、層間絶縁膜30に設けられたコンタクトホールに埋め込まれ、ゲート電極16及びゲート電極保護膜17に接するゲートコンタクトプラグGCとを備える。

(もっと読む)

ナノ構造ベースNANDフラッシュセルおよびその周辺回路の形成方法

ナノ構造に基づく電荷蓄積領域は、不揮発性メモリ装置に備えられており、選択ゲートおよび周辺回路の製造と一体に製造される。1つ以上のナノ構造コーティングは、メモリアレイ領域および周辺回路領域の基板に塗布される。選択ゲートや周辺トランジスタについての目標領域などの基板の不要な領域から、ナノ構造コーティングを除去するための様々な工程が、行われる。一例では、基盤のアクティブ領域にナノ構造を選択的に形成するために、自己組織化に基づく工程を用いて、1つ以上のナノ構造コーティングが形成される。自己組織化によって、ナノ構造コーティングのパターニングやエッチングを行うことなく、互いに電気的に分離されているナノ構造の個別のライン群を形成することができる。  (もっと読む)

(もっと読む)

不揮発性半導体記憶装置

【課題】高性能な書きこみ消去特性を有する不揮発性半導体記憶装置を提供する。

【解決手段】半導体基板のp型ウエル2上にゲート絶縁膜6を介して選択ゲート18が形成され、p型ウエル2上に酸化シリコン膜15a、窒化シリコン膜15bおよび酸化シリコン膜15cからなる積層膜15を介してメモリゲート17が形成される。メモリゲート17は、積層膜15を介して選択ゲート18に隣接する。p型ウエル2の選択ゲート18およびメモリゲート17の両側の領域には、ソース、ドレインとしてのn型の不純物拡散層20,21が形成されている。不純物拡散層20,21の間に位置するチャネル領域のうち、選択ゲート18により制御され得る領域51とメモリゲート17により制御され得る領域52とにおける不純物の電荷密度が異なる。

(もっと読む)

半導体装置およびその製造方法

【課題】各々ばらつきの少ない異なる閾値電圧を有する複数のトランジスタを備えた半導体装置およびその製造方法を提供する。

【解決手段】本発明の一態様に係る半導体装置は、半導体基板2上に形成された高誘電率材料を母材料とするゲート絶縁膜11、ゲート電極12、およびゲート絶縁膜11に接するように形成されたSiNを主成分とする絶縁材料からなるオフセットスペーサ13、を有する低閾値電圧MISFET10と、半導体基板2上に形成された高誘電率材料からなるゲート絶縁膜21、ゲート電極22、およびゲート絶縁膜21に接するように形成されたSiNを主成分とする絶縁材料からなるオフセットスペーサ23、を有する高閾値電圧MISFET20と、を有し、オフセットスペーサ23は、オフセットスペーサ13よりも、単位体積当たりのSi−H結合とN−H結合の存在比、単位体積当たりのClの量、および単位体積当たりのHの量の少なくともいずれか1つが大きい。

(もっと読む)

半導体装置

【課題】回路を形成する領域を確保しつつ、十分な耐圧、容量を備えた容量素子を備える半導体装置を提供する。

【解決手段】半導体装置は、DRAMセルのキャパシタ上部電極19と、上部電極19の下方に形成されたキャパシタ下部電極17とを含む情報記憶部と、情報記憶部へのアクセスを制御するアクセストランジスタとを有するメモリセルと、アクセストランジスタに接続され、情報記憶部にデータの書き込み又は読み出しを行うビット線16と、アクセストランジスタのゲート電極に接続され、アクセストランジスタを制御するワード線と、キャパシタ上部電極19の上方に形成された第1金属配線21と同一層からなる上部電極23と、キャパシタ上部電極19と同一層の下部電極22とを有し、メモリセルが形成された領域外に形成された容量素子とを備える。

(もっと読む)

半導体記憶装置及びその製造方法

【課題】微細化が進んだ場合であってもトランジスタのカットオフ特性を改善する。

【解決手段】半導体基板100上に形成されるp型ウェル2には、ビット線BLの長手方向に沿って形成されたトレンチ3に素子分離絶縁膜4が埋め込まれている。素子分離絶縁膜4によりp型ウェル2が分離され、メモリトランジスタが形成される素子形成領域2Aが形成される。素子分離絶縁膜4にはボロン等のp型不純物が注入されており、その不純物濃度は、p型ウェル2の不純物濃度よりも大きい。

(もっと読む)

161 - 180 / 671

[ Back to top ]