Fターム[5F083PR44]の内容

半導体メモリ (164,393) | プロセス (23,970) | メモリセルと周辺回路の同時形成 (5,561) | メモリセル (2,770) | ゲート絶縁膜 (671)

Fターム[5F083PR44]に分類される特許

201 - 220 / 671

半導体装置及びその製造方法

【課題】半導体界面のダングリングボンドを終端させて、リーク電流が少ない半導体装置の製造方法を提供する。

【解決手段】ボンディングパッド40が設けられる最上層の配線層39の上に、フッ素を含んだ介在層41としてCVD法によりよって形成されたフッ素含有酸化シリコン膜(SiOF)を設ける。この上にパッシベーション膜42としてプラズマCVD法により形成した窒化シリコン膜を設け、フッ素に対するバリアとする。この後熱処理を行い、フッ素をシリコン基板の表面に拡散させる。

(もっと読む)

半導体装置の製造方法

【課題】メモリセル領域および周辺回路領域に素子分離溝を同時に形成するときに、メモリセル領域の素子分離溝の深さを十分深くすると共に、周辺回路領域の素子分離溝の深さが深くなりすぎることを防止する。

【解決手段】素子分離溝を形成する際に、半導体基板1上に形成した絶縁膜を加工するとき、メモリセル領域の薄い絶縁膜についてはすべて除去するようにエッチングし、周辺回路領域の厚い絶縁膜については途中で加工が止まるようにエッチングし、この後、周辺回路領域の残存する絶縁膜をエッチングストッパーとして半導体基板1をエッチングし、次いで、周辺回路領域の残存する絶縁膜をすべて除去した後、再び半導体基板1をエッチングした。

(もっと読む)

半導体装置の製造方法

【課題】歩留まりが向上して信頼性の高いフラッシュメモリセルを備えた半導体装置の製造方法を提供すること。

【解決手段】第1窓70aを有する第1レジストパターン70を第2絶縁膜69上に形成する工程と、第1レジストパターン70をエッチングマスクにしてコンタクト領域CRが露出する第1開口69dを形成する工程と、第1レジスト部76aを有する第2レジストパターン76を第2導電膜74上に形成する工程と、第2レジストパターン76をエッチングマスクにし、第1、第2導電体67a、74a、フローティングゲート67d、及びコントロールゲート74dを形成する工程と、第3レジストパターン80を各領域I、IIに形成する工程と、第3レジストパターン80をエッチングマスクにして第2窓80a下の第2導電体74aを除去する工程と、を有する半導体装置の製造方法による。

(もっと読む)

半導体装置とその製造方法

【課題】

ロジックプロセスと適合性が高く、ノイズに対して強い耐性を有するメモリ回路を含む半導体装置とその製造方法を提供する。

【解決手段】

半導体装置は、複数のメモリセルが第1および第2の方向に沿って行列状に配置されたメモリセルアレイ、および第1および第2のセンスアンプを含む複数のセンスアンプ、を形成した半導体基板を含み、メモリセルの各々は絶縁ゲート電極とその両側に形成されたビット線コンタクト領域と他のソース/ドレイン領域を備えたトランジスタと、他のソース/ドレイン領域に接続されたキャパシタとによって構成される。メモリセルアレイ上方に、第1の方向に沿って延在し、複数のビット線コンタクト了以金に接続され、第2の方向に並んで配置された複数のビット線を含む。第1のセンスアンプに接続される第1対のビット線は、第1配線層で形成され、第2のセンスアンプに接続される第2対のビット線は、第1の配線層と異層の第2配線層で形成される。

(もっと読む)

半導体装置の製造方法および半導体装置

【課題】スプリットゲート型メモリセル構造を採用し、電荷蓄積層として窒化膜を用いる不揮発性メモリを有する半導体装置において電気的特性を向上させる。

【解決手段】半導体基板1Subの主面にn型の半導体領域6を形成した後、その上にスプリットゲート型のメモリセルのメモリゲート電極MGおよび電荷蓄積層CSLを形成する。続いて、そのメモリゲート電極MGの側面にサイドウォール8を形成した後、半導体基板1Subの主面上にフォトレジストパターンPR2を形成する。その後、フォトレジストパターンPR2をエッチングマスクとして、半導体基板1Subの主面の一部をエッチングにより除去して窪み13を形成する。この窪み13の形成領域では上記n型の半導体領域6が除去される。その後、その窪み13の形成領域にメモリセル選択用のnMISのチャネル形成用のp型の半導体領域を形成する。

(もっと読む)

不揮発性半導体記憶装置及びその製造方法

【課題】メモリトランジスタの特性が良好な不揮発性半導体記憶装置及びその製造方法を提供する。

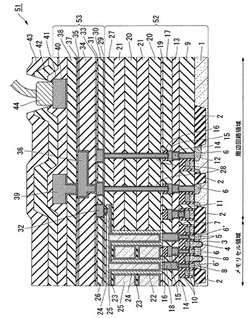

【解決手段】シリコン基板11上に、それぞれ複数の絶縁膜及び電極膜14が交互に積層された積層体を設ける。電極膜14は、X方向に延びる複数本の制御ゲート電極CGに分断する。また、積層体内に、選択ゲート電極SGb、SGs、制御ゲート電極CGを貫き、一端がソース線SLに接続され、他端がビット線BLに接続されたU字ピラー30を設ける。そして、各制御ゲート電極CGは、Y方向において隣り合う2本のシリコンピラー31によって貫かれており、接続部材32によって相互に接続された2本のシリコンピラー31は、相互に異なる制御ゲート電極CGを貫いている。

(もっと読む)

半導体装置

【課題】非接触でデータの送受信が可能な安価な半導体装置及びその作製方法の提供する。

【解決手段】基板32に、メモリセルの有機化合物層20bに流れる電流を制御する素子であるTFT、ビット線である第1の電極層18a〜18c、ソース線17a〜17c、第2の電極層21、第1の電極層18a〜18cと第2の電極層21の間に有機化合物を含む積層(第1層(バッファ層20a)と第2層(有機化合物層20b)の積層)を設けている。有機化合物層20bは、導電性を有する有機化合物材料からなる層を単層または積層構造で設ける。導電性を有する有機化合物材料の具体例としては、キャリア輸送性を有する材料を用いることができる。集積回路部の接続電極28、電極29上にアンテナ30を形成する。

(もっと読む)

半導体装置およびその製造方法

【課題】不揮発性メモリセルを有する半導体装置において、駆動力の低下を抑えて、信頼度を向上させることのできる技術を提供する。

【解決手段】メモリセルMC1をp型の導電性を示す導電膜からなる選択ゲート電極CGを有する選択用pMIS(Qpc)とp型の導電性を示す導電膜からなるメモリゲート電極MGを有するメモリ用pMIS(Qpm)とから構成し、書込み時には半導体基板1側からホットエレクトロンを電荷蓄積層CSLへ注入し、消去時にはメモリゲート電極MGからホットホールを電荷蓄積層CSLへ注入する。

(もっと読む)

半導体装置およびその製造方法

【課題】接合リーク電流を低減可能なDRAM型半導体装置を提供する。

【解決手段】メモリセル部内におけるゲート絶縁膜8の厚みを周辺回路部内におけるゲート絶縁膜9の厚みよりも大きくする。また、メモリセル部におけるMOSトランジスタのソース/ドレインを二重拡散層構造5,6とし、周辺回路部におけるMOSトランジスタのソース/ドレインを三重拡散層構造5,6,7にする。このようにメモリセル部内におけるゲート絶縁膜8の厚みを周辺回路部内におけるゲート絶縁膜9の厚みよりも大きく設定することにより、メモリセル部内におけるp型不純物領域4aの濃度を低くすることが可能となり、接合リーク電流を低減することが可能となる。

(もっと読む)

半導体装置

【課題】半導体装置の製造歩留りを向上させる。

【解決手段】素子分離領域2を含む半導体基板1上に多結晶シリコン膜7と絶縁膜8を形成してパターニングし、多結晶シリコン膜7かならる下部電極11a,11bおよび下部電極11a,11b間のダミーパターン12を形成する。下部電極11a,11bおよびダミーパターン12とそられの上に形成された絶縁膜8を覆うように多結晶シリコン膜17を形成し、多結晶シリコン膜17上にキャップ保護膜を形成する。キャップ保護膜上に反射防止膜およびフォトレジストパターンを形成し、フォトレジストパターンをエッチングマスクとして用いて反射防止膜、キャップ保護膜および多結晶シリコン膜17を順次ドライエッチングすることで、下部電極11a,11b上に容量絶縁膜としての絶縁膜8を介して多結晶シリコン膜17からなる上部電極21a,21bを形成してキャパシタ36a,36bを形成する。

(もっと読む)

半導体装置とその製造方法

【課題】同一基板内にEPROMとEPROM以外の機能デバイスを備えた半導体装置に関する技術を提供する。

【解決手段】半導体装置10では、EPROM領域Aにおいて、半導体基板20上に半導体基板20の側からゲート酸化膜41とフローティングゲート電極42と絶縁膜43とコントロールゲート電極44がこの順に積層されて構成されている。また、DRAM領域Bにおいて、半導体基板20上に半導体基板20の側から絶縁膜43と金属膜(ソース電極67、87とドレイン電極68、88を含む)がこの順に積層されて構成されている。本実施例の半導体装置10では、EPROM領域Aの絶縁膜43とDRAM領域Bの絶縁膜43が同一層で形成されており、EPROM領域Aのコントロールゲート電極44とDRAM領域Bの金属膜が同一層で形成されている。そのため、半導体装置10を形成する際に、その工程が増加することが抑制される。

(もっと読む)

半導体集積回路装置およびその製造方法

【課題】多値記録が可能なメモリセルを備えた半導体記憶装置の性能を向上させる。

【解決手段】シリコン基板100上に配置された複数のメモリセルを有する半導体集積回路装置であって、個々のメモリセルは、素子分離膜118で規定されたアクティブ領域において、ボトム酸化膜105、電荷蓄積窒化膜106、トップ酸化膜107を介して形成されたメモリゲート電極103を有する。素子分離膜118の一部上面は、アクティブ領域上面の高さよりも高くなるように突出して形成され、電荷蓄積窒化膜106はその素子分離膜118が突出した部分の側壁から、アクティブ領域表面に渡って形成されている。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】メモリセル部でアスペクト比の高い下部電極の倒壊を防止するとともに、前記メモリセル部に隣接する周辺回路部への薬液の浸透を防止する半導体装置および半導体装置の製造方法を得るという課題があった。

【解決手段】メモリセル部と、前記メモリセル部を囲む周辺回路部と、を有する半導体装置であって、前記メモリセル部は、複数の筒状の下部電極13と、下部電極13の側面を覆う第1の絶縁膜と、前記第1の絶縁膜を覆う上部電極15と、を有するキャパシタ30を備えたメモリセル本体部55と、メモリセル本体部55を囲む溝部73を備えたメモリセル外周部56と、を有しており、下部電極13の筒内に充填された第1の支持膜61と、第1の支持膜61の開口側の面に接面されるとともに複数の下部電極13を結ぶように延在された第2の支持膜62と、を有する半導体装置を用いることにより、上記課題を解決できる。

(もっと読む)

半導体装置

【課題】ワード線引き出し部におけるワード線とシリコン基板との距離をセルアレイ領域内に比して長く確保でき、耐圧を向上させることができる半導体装置を提供する。

【解決手段】セルアレイ領域の半導体基板14上には、第1の膜厚を持つトンネル酸化膜18、及び第1ゲート電極を有するメモリセルトランジスタが形成されている。周辺回路領域の半導体基板14上には、第1の膜厚より厚い第2の膜厚を持つゲート酸化膜を有する高電圧トランジスタが形成される。ワード線3は、メモリセルトランジスタの第1ゲート電極に接続され、ワード線引き出し領域の半導体基板14上に延伸している。ワード線引き出し領域において、半導体基板14とワード線3との間には、第1の膜厚より厚く、第2の膜厚より薄い第3の膜厚を持つシリコン酸化膜15が形成されている。

(もっと読む)

メモリデバイス及びメモリデバイスの形成方法

【課題】プログラマブルMOSFET(105)とロジックMOSFET(110)とを含むメモリデバイスを同一チップ上に形成する。

【解決手段】半導体基板を被う層状ゲート積層体の成形から始まり、層状ゲート積層体の高kゲート電極層上で停止するよう金属ゲート電極層にパターンを形成して、半導体基板上に第1、第2ゲート金属ゲート電極(16、21)を形成するメモリデバイスの製法が提供される。次のプロセスで、高kゲート誘電体層の一部を被う少なくとも1つのスペーサ(55)を第1ゲート電極(16)に形成する。高kゲート誘電体層の露出された残存部分をエッチングし、第1金属ゲート電極のサイドウォールを越えて延びる部分を有する第1高kゲート誘電体(17)及び第2金属ゲート電極(21)のサイドウォールに整合されたエッジを有する第2高kゲート誘電体(22)を形成する。

(もっと読む)

半導体記憶装置及びその製造方法

【課題】選択ゲートトランジスタの隣りに配置されたメモリセルの閾値電圧の上昇を防ぎ、選択ゲートトランジスタ間の側壁絶縁膜を薄膜化できる半導体記憶装置を提供する。

【解決手段】周辺トランジスタの第3側壁絶縁膜の膜厚は、選択ゲートトランジスタの第1側壁絶縁膜、及び隣接した選択ゲートトランジスタの第2側壁絶縁膜より膜厚が厚い。メモリセルのゲート電極MGと選択ゲートトランジスタの選択ゲート電極SG1との間隔はゲート電極MG間の間隔より広く、選択ゲート電極SG1と選択ゲートトランジスタの選択ゲート電極SG2との間隔はゲート電極MGと選択ゲート電極SG1との間隔より広い。

(もっと読む)

半導体装置

【課題】強誘電体キャパシタの疲労特性の不揃いを抑制できる半導体装置を提供することにある。

【解決手段】半導体基板1の上方に形成され、金属を有するキャパシタの下部電極18bと、下部電極18bの上に形成されるキャパシタQの誘電体膜と、誘電体膜上に形成され、能動素子に電気的に接続されるキャパシタQの上部電極と、キャパシタQを覆う絶縁膜と、下部電極のコンタクト領域25cの上に形成されるホールを有する半導体装置であって、ホールと上部電極19bの距離はホール直径又はホール面積との関係において決定される。

(もっと読む)

半導体記憶装置およびその製造方法

【課題】強誘電体キャパシタの側壁残渣を除去し、かつ、水素による強誘電体キャパシタの特性劣化を抑制する半導体記憶装置およびその製造方法を提供する。

【解決手段】半導体記憶装置は、半導体基板上に設けられたスイッチングトランジスタと、スイッチングトランジスタ上に形成された層間絶縁膜と、層間絶縁膜中に形成されたコンタクトプラグと、コンタクトプラグおよび層間絶縁膜の上方に形成され、下部電極、強誘電体膜および上部電極を含む強誘電体キャパシタと、半導体基板に形成され、コンタクトプラグとスイッチングトランジスタとの間を電気的に接続する拡散層と、強誘電体キャパシタの側面に形成された水素バリア膜と、上部電極の上面全体を被覆しかつ該上部電極の上面に接触するTiN膜またはTiAlN膜を含む配線とを備えている。

(もっと読む)

半導体装置の製造方法

【課題】MISFETのしきい値のばらつきを抑制する。

【解決手段】半導体基板1に素子分離領域2を形成し、MISFETのしきい値調整用のチャネルドープイオン注入を行なってから、ゲート絶縁膜5a,5bおよびゲート電極GE1,GE2を形成する。それから、イオン注入によりエクステンション領域7a,7bおよびハロー領域8a,8bを形成し、更に炭素(C)、窒素(N)またはフッ素(F)のうちの1種以上をイオン注入することにより拡散防止領域10a,10bを形成する。その後、ゲート電極GE1,GE2の側壁上にサイドウォールSWを形成してから、イオン注入により、ソース・ドレイン用のn+型半導体領域11aおよびp+型半導体領域11bを形成して、nチャネル型MISFETおよびpチャネル型MISFETが形成される。

(もっと読む)

半導体装置の製造方法および半導体装置

【課題】層間絶縁膜を表面研磨する工程を経て形成される半導体装置の信頼性を向上させる。

【解決手段】シリコン基板1の主面s1上に、高耐圧ゲート絶縁膜IG1および高耐圧ゲート電極EG1からなる高耐圧ゲートG1を形成した後、サリサイドブロック膜SAB、層間絶縁膜ILを順に形成し、その層間絶縁膜ILをCMPにより研磨する。サリサイドブロック膜SABは、下層から順に酸化シリコンを主体とする絶縁膜である保護酸化膜t1と、窒化シリコンを主体とする絶縁膜である保護窒化膜t2とによって形成する。また、層間絶縁膜ILの研磨は、高耐圧ゲートG1上面のサリサイドブロック膜SABに達するまで研磨する。

(もっと読む)

201 - 220 / 671

[ Back to top ]