Fターム[5F083ZA10]の内容

Fターム[5F083ZA10]に分類される特許

1 - 20 / 195

半導体装置

【課題】複数の貫通電極を選択的に利用可能な積層型の半導体装置において、回路動作を安定させる。

【解決手段】半導体記憶装置10は、インターフェースチップIFと複数のコアチップCCを含む。コアチップCCは、インターフェースチップIFに積層される。インターフェースチップIFとコアチップCCは複数の貫通電極TSVにより接続される。コアチップCCに含まれる入力切り替え回路240、230は、電源投入時における設定処理の前に、コアチップCCに含まれる複数の入力信号線と複数の貫通電極TSVとの接続をいったん遮断し、コアチップCCの設定後に、複数の入力信号線と複数の貫通電極TSVの接続を示す救済情報にしたがって各入力信号線を複数の貫通電極TSVのいずれかと接続する。

(もっと読む)

半導体回路装置およびその製造方法

【課題】ビアヒューズ素子の径を小さくし、ビアヒューズ素子を低電流で溶断することが可能な半導体回路装置およびその製造方法を提供する。

【解決手段】一方向に配置された複数の配線層と、前記複数の配線層のうちの少なくとも2つの前記配線層の間に設けられたビアヒューズ素子と、前記複数の配線層の配置方向に直交する平面内において前記ビアヒューズ素子に隣接する穴と、前記穴内に設けられた貫通ビアとを備えた半導体回路装置。

(もっと読む)

不揮発性記憶素子、不揮発性記憶装置、不揮発性半導体装置、および不揮発性記憶素子の製造方法

【課題】 動作の高速化を図ることができ、可逆的に安定した書き換え特性と、良好な抵抗値のリテンション特性を有し、半導体製造プロセスと親和性の高い不揮発性記憶素子およびその製造方法、並びにその不揮発性記憶素子を備える不揮発性記憶装置および不揮発性半導体装置を提供する。

【解決手段】 本発明の不揮発性記憶素子は、第1電極103と、第2電極105と、第1電極103と第2電極104との間に介在させ、両電極103,105間に与えられる電気的信号に基づいて可逆的に抵抗値が変化する抵抗変化層104とを備え、この抵抗変化層104は少なくともタンタル酸化物を含み、当該タンタル酸化物をTaOxと表した場合に、0<x<2.5を満足するように抵抗変化層104が構成されている。

(もっと読む)

半導体ウエハ、半導体装置、および、半導体装置の製造方法

【課題】半導体チップのチップ面積の削減を図るとともに、半導体チップへの入力を記憶させる時間を短縮する。

【解決手段】本発明の半導体ウエハ1は、チップ領域10に形成され、絶縁膜を有し、電圧の印加による絶縁膜の絶縁破壊により導通状態となる複数のアンチヒューズ14を有するアンチヒューズ回路12と、チップ領域10を区画するダイシング領域20に複数のアンチヒューズ14の各々に対応して形成され、配線を有し、レーザー照射による配線の切断により非導通状態となる複数のレーザーヒューズ24を有するレーザーヒューズ回路22と、複数のアンチヒューズ14のうち、半導体チップへの入力に応じて非導通状態とされたレーザーヒューズ22に対応するアンチヒューズ14の有する絶縁膜に、電源からの電圧を印加させて、そのアンチヒューズ14を導通状態とする制御回路13と、を有する。

(もっと読む)

半導体装置の製造方法及び半導体装置

【課題】半導体チップを積層して半導体装置を製造する際に、当該半導体チップの回路の不良電子素子を救済し、半導体装置の歩留まりを向上させる。

【解決手段】ウェハ10を厚み方向に貫通する一対の貫通電極50〜52を形成し、デバイス層11に一対の貫通電極50〜52を短絡する共有配線24、26、28を形成し、デバイス層11の表面11aにおいて異なる場所につながる一対のフロントバンプ20〜22を形成する。一対の貫通電極50〜52に対して異なる極性で電圧を印加し、一対の貫通電極50〜52のうちの一の貫通電極50〜52上にバックバンプ80〜82を形成する。ウェハ10を積層し、一のウェハ10上のバックバンプ80〜82と、他のデバイス層11上のフロントバンプ20〜22とを接続する。

(もっと読む)

不揮発性半導体記憶装置

【課題】アクセス性能の向上を図ることが可能な不揮発性半導体記憶装置を提供する。

【解決手段】不揮発性半導体記憶装置は、データバッファに格納されエラー訂正されたリードデータを第1の入出力ピンから出力するのに同期して、エラー訂正されたリードデータに対応する第1のパリティフラグを第2の入出力ピンから出力する。

(もっと読む)

半導体装置

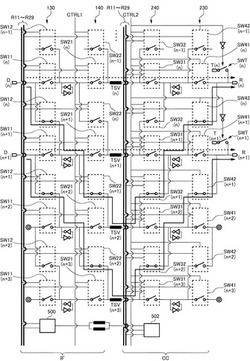

【課題】貫通電極を用いた積層型の半導体装置において不良のある信号経路を救済する。

【解決手段】インターフェースチップIFと、互いに積層されたコアチップCC0〜CC7と、コアチップCC0〜CC7を貫通する複数の貫通電極TSV3により構成され、コアチップCC0〜CC7をインターフェースチップIFにそれぞれ個別に接続する複数の第1の信号経路と、コアチップCC0〜CC7を貫通する複数の貫通電極TSV1により構成され、コアチップCC0〜CC7をインターフェースチップIFに共通接続する第2の信号経路と、複数の第1の信号経路のいずれかを第2の信号経路に置換する切り替え回路110とを備える。本発明によれば、貫通電極の全てに切り替え回路を設ける必要がなくなる。また、救済のために追加する貫通電極の数も最小限に抑えられることから、チップ面積の増大を抑制することも可能となる。

(もっと読む)

半導体記憶装置

【課題】 長期間のデータ保持特性に優れ、読み出し時のデータの誤り検出および訂正を効率よく行うことのできる半導体記憶装置を実現する。

【解決手段】

金属酸化物を用いた可変抵抗素子を情報の記憶に用いる半導体記憶装置1において、当該可変抵抗素子を高抵抗状態に遷移させる場合に印加する書き換え電圧パルスの電圧振幅を、遷移後の高抵抗状態の抵抗値が時間の経過とともに上昇するデータ保持特性となる電圧範囲内に設定する。具体的には、当該電圧振幅を上昇させるに伴って遷移後の高抵抗状態の抵抗値が所定のピーク値に向って上昇する電圧範囲に設定する。そして、ECC回路106によりデータ誤りが検出された場合、本来低抵抗状態であるべきデータが高抵抗状態に変化したとみなして、誤りが検出された全てのメモリセルの可変抵抗素子を低抵抗状態に書き換え、誤りが検出されたビットを訂正する。

(もっと読む)

半導体装置およびその製造方法

【課題】オフ電流を増加させることなく電源供給配線の電気抵抗を下降させることが可能な、TFTを有する半導体装置を提供することである。

【解決手段】表面を有する絶縁膜II4と、絶縁膜II4の表面上に形成され、かつチャネル領域TP2と、チャネル領域TP2を挟む1対のソース/ドレイン領域TP1,TP4とを含む半導体層と、ソース領域TP1に電源を供給するための電源供給配線TP1とを備えている。上記絶縁膜II4の表面には凹部TRが形成されている。上記電源供給配線TP1は、半導体層と同一の層から形成された層を含み、かつ絶縁膜II4の表面上に形成された第1の部分TP1Aと、凹部内に形成された第2の部分TP1Bとを有している。上記第2の部分TP1Bの底面全体が絶縁体II4で覆われている。

(もっと読む)

半導体装置

【課題】占有面積の小さな直線状の電気ヒューズを有する半導体装置を提供する。

【解決手段】複数の突出部10fは、電気ヒューズ部10aの中央位置からずれた位置、より具体的には、ビア10dに近くかつビア10eから遠い位置に設けられている。また、複数の突出部20fは、電気ヒューズ部20aの中央位置からずれた位置、より具体的には、ビア20dから遠くかつビア20eに近い位置に設けられている。つまり、突出部10fおよび突出部20fは、ジグザグ状に配置されている。

(もっと読む)

半導体メモリ装置及びそのリペア方法

【課題】リペア過程が簡素化された半導体メモリ装置及びそのリペア方法を提供する

【解決手段】半導体メモリ装置200は、複数のメモリセルを含む第1のメモリチップないし第3のメモリチップ210〜230と、第1のリペアチップ240とを備え、第1のリペアチップ240は、第1のメモリチップないし第3のメモリチップ210〜230のそれぞれに含まれた複数のメモリセル212A,212B,・・・のうち、欠陥が発生した任意のメモリセルをリペアするための第1のヒューズ回路ないし第3のヒューズ回路241A,241B,243A,243B,245A,245Bと、メモリチップ210〜230毎に欠陥が発生した任意のメモリセルを代替するための、複数の第1のリダンダンシメモリセルないし第3のリダンダンシメモリセル242A,242B,244A,244B,246A,246Bとを含む。

(もっと読む)

半導体記憶装置

【課題】DRAMの回路規模や信号伝搬時間を抑制する。

【解決手段】半導体記憶装置には、不良なメモリセルのアドレスを記憶するためのヒューズ素子120が配列されるヒューズ領域116が形成される。ヒューズ領域116のまわりにはガードリング118が形成され、ガードリング118はパッシベーション膜124によって覆われる。ただし、ヒューズ領域116の上のパッシベーション膜124には開口部126が設けられる。ガードリング118は、第1層128の第1リング134、第2層130の第2リング136および第3層132の第3リング138とそれらを接続する第1接続リング142、第2接続リング144を含む。ここで、第2リング136の下に第1リング134の非形成領域が確保されるように、第1リング134を第2リング136の内側に配置する。

(もっと読む)

半導体装置、及び半導体装置の制御方法。

【課題】簡便な半導体装置の評価試験を実現する。

【解決手段】半導体装置10は、それぞれ内部信号MAを生成する第1及び第2のコアチップCC0,CC1を備え、第1及び第2のコアチップCC0,CC1のそれぞれに、貫通電極を介して他方のコアチップとスパイラル接続された第2及び第3のノードN2,N3を設け、この第2及び第3のノードN2,N3を介して、観測対象の内部信号MAを外部に出力することを技術思想とするものである。こうして出力される複数の内部信号MAを外部のテスター等によって観測することで、各コアチップの評価試験を並列に行える。

(もっと読む)

抵抗変化型メモリ

【課題】メモリの動作マージンを向上する。

【解決手段】本実施形態の抵抗変化型メモリは、ビット線BLA,BLC間に接続された第1のセルSCAとビット線BLB,BLC間に接続された第2のセルSCBとを含むメモリセルMCと、第1のセルSCAを形成するメモリ素子8A及び選択トランジスタTrAと、第2のセルSCBを形成するメモリ素子8B及び選択トランジスタTrBとを具備し、メモリセルに対する書き込み動作時、ワード線が活性化されている期間において、メモリセルMC内の2つのメモリ素子8A,8Bを第1の抵抗状態に変化させた後、2つのメモリ素子8A,8Bのうち一方のメモリ素子を第2の抵抗状態に変化させる。

(もっと読む)

半導体記憶装置

【課題】低消費電力且つ省スペースな半導体記憶装置を提供する。

【解決手段】実施形態に係る半導体記憶装置は、異なる抵抗状態によってデータを記憶する複数のメモリセルからなるメモリセル層を有するメモリセルアレイと、第1配線及び第2配線を介して前記メモリセルにアクセスするアクセス回路とを備え、メモリセルは、第1極性の所定の電圧が印加されると抵抗状態が第1抵抗状態から第2抵抗状態に遷移し、第2極性の所定の電圧が印加されると抵抗状態が第2抵抗状態から第1抵抗状態に遷移し、アクセス回路は、選択したメモリセルに接続された第1配線及び第2配線に前記メモリセルのアクセスに必要な電圧を印加する共に、非選択の前記メモリセルに接続された第1配線及び第2配線の少なくとも一方をフローティング状態にして、選択したメモリセルにアクセスすることを特徴とする。

(もっと読む)

欠陥フラッシュメモリダイの動作不能化

【課題】複数のフラッシュメモリダイを含むデバイス内の欠陥フラッシュメモリダイを動作不能化する製品ならびに関連する方法およびシステムを提供する。

【解決手段】動作不能化されていないフラッシュメモリダイに基づくフラッシュメモリのデータ記憶容量を示すラベルを、複数のフラッシュメモリダイを含むパッケージに付すことができる。ダイレベル、パッケージレベル、および/またはボードレベルにおいて、様々な動作不能化方法を適用することができる。

(もっと読む)

半導体装置及びその試験方法

【課題】論理値の反転処理を行う回路をコアチップ側に設けることなく、TSVを含む電流パスラインのショート不良を検出する。

【解決手段】半導体装置10は、第1及び第2の電流パスSa,Sbと、これらとそれぞれ電気的に接続する第1及び第2のラッチ回路100a,100bと、第1のラッチ回路100aに第1のデータD1を供給するとともに、第2のラッチ回路100bに第1のデータとは逆の論理値を有する第2のデータD2を供給するドライバ回路101と、第1のデータD1が第1のラッチ回路100aに供給され、かつ第2のデータD2が第2のラッチ回路100bに供給されない第1の期間と、第2のデータD2が第2のラッチ回路100bに供給され、かつ第1のデータD1が第1のラッチ回路100aに供給されない第2の期間と、が交互に繰り返されるよう、ドライバ回路101を制御する制御回路104と、モニタ回路120とを備える。

(もっと読む)

半導体メモリ装置及びそのリペア方法

【課題】 本発明は単一の半導体装置を構成する複数個のチップでヒューズ情報を伝送できる半導体装置に関することである。

【解決手段】半導体装置は信号伝送部及び信号受信部を含む。信号伝送部は第1チップに配置されて、伝送制御信号に同期してヒューズ情報を伝送する。信号受信部は第1チップ及び第2チップに各々配置されて、受信制御信号に同期して前記ヒューズ情報を受信する。

(もっと読む)

半導体装置

【課題】制御チップと複数の被制御チップが積層されたタイプの半導体装置において、コマンド信号よりも層アドレス信号を早く伝送させる。

【解決手段】互いに異なる層情報を保持する複数の被制御チップCC0〜CC7と、被制御チップCC0〜CC7に対して層アドレス信号A13〜A15及びコマンド信号ICMDを共通に供給する制御チップIFとを備える。層アドレス信号A13〜A15を構成する各ビットは、複数の第1の貫通電極のうち、被制御チップごとに並列接続された少なくとも2本の貫通電極を経由して伝送され、コマンド信号ICMDを構成する各ビットは、出力切り替え回路及び入力切り替え回路によって選択された対応する1本の貫通電極を経由して伝送される。これにより、コマンド信号ICMDよりも先に層アドレス信号A13〜A15が各被制御チップに到達する。

(もっと読む)

半導体記憶システム

【課題】 複数のチップを実装した場合において、複数のチップ間で通信する通信線を設けることなく、ピーク電流を抑制可能な半導体記憶システムを提供する。

【解決手段】 半導体記憶システムによれば、電源配線81は、第1の半導体記憶装置71aと第2の半導体記憶装置71bに共通接続され、第1、第2の半導体記憶装置に電源を供給する。電圧検知回路74a,74b,74cは、第1、第2の半導体記憶装置のそれぞれに設けられ、電源配線の電源電圧を検知する。制御回路7は、第1、第2の半導体記憶装置のそれぞれに設けられ、電圧検知回路により電源電圧の低下が検知された場合、電源電圧が復帰するまで、第1、又は第2の半導体記憶装置の動作を、次の動作に遷移させない。

(もっと読む)

1 - 20 / 195

[ Back to top ]