Fターム[5F092BA15]の内容

Fターム[5F092BA15]に分類される特許

1 - 20 / 45

磁気デバイスの製造方法

【課題】ダイシングストリートにGaAsが露出している場合、結果ダイシング時に素子のチッピング、電極や磁性体の剥離、溶解したGaAsによる電極接合部の汚染が発生し、さらにGaAs基板裏面もエッチングされるためGaAsの溶解による電極接合部の汚染の課題がある。

【解決手段】本発明は、ホール素子が設けられたGaAs基板と、GaAs基板上に設けられた磁気増幅機能を有する磁性体とを備える磁気デバイスにおいて、上記ホール素子上に絶縁層と、上記絶縁層上にTi系金属層と、上記Ti系金属層の上にCu系金属層とを有し、ダイシングストリート上を少なくとも無機絶縁材料乃至有機絶縁材料もしくはその両方でカバーさせGaAsを露出させず、またさらにGaAs基板裏面にも有機絶縁膜でカバーすることにより本課題を解決した。

(もっと読む)

電圧駆動型電磁石

【課題】室温付近で電圧によりキュリー温度を変化させることができ、かつ大きな磁化、即ち大きな磁界を発生させることが可能な電圧駆動型電磁石を提供する。

【解決手段】鉄、コバルト、ニッケルのうちのいずれか、もしくはこれらのうち少なくとも一つを含む合金からなる強磁性金属薄膜層12と、前記強磁性金属薄膜層12の片側に積層された絶縁層20と、前記絶縁層20の、前記強磁性金属薄膜層12とは反対側に設けられたゲート電極30と、前記強磁性金属薄膜層12と前記ゲート電極30の間に電圧を印加する電圧印加部40とを備える電圧駆動型電磁石を提供する。また、強磁性金属薄膜層12内の磁化を特定の方向に配向させる下地層13と、配向させた強磁性金属薄膜層12内の磁化の方向を維持させるキャップ層11を備える。

(もっと読む)

磁気センサ

【課題】ホール素子を有する磁気センサにおいて、簡易な回路構成である信号処理回路で、ホール素子の出力電圧に含まれるオフセット電圧及びフリッカノイズを除去することのできる磁気センサを提供する。

【解決手段】ホールプレートHは、ホールプレートHを流れる電流のキャリアの種類を、ゲート電極Gの電位Vgにより、電子または正孔のいずれか一方にすることが可能な両極性材料から形成される。さらに、入出力端子TA,TA’,TB,TB’が、ホールプレートHの面内で対向する電流入力端子対と電圧出力端子対とになり、その際に電流入出力端子対と電圧出力端子対とが互いに直交するような位置に形成される。

(もっと読む)

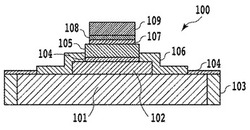

半導体装置及びその製造方法

【課題】低保磁力をもつ軟磁性薄膜を備え、この軟磁性薄膜で磁気収束する半導体装置及びその製造方法を提供すること。

【解決手段】半導体基板1に設けられたホール素子2と、ホール素子1上に設けられた軟磁性薄膜6が、少なくともホウ素を含有している。また、半導体基板1上で、かつホール素子2上に設けられた有機絶縁膜4と、有機絶縁膜4と軟磁性薄膜6との間に設けられた金属導電層5とを備え、軟磁性薄膜6が、金属導電層5上で少なくとも1個以上のホール素子2の感磁部を覆うように配置されている。形成された軟磁性薄膜6の総重量を100重量%としたときの鉄含有量が15〜30重量%、ホウ素含有量が0.15〜0.35量%、電解めっき液を安定化するpH緩衝剤に起因する炭素を0.4〜0.8重量%、残部がニッケルである。

(もっと読む)

磁気センサ

【課題】感磁部と磁気感度および抵抗の調整を可能とするトリミング部とを備えた磁気センサを提供すること。

【解決手段】磁気センサは、基板26に設けられた化合物半導体からなる十字形状パターンの感磁部21を備え、入力端子21a,21bと出力端子21c,21dの少なくとも一方の端子21a,21dに、化合物半導体を有するトリミング部23a,23bが接続電極24を介して直列接続されている。ウェハプロービングを行いながら、接続電極24を介して感磁部21に直列接続された入力端子側のトリミング部23aを、レーザートリミングすることにより、定電圧駆動における磁気感度の調整を可能とし、同様に出力端子側のトリミング部23bをトリミングすることにより出力抵抗の調整を可能にした。

(もっと読む)

集積化センサの配列

【課題】減少された大きさ、改善された精度、および/または改善されたダイナミックレンジを有する外部磁界センサ等を提供することを目的とする。

【解決手段】 集積回路(10)は、磁界感知素子(30)を支持する第1の基板(14)および他の磁界感知素子(20)を支持する第2の基板(26)を備えることができる。第1および第2の基板は、様々な構成で配列されてもよい。他の集積回路は、その表面に配置された第1の磁界感知素子および第2の異なる磁界感知素子を備えることができる。

(もっと読む)

複合半導体素子、その製造方法、磁気センサ及び画像形成装置

【課題】化合物半導体ウェハー素材を用いてホール素子などを作成するに当たり、無駄となる部分が多くコストの増加を招いていた。

【解決手段】 複合半導体素子が、基板(11)と、基板上(11)に備えられ有機材料を主材料とする平坦化層(14)と、例えばホール素子を構成する化合物半導体素子を含み平坦化層(14)上にボンディングされた半導体薄膜(12)を有する。化合物半導体薄膜(12)との電気的接続のための金属配線膜(23)をさらに備え、化合物半導体薄膜(12)と金属配線膜(23)との間に、より高い不純物濃度の化合物半導体層(17)を介在させても良い。

(もっと読む)

磁気センサ

【課題】ホールセンサ出力の、磁束密度に対する直線性を向上させる。

【解決手段】絶縁性基板または半絶縁性基板10上に形成された膜厚方向に電子移動度の分布を有する化合物半導体薄膜を用いた磁気センサにおいて、導電層20となる化合物半導体薄膜を、第一の半導体層21と第二の半導体層22と第三の半導体層23とをこの順に積層して構成し、前記第一の半導体層21が前記絶縁性基板または半絶縁性基板10に接するように配置し、前記第二の半導体層のキャリア移動度を、前記第一の半導体層及び前記第三の半導体層のキャリア移動度よりも高く、且つ前記第二の半導体層22の不純物濃度を、前記第一の半導体層21及び前記第三の半導体層23の不純物濃度よりも大きくする。

(もっと読む)

ホール素子

【課題】従来の位置検出装置では、第1のホール素子および第2のホール素子をそれぞれ別のチップ内に形成していた。従って、2チップを使用しているため、コストが高く、パッケージを小さくできないという問題があった。また、ダイボンドの位置ずれにより、前記第1のホール素子と前記第2のホール素子との間のギャップ精度が悪いという問題もあった。

【解決手段】本発明に係るホール素子では、前記第1のホール素子および前記第2のホール素子が1チップ内に形成される。また、適正なレイアウトによりチップサイズを縮小することができる。これにより、パッケージサイズを小さくすることができる。さらに、本発明に係るホール素子では、前記第1のホール素子および前記第2のホール素子がリソグラフィーにより同一チップに同時に形成されるので、前記第1のホール素子と前記第2のホール素子との間のギャップ精度を向上させることができる。

(もっと読む)

回転センサ

【課題】 回転角度の検出精度を高めながら小型化することができる回転センサを実現する。

【解決手段】 磁気抵抗素子R1〜R8が各磁気抵抗素子の出力信号間に位相差が出るように配置された磁気抵抗素子領域E1と、ホール素子H1,H2が各ホール素子の出力信号間に位相差が出るように配置されたホール素子領域E2とを有し、かつ、磁気抵抗素子領域およびホール素子領域の少なくとも一部同士が重ねられたセンサチップ5と、各ホール素子の各出力レベルと閾値レベルとの比較結果を出す比較部53と、各磁気抵抗素子の各出力信号を用いて相対回転角度θに対応する演算角度φを演算する角度演算部60と、その演算された角度と閾値角度とを比較し、その比較結果と比較部53の比較結果とを用い、相対回転角度に対応する信号を出力する出力部70とを備える。

(もっと読む)

回転センサ

【課題】 磁気発生部の相対回転角度の演算時間を短縮することができる回転センサを実現する。

【解決手段】角度演算部60はAMRセンサM1,M2から出力される信号を用い永久磁石2に対する相対回転角度θと演算により求めた演算角度φとの偏差が所定値に収束するようにフィードバック制御を行って相対回転角度θを演算する。初期値決定部53はホール素子H1,H2から出力された各検出信号の各信号レベルと閾値との各比較結果を用い相対回転角度θの初期値θ0が含まれる角度範囲を判定し、その判定した角度範囲の中で発生し得る相対回転角度の初期値と前記演算角度の初期値との差の絶対値が90°未満となるように演算角度の初期値を決定する。初期値決定部は永久磁石2が相対回転を開始する前にのみ演算角度φの初期値φ0を決定し角度演算部60はその決定された演算角度φの初期値φ0を用いてフィードバック制御を開始し、相対回転角度θを演算する。

(もっと読む)

GaAsホール素子

【課題】オフセット電圧の変動の小さいGaAsホール素子を提供すること。

【解決手段】n−GaAs層からなる感磁部22を、n−GaAs層22よりもバンドギャップの大きいAlGaAsからなる第1及び第2の絶縁層23a,23bで挟み、かつ、n−GaAs層22のキャリア濃度を5×1016/cm3以上、1×1018/cm3以下とすることにより、n−GaAs層22の下部から側面への電子の移動、及び側面での電子のトラップの影響を抑制することができる。

(もっと読む)

電流センサの製造方法

【課題】少ない製造工程数でS/N比が良く、資源に無駄を生じない低コストの電流センサを提供する。

【解決手段】InSb等の単結晶基板1とフェライト基板2とを接着し、単結晶基板1の非接着面を厚みが5〜10[μm]になるまで研磨する。この研磨面に、ホール素子パターンとしての複数の感磁性部1aを形成した後、フェライト基板2ごと切断して複数のホール素子チップ5を分割形成する。次に、接着剤7を介しホール素子チップ5をフェライトコア6の段差部6aに接着し、感磁性部1aに電極8及び保護膜9を形成する。フェライトコア6及び感磁性部1aを含む磁気回路を他のLコア、Iコアを組み付けて構成し、電流センサを製造する。

(もっと読む)

ホール素子

【課題】感磁面に対して平行な磁場を検出するホール素子において、磁気増幅効果を損なうことなく、小型化および薄型化を実現すること。

【解決手段】ホール素子100は、感磁面が化合物半導体で構成されたホール素子部110と、ホール素子部110の感磁面111と平行に配置された磁気収束板120とを備える。感磁面111の幅をW、磁気収束板120の幅をA、長さをB、厚みをDとする。感磁面111と磁気収束板120との間のギャップをCとする。磁気増幅率は長さBに比例しており、アスペクト比B/Aが3以上となる形状では磁気増幅率が1.5倍を超え、更にBを300μmとしたB/A=5の場合には磁気増幅率が3倍に達する。また、A/W<3を満足するよう磁気収束板120の幅Aを狭めてゆくと、磁束の集中する磁気収束板120の側面部が感磁面111に近づくため、磁気増幅率の増加が著しい。

(もっと読む)

ホール素子

【課題】高感度で消費電力が低く、かつ、温度特性にも優れたホール素子の提供すること。

【解決手段】InX1Ga1−X1AsY1Sb1−Y1(0≦X1≦1、0≦Y1≦1)からなる活性層の上下に、この活性層より大きな禁制帯幅を有する化合物半導体層を配置した半導体薄膜と、金属電極層を形成する領域の上部の化合物半導体層をエッチングして活性層が露出された半導体薄膜をすべて覆うように設けられた第一保護層と、パターンニングした第一保護層をマスクとして用いて半導体薄膜の感磁部及び電極接触部以外をエッチングして露出した基板と半導体薄膜の側面及び第一保護層を被覆した第二保護層と、この第二保護層と第一保護層とをエッチングして露出された活性層のみに接触する金属電極層とを備えた。

(もっと読む)

半導体装置

【課題】ダイシングストリートにGaAsが露出している場合、結果ダイシング時に素子のチッピング、電極や磁性体の剥離、溶解したGaAsによる電極接合部の汚染が発生し、さらにGaAs基板裏面もエッチングされるためGaAsの溶解による電極接合部の汚染の課題がある。

【解決手段】本発明は、ホール素子が設けられたGaAs基板と、GaAs基板上に設けられた磁気増幅機能を有する磁性体とを備える磁気デバイスにおいて、上記ホール素子上に絶縁層と、上記絶縁層上にTi系金属層と、上記Ti系金属層の上にCu系金属層とを有し、ダイシングストリート上を少なくとも無機絶縁材料乃至有機絶縁材料もしくはその両方でカバーさせGaAsを露出させず、またさらにGaAs基板裏面にも有機絶縁膜でカバーすることにより本課題を解決した。

(もっと読む)

半導体磁気センサー

【課題】従来よりも高感度かつ小面積の半導体磁気センサーを低コストで提供すること。

【解決手段】半導体基板上に化合物半導体から構成されたエピタキシャル成長層を分割することにより形成された3つのメサ領域が形成されている。メサ10Cはホール素子部100として使用される。メサ10A及びメサ10Bは、それぞれホール素子部100からの出力を増幅するための電界効果トランジスタ部200A、200Bとして使用される。メサ10Cとメサ10B、メサ10Cとメサ10Aはそれぞれ隣接して設けられているが、これらのメサ同士はエッチングにより分断されることによって絶縁されている。電圧検出用電極20A及び20Bは、それぞれ電界効果トランジスタ部200A及び200Bのゲート電極40A、40Bに直接接続されている。

(もっと読む)

半導体装置及びその製造方法

【課題】低保磁力と低い残留磁束密度をもつ軟磁性膜を備え、この軟磁性薄膜で磁気収束する半導体装置及びその製造方法を提供すること。

【解決手段】半導体基板1に設けられたホール素子2と、このホール素子1上に設けられた軟磁性薄膜6とを備え、軟磁性薄膜6が、少なくともホウ素を含有している。半導体基板1上で、かつホール素子2上に設けられた有機絶縁膜4と、この有機絶縁膜4と軟磁性薄膜6との間に設けられた金属導電層5とを備え、軟磁性薄膜6が、金属導電層5上で少なくとも1個以上のホール素子2の感磁部を覆うように配置されている。

(もっと読む)

電流センサの製造方法

【課題】ホール素子チップの厚さを均一化し、感度特性が均一で歩留まりに優れた電流センサを提供する。

【解決手段】InSb単結晶基板10の一面に感磁性部11を形成し、支持基板12と単結晶基板10との少なくとも一方に仮接着剤13を均一の厚さに成膜して支持基板12と単結晶基板10とを接着する。単結晶基板10の裏面を感磁性部11が露出するまで研磨し、本接着剤14を均一の厚さに成膜し、個々の感磁性部11を支持基板12ごと切断して多数のホール素子チップ15を分割形成する。本接着剤14を介してチップ15をフェライトコア20に接着し、チップ15から支持基板12を除去し、感磁性部11に電極22を形成して感磁性部11を覆うように保護膜23を形成する。フェライトコア20及び感磁性部11を含む磁気回路を構成するように他のLコア、Iコアを組み付けて電流センサを製造する。

(もっと読む)

半導体素子

【課題】特性劣化が小さい半導体素子を提供する。

【解決手段】本発明に係る半導体素子は、基板上に形成されたメサ構造を有する化合物半導体膜1と、化合物半導体膜1上に形成された短絡電極2と、外部との電気的接続を行うための取り出し電極3とを備える。短絡電極2および取り出し電極3は、化合物半導体膜1のメサ部分に接合する。取り出し電極3と化合物半導体膜1のメサ構造の長辺端部との接合面は、(111)面、(1−1−1)面、(−11−1)面、および(−1−11)面に平行な面のうち、少なくとも1つの面に対して−15°〜+15°の範囲であり、(11−1)面、(1−11)面、(−111)面、および(−1−1−1)面に平行な面に対して−15°〜+15°の範囲では、接合部が無いように形成されたことを特徴とする。

(もっと読む)

1 - 20 / 45

[ Back to top ]