Fターム[5F092BC07]の内容

Fターム[5F092BC07]に分類される特許

201 - 220 / 942

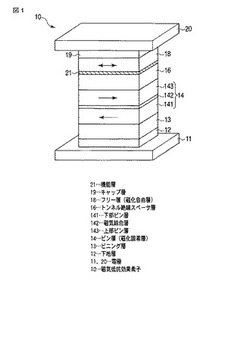

磁気抵抗効果素子及び磁気記録再生装置

【課題】本発明は、MR変化率の高い磁気抵抗効果素子及びそれを用いた磁気記録再生装置を提供する。

【解決手段】キャップ層と、磁化固着層と、前記キャップ層と前記磁化固着層との間に設けられた磁化自由層と、前記磁化固着層と前記磁化自由層との間に設けられたトンネル絶縁スペーサ層と、前記磁化固着層中、前記磁化固着層と前記トンネル絶縁スペーサ層との間、前記トンネル絶縁スペーサ層と前記磁化自由層との間、前記磁化自由層中、及び前記磁化自由層と前記キャップ層との間の何れかに設けられ、Zn、In、Sn、及びCdから選択される少なくとも1つの元素、並びにFe、Co、及びNiから選択される少なくとも1つの元素を含む酸化物を有する機能層と、を備えた積層体と、前記積層体の膜面に垂直に電流を流すための一対の電極と、を備えたことを特徴とする磁気抵抗効果素子。

(もっと読む)

半導体装置および半導体装置アセンブリ

【課題】外部からの磁場を遮蔽する磁気シールド効果が高い半導体装置を提供する。

【解決手段】半導体基板SUBの主表面上に形成されたスイッチング素子TRを覆うように形成された層間絶縁膜III1と、平板状の引出配線LELと、引出配線LELとスイッチング素子TRとを接続する接続配線ICLと、磁化の向きが可変とされた磁化自由層MFLを含み、引出配線LEL上に形成された磁気抵抗素子TMRとを備える。磁化自由層MFLの磁化状態を変化させることが可能な配線DLと配線BLとを備えている。磁気抵抗素子TMRが複数並んだメモリセル領域において、磁気抵抗素子TMRの上部に配置された第1の高透磁率膜CLAD2が、上記メモリセル領域から、メモリセル領域以外の領域である周辺領域にまで延在している。

(もっと読む)

装置、方法および磁気センサ

【課題】磁気記憶装置において、精度のよい面積解像度に対応する低減された作動幅を有する変換素子を提供する。

【解決手段】磁気に反応する第1の面積範囲を有する自由層132と、第1の面積範囲よりも広い第2の面積範囲を有し、自由層に隣接する合成反強磁性(SAF)層134を設ける。

(もっと読む)

磁気ヘッド、磁気ヘッドアセンブリおよび磁気記録再生装置

【課題】MR比の低下や再生分解能の劣化を発生させることなく、スピントランスファトルクに起因する磁気ノイズを抑制する。

【解決手段】本発明は、第1磁気シールド72aと、第2磁気シールド72bと、第1磁気シールド72aと、第2磁気シールド72bと、の間に設けられ、外部磁界に応じて磁化方向が変化する第1磁化自由層103を含む磁気抵抗効果膜71と、磁気抵抗効果膜71と、第1磁気シールド72aと、の間に設けられ、第1磁気シールド72aよりも飽和磁束密度が高い第3磁気シールド72cと、を有する再生ヘッド部70を備えた磁気ヘッド110である。

(もっと読む)

Co−Feバッファ層を備える膜面垂直通電(CPP)読出しセンサ

【課題】 Co−Feバッファ層を備える膜面垂直通電(CPP)読出しセンサを提供する。

【解決手段】 ピン止めおよび磁気抵抗特性を改善するために、Co−Feバッファ層を備える膜面垂直通電(CPP)読出しセンサが、提案される。この読出しセンサは、それぞれキーパ層構造の下側部分と上側部分にある第1と第2のCo−Feバッファ層と、それぞれ基準層構造の下側部分と上側部分にある第3と第4のCo−Feバッファ層と、検知層構造の下側部分にある第5のCo−Feバッファ層を含む。第1のバッファ層は、ピン止め層に隣接して、双方向異方性ピン止め特性を改善するための特定の組成を有する。第2と第3のバッファ層は、反平行結合層に隣接し、双方向異方性ピン止め特性を改善するための特別な組成を有する。第4と第5のバッファ層は、バリアおよびスペーサ層に隣接し、磁気抵抗特性を改善するための特定の組成を有する。

(もっと読む)

膜面垂直通電(CPP)読み取りセンサの縦バイアス積層構造

【課題】膜面垂直通電(CPP)読み取りセンサの縦バイアス積層構造を提供する。

【解決手段】CPP読み取りセンサの検知層構造を安定化させるための、改良された縦バイアス積層構造を有する読み取りヘッドが提供される。縦バイアス積層構造は、2つの側部領域の各々において、絶縁層によってCPP読み取りセンサから分離され、絶縁層とCPP読み取りセンサとともに、読み取りヘッド内の上側および下側強磁性シールドの間に挟まれる。本発明の好ましい実施形態において、縦バイアス積層構造は主として、Fe−Pt縦バイアス層を含み、シード層を持たないため、絶縁層のみの厚さで、Fe−Pt縦バイアス層とCPP読み取りセンサの間の間隔が決定される。シード層を持たないFe−Pt縦バイアス層は、アニーリング後に良好な膜面内の硬磁性を呈し、間隔が狭いため、この安定化方式は有効である。

(もっと読む)

磁気記憶素子および磁気記憶装置

【課題】半選択状態になったデータの誤反転を抑制して信頼性の高い書き込み動作を行うことができる磁気記憶素子およびこれを用いた磁気記憶装置を提供する。

【解決手段】磁化容易軸91とそれに交差する磁化困難軸92とを有する記録層3と、磁化容易軸91の方向と交差する方向に磁界を形成するライト線WTと、記録層3の配置位置において磁化困難軸92の方向と交差する方向に磁界を形成するビット線BLとを備え、記録層3は、ライト線WTとビット線BLとの間に挟まれるように配置されており、ライト線WTおよびビット線BLと記録層3とが積層された積層方向からみた記録層3の平面形状は、積層方向からみてライト線WTが延びる方向に沿うライト線WTの仮想の第1の中心線AWに対して一方側に位置する一方の部分と他方側に位置する他方の部分とを有し、積層方向からみた一方の部分の面積S2が他方の部分の面積S1の1/3以下である。

(もっと読む)

磁気メモリ

【課題】書き込み電流を低減する。

【解決手段】本発明の例に関わる磁気メモリは、磁化が可変な磁性層11と、磁化が固定された磁性層13と、中間層12と、膜面に対して平行方向の磁化が可変な磁性層15とを有する磁気抵抗効果素子1と、絶縁膜を介して磁気抵抗効果素子1の側面上に設けられ、磁性層15の端部から発生する磁場を収束する磁性層16と、を有する。

(もっと読む)

磁気抵抗効果素子、磁気ヘッドアセンブリ、及び磁気記録再生装置

【課題】 大きなMR変化率を有する磁気抵抗効果素子、磁気ヘッドアセンブリ、及び磁気記録再生装置を提供する。

【解決手段】 磁化固着層5と、磁化自由層7と、磁化固着層5と磁化自由層7との間に設けられた非磁性層6と、磁化自由層7の非磁性層6が設けられた側とは反対の側に設けられたAuを含む第1の金属層4と、第1の金属層4の磁化自由層7が設けられた側とは反対の側に設けられたCuNi合金を含む第2の金属層3と第2の金属層3の第1の金属層4が設けられた側とは反対の側に設けられた第1の電極2と、磁化固着層5の非磁性層6が設けられた側とは反対の側に設けられた第2の電極8とを備え、磁化固着層5及び磁化自由層7の一方がハーフメタルを含み、第1の電極2から第2の電極8に向かって電流が流れることを特徴とする。

(もっと読む)

磁気抵抗効果素子およびその製造方法ならびに磁気メモリ

【課題】高いMR比を有する磁気抵抗効果素子およびその製造方法ならびに磁気メモリを提供することを可能にする。

【解決手段】第1磁性層14と、第1磁性層上に設けられたトンネルバリア層16と、トンネルバリア層上に設けられCoFeを含む第2磁性層18aと、第2磁性層上に設けられ、B、Ta、Zr、Al、Ceのうちの少なくとも1つの元素および窒素を含む非磁性層19と、を備えている。

(もっと読む)

磁気トンネル接合記憶素子の製造

スピンメモリおよびスピントランジスタ

【課題】単方向電流で書き込みをすることを可能にするとともに回路面積が増大するのを防止することを可能にする。

【解決手段】第1強磁性層21、第1非磁性層23、第2強磁性層25、第2非磁性層27、および第3強磁性層29がこの順序または逆の順序で積層された積層構造を有し第3強磁性層と第2強磁性層とが第2非磁性層を介して反強磁性的な交換結合をする強磁性積層膜20を含むメモリセル10を備え、第1強磁性層から第3強磁性層に向かう単一方向の電流を強磁性積層膜に流して、電流の大きさに応じて第1強磁性層に異なる磁化状態の書き込みを行うとともに第1強磁性層からの読み出しを行なう。

(もっと読む)

半導体集積回路

【課題】セル面積が小さい不揮発性SRAMセルを提案する。

【解決手段】本開示に係わる半導体集積回路は、第1及び第2のインバーターINV1,INV2と、ゲートにワード線WLが接続され、ソースに第1のビット線BLが接続され、ドレインに第2のインバーターINV2の入力端子が接続される第1のトランジスタM5と、ゲートにワード線WLが接続され、ソースに第2のビット線bBLが接続され、ドレインに第1のインバーターINV1の入力端子が接続される第2のトランジスタM6と、第1の端子に第1のトランジスタM5のドレインが接続され、第2の端子に第1のインバーターINV1の出力端子が接続される第1の可変抵抗素子R1と、第1の端子に第2のトランジスタINV2のドレインが接続され、第2の端子に第2のインバーターINV2の出力端子が接続される第2の可変抵抗素子R2とを備える。

(もっと読む)

マイクロ波素子

【課題】検波出力や発振出力等の点で、著しい特性向上は困難である。

【解決手段】マイクロ波素子100は、面内磁化膜の磁化自由層103と、面内磁化膜の磁化固定層105と、磁化自由層103と磁化固定層105の間に設けられたトンネルバリア層104とを有する磁気抵抗素子を用いたマイクロ波素子において、磁気抵抗素子の膜面直方向の軸から3°以上30°以下の外部磁界を印加する外部磁界印加機構302と、磁化固定層105の膜面直方向の反磁界に対する磁化自由層103の膜面直方向の反磁界の比が0.5以下であることを特徴とする。

(もっと読む)

スピンバルブ素子および記憶装置

【課題】 磁化反転のための電流を低減し、動作を高速にする。

【解決手段】 1層の絶縁体層または非磁性層からなる中間層(24、51)と、中間層を挟む1対の強磁性層(23、25)とを備え、1対の強磁性層の強磁性層の保磁力が互いに異なるスピンバルブ素子またはそのスピンバルブ素子を用いる記憶装置。1対の強磁性層の強磁性層の磁化容易軸(10、12)の方向を互いに異なるようにする。また、好適には、磁化容易軸の間の角度を一定の範囲に設定する。

(もっと読む)

磁気抵抗記憶素子及び磁気ランダムアクセスメモリ

【課題】書込み電流を低減しつつ、信頼性の高い磁気抵抗記憶素子を提供する。

【解決手段】磁気抵抗記憶素子は、読出し構造体と、読み出し構造体の近傍に設けられた書込み構造体とを具備する。読み出し構造体は、磁化方向が変化する第1のフリー層と、磁化方向が固定された磁化固定層と、第1のフリー層と磁化固定層との間に設けられたトンネル絶縁層とを備える。書込み構造体は、磁化方向が変化する第2のフリー層を備える。第2のフリー層は、第2のフリー層の膜の上面に設けられ、第1方向に磁化が固定された第1の磁化固定領域と、膜の下面に設けられ、第2方向に磁化方向が固定された第2の磁化固定領域とを含む。膜の膜面方向に磁壁が存在する。第1のフリー層と第2のフリー層とは静磁結合している。

(もっと読む)

基板処理装置および半導体装置の製造方法

【課題】メンテナンス頻度を低減でき、適切なメンテナンス時期を見極めることができる基板処理装置を提供する。

【解決手段】基板処理装置10は、イオンを発生させるイオン源40と、イオン源40からのイオンビーム45を受けるターゲット36と、第一真空容器11内に収容されてターゲット36からのスパッタ粒子46を受けるウエハ1を保持するウエハホルダ18と、第二真空容器22へのスパッタ粒子46の付着を抑制する防着板51と、防着板51へ付着するスパッタ粒子46の付着量を予測する付着量予測部61とを備える。

(もっと読む)

磁気抵抗効果素子の製造方法、磁気抵抗効果素子、磁気ヘッドアセンブリ及び磁気記録再生装置

【課題】MR変化率を向上した磁気抵抗効果素子の製造方法、磁気抵抗効果素子、磁気ヘッドアセンブリ及び磁気記録再生装置を提供する。

【解決手段】強磁性体を含む第1磁性層と、強磁性体を含む第2磁性層と、第1磁性層と第2磁性層との間に設けられ、絶縁層161と、絶縁層を貫通する導電部162と、を含む中間層16と、を有する磁気抵抗効果素子の製造方法が提供される。本製造方法は、絶縁層と、絶縁層を貫通する導電部16pと、を含む構造体を形成する工程(ステップS110)と、構造体に、希ガスを含むイオン及びプラズマの少なくともいずれかの照射を行う第1処理工程(ステップS120)と、第1処理工程が施された構造体に対して、酸素及び窒素の少なくともいずれかのガスへの曝露、イオンビーム照射及びプラズマ照射の少なくともいずれかを行う第2処理工程(ステップS130)と、を備える。

(もっと読む)

磁気記憶装置

【課題】配線に流れる電流によって発生した誘導磁界による磁気記憶素子の誤作動を低減しつつ、大容量化および高集積化を図ることができる磁気記憶装置を提供する。

【解決手段】複数の磁気記憶素子3とビット線4と複数のトランジスタ2と磁気シールド用磁性膜22とを備えている。磁気記憶素子3は、磁化方向が一定である固着層19、磁化方向が可変である記憶層21、および、固着層19と記憶層21との間に配置されたトンネル絶縁膜20を有し、スピン偏極した電子により記憶層21の磁化方向を反転させる。ビット線4は、複数の磁気記憶素子3のそれぞれが互いに間隔を置いて接続され、複数の磁気記憶素子3に対向して配置されている。トランジスタ2は、複数の磁気記憶素子3の内の対応した磁気記憶素子3を経由してビット線4に電気的に接続されている。磁気シールド用磁性膜22は、ビット線4と磁気記憶素子3との間に配置されている。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】磁気抵抗素子への不純物の侵入や応力の負荷を抑制し、低い駆動電力で高精度に作動する半導体装置およびその製造方法を提供する。

【解決手段】本発明の半導体装置は、主表面を有する半導体基板SUBと、半導体基板SUBの主表面上に位置する磁気抵抗素子MRDとを備えている。その他、保護層IIIと、配線BLと、第1上部電極UEL1と、第2上部電極UEL2とを備えている。保護層IIIは、磁気抵抗素子MRDの側面を覆うように配置されている。配線BLは、上記磁気抵抗素子MRDの上部に位置する。第1上部電極UEL1は、上記磁気抵抗素子MRD上に、平面視における大きさが磁気抵抗素子MRDと実質的に同じであるものが配置されている。第2上部電極UEL2は、上記第1上部電極UEL1上にて、上記第1上部電極UEL1と電気的に接続されており、平面視における大きさが第1上部電極UEL1より大きい。

(もっと読む)

201 - 220 / 942

[ Back to top ]