Fターム[5F092EA06]の内容

ホール/MR素子 (37,442) | 集積化レイアウト (372) | 1チップ上に他の素子と集積化したもの (234) | トランジスタ (74)

Fターム[5F092EA06]に分類される特許

1 - 20 / 74

電流検知装置、電流検知素子および電流検知方法

【課題】より広い電流レンジの測定を可能とする。

【解決手段】電流を検知するための素子として、磁界の強度に応じて抵抗値が変化する磁気抵抗効果を利用した磁気抵抗素子を用いる。磁気抵抗素子の近傍に配置した配線に測定対象の電流が流れた際に発生する磁界に応じた当該磁気抵抗素子の抵抗に基づき、当該測定対象電流の電流値を測定する。また、磁気抵抗素子を、IV特性の直線領域において純抵抗として用いて、当該磁気抵抗素子に測定対象電流を直接流して電流値の測定を行う。これらの、磁気抵抗素子の磁気抵抗効果を利用した電流測定と、磁気抵抗素子を純抵抗として用いた電流測定とを、測定対象電流の電流値に応じて切り替える。

(もっと読む)

アナログ/デジタル変換器

【課題】変換精度が高いアナログ/デジタル変換器を提供する。

【解決手段】アナログ/デジタル変換器は、電圧生成部と複数の比較器とを備える。電圧生成部は、基準電圧を、複数の抵抗器で分圧して複数の比較用電圧を生成する。各比較器は、複数の比較用電圧のうちの何れかの比較用電圧とアナログの入力電圧との比較結果に応じたデジタル信号を出力する。各比較器は、2つの入力の電位差を検出する差動対回路を含む。差動対回路は、第1回路部50と第2回路部60とを有する。第1回路部は、第1入力トランジスタ51と、第1入力トランジスタと直列に接続される抵抗器Rrefとを含む。第2回路部は、第1入力トランジスタと差動対を形成する第2入力トランジスタ61と、第2入力トランジスタと直列に接続される可変抵抗器Rvとを含む。可変抵抗器は、直列に接続されるとともに、制御信号に応じて各々の抵抗値が可変に設定される複数の可変抵抗素子を含む。

(もっと読む)

磁界検出方法

【課題】精度の高い磁界検出方法を提供する。

【解決手段】

トンネル磁気抵抗効果素子10を用いて外部磁界を検出する磁界検出方法が提供される。磁界検出方法は、トンネル磁気抵抗効果素子10の自由層15の磁化方向を変化させるバイアス磁界Hbと外部磁界Hexとを同時に、もしくはバイアス磁界Hbと外部磁界Hexとを個別にトンネル磁気抵抗効果素子10に印加したときの電気特性を測定するステップと、バイアス磁界Hbおよび外部磁界Hexに応じて測定されたトンネル磁気抵抗効果素子10の電気特性に基づいて外部磁界を算出するステップとを含む。

(もっと読む)

半導体装置の製造方法

【課題】FinFETの特性が均一な半導体装置の製造方法を提供する。

【解決手段】実施形態に係る半導体装置の製造方法は、半導体基板の上層部分に凹部を形成する工程と、前記凹部内に犠牲材を配置する工程と、前記半導体基板及び前記犠牲材を選択的に除去することにより、一方向に延び、周期的に配列された複数本のフィンを形成する工程と、前記フィン間の空間の下部に素子分離絶縁膜を形成する工程と、前記犠牲材を除去する工程と、前記フィンの露出面上にゲート絶縁膜を形成する工程と、前記素子分離絶縁膜上に、前記フィンを跨ぐように、前記一方向に対して交差した方向に延びるゲート電極を形成する工程と、を備える。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】基板の反射率に依存せず、アライメントマークの識別性を確保することができる半導体装置及び半導体装置の製造方法を提供する。

【解決手段】半導体装置1は、シリコン基板24と、シリコン基板24上に少なくともNiCoパターン31とアルミ電極30とを含んで形成される回路部3と、シリコン基板24上に回路部3のNiCoパターン31と同工程において形成される低反射パターンとしてのNiCoパターン22と、NiCoパターン22上に形成され、回路部3のアルミ電極30と同工程において形成される高反射パターンとしてのアルミパターン20とを有する。

(もっと読む)

ホール素子及びホール素子を備えた半導体装置

【課題】ウェル層と基板の間の空乏層幅を抑制し、かつCMOSトランジスタとの混載が可能なホール素子を含む半導体装置を提供することを目的とする。

【解決手段】P型基板101に設けられたNウェル層103と、Nウェル層103の上面においてX方向に沿った電流を流す電流入力端子110、111と、前Nウェル層103の上面においてX方向と直交するY方向に沿った磁界を発生する電圧出力端子112、113と、を備える半導体装置において、Nウェル層103の底面とP型基板101との間に、導電型がN型であって、かつNウェル層103よりも不純物濃度の高い空乏層幅抑制用N+層120を設ける。

(もっと読む)

ホール素子及びその製造方法、半導体装置

【課題】コストの増大を抑えつつ、ホール素子のオフセット電圧Voを低減することができるようにしたホール素子及びその製造方法と、半導体装置を提供する。

【解決手段】半導体基板1に設けられた第1のN型拡散領域10と、半導体基板1に設けられ、第1のN型拡散領域10に電気的に接合された複数の第2のN型拡散領域20と、半導体基板1に設けられ、複数の第2のN型拡散領域20の各々の間を電気的に分離するSTI領域30と、を有する。第1のN型拡散領域10は感磁部であり、複数の第2のN型拡散領域20の各々は感磁部に対する入出力端子部である。複数の第2のN型拡散領域20の各々におけるN型の不純物濃度は、STI領域30の底部30bを基点に深さ方向で0μm以上、0.2μm以下の範囲内で、5×1017個/cm3以上、3×1019個/cm3以下である。

(もっと読む)

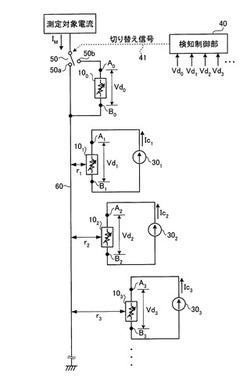

電流センサ

【課題】簡便な構成で電気配線に流れる電流を広い電流レンジで検知する電流センサを提供する。

【解決手段】測定対象Aに接続される電気配線wa,wb1,wc1と、抵抗値が一定比率で増加する直線部分と抵抗値が飽和する飽和部分とからなる磁気抵抗特性を有し、それぞれが前記電気配線から異なる距離d1,d2,d3で離間して配置される磁気抵抗素子11a,11b,11cと、磁気抵抗素子11a,11b,11cそれぞれにセンス電流を流すセンス電流部12と、磁気抵抗素子11a,11b,11cにおけるセンス電流値の変化から磁気抵抗特性の前記直線部分から飽和部分へ移行する抵抗値の飽和点に到達したことを検知し、前記電流配線に流れる電流がある規定値に到達したとして出力する検知手段13と、を備え、検知手段13は、前記電流配線に流れる電流について磁気抵抗素子11a,11b,11cごとに異なる規定値への到達を検知する。

(もっと読む)

スピン流回路

【課題】スピンエレクトロニクスを用いて擬似的にダイオード特性を有するスピン流回路を提供する。

【解決手段】 このスピン流回路は、半導体層10C内に形成された主導電領域3Aと、半導体層内に形成され主導電領域から分岐した第1副導電領域3Bと、半導体層内に形成され主導電領域から分岐した第2副導電領域3Cと、主導電領域3A上に形成され主導電領域内にトンネル障壁層5を介して電子を注入する主強磁性体1と、主導電領域3A上に形成された収集電極4と、第1副導電領域3B上に形成され、主強磁性体1と同じ方向に磁化方向が固定された第1副強磁性体2’と、第2副導電領域3C上に形成され、第1副強磁性体2’とは磁化方向が異なる方向に固定された第2副強磁性体2”と、第1副強磁性体2’と第2副強磁性体2”との間の電圧を検出する電圧検出回路とを備えている。

(もっと読む)

半導体装置

【課題】チップ面積を増大させることなく電流検出精度を向上することができる半導体装置を得る。

【解決手段】半導体素子1はエミッタ電極7を有する。引き出し線10は、エミッタ電極7に電気的に接続され、エミッタ電極7の上方を通ってサイドに引き出される。電流センサー11は、磁気抵抗素子12を有し、引き出し線10に流れる電流を検出する。磁気抵抗素子12は、エミッタ電極7上、かつ引き出し線10の下方に配置されている。磁気抵抗素子12の抵抗値は、電流により発生した磁界に対してリニアに変化する。

(もっと読む)

集積化センサの配列

【課題】減少された大きさ、改善された精度、および/または改善されたダイナミックレンジを有する外部磁界センサ等を提供することを目的とする。

【解決手段】 集積回路(10)は、磁界感知素子(30)を支持する第1の基板(14)および他の磁界感知素子(20)を支持する第2の基板(26)を備えることができる。第1および第2の基板は、様々な構成で配列されてもよい。他の集積回路は、その表面に配置された第1の磁界感知素子および第2の異なる磁界感知素子を備えることができる。

(もっと読む)

半導体磁気センサ及びそれを用いた磁性体検出装置

【課題】ノイズの影響が低減され、かつ、増幅歪みの少ない半導体磁気センサ及びそれを用いた磁性体検出装置を提供すること。

【解決手段】直列接続された第1の半導体磁気抵抗素子11及び第2の半導体磁気抵抗素子12と、第1の半導体磁気抵抗素子11及び第2の半導体磁気抵抗素子12の接続ノードにゲート電極が接続された電界効果トランジスタ10とを備えている。電界効果トランジスタ10のゲート電極の幅を第1の半導体磁気抵抗素子11及び第2の半導体磁気抵抗素子12の各中心点を結んだ直線に投影した時の長さが、第1の半導体磁気抵抗素子11及び第2の半導体磁気抵抗素子12の各中心点の直線距離の略偶数倍であるように構成されている。

(もっと読む)

アッド‐オン層形成方法

【課題】多くの半導体装置に必要な低温処理と両立しない高温操作を必要とするような欠点がない、堆積可能なアッド‐オン層形成方法を提供することを目的とする。

【解決手段】堆積可能なアッド‐オン層形成方法であって、第一半導体基板の取り外し層の形成、取り外し層の上の第一半導体基板に多くのドーピング領域の形成、ここで多くのドーピング層の形成は、第一電導型を有するように、ドーピングされ、取り外し層の上の第一半導体基板の第一ドーピング層の形成、第一電導型に対する第二電導型を有するようにドーピングされ、第一ドーピング層の上の第一半導体基板に最低中間ドーピング層の形成、及び中間ドーピング層上の第一半導体基板に最低第三ドーピング層の形成からなり、第三ドーピング層上に第一の電導性ブランケット層の形成、第一電導ブランケット層上に第二の電導性ブランケット層の形成、及び第二電導性ブランケット層が第二半導体基板の対応する電導性上部層と接触するように、第一半導体基板を第二半導体基板への取り付け、からなる。

(もっと読む)

磁気レベルシフタ

【課題】多チャンネル化しても形成面積の増大を抑えることができる磁気レベルシフタを提供する。

【解決手段】レベルシフタは、入力信号が印加される磁界発生用配線112と、磁界発生用配線112が発生した磁界に対応した値をとる検出信号を出力する検出用磁気抵抗効果素子11と、一定の値をとる参照信号を出力する参照用磁気抵抗効果素子21,31を備える。当該レベルシフタは、検出信号と参照電圧の差に基づいて出力信号を生成する。

(もっと読む)

電流検知器を備えた半導体装置

【課題】磁気抵抗効果素子を用いて電流を検知するセンサを備えた半導体装置に関する。簡単な構成により、電流の検出を高精度に実現することを目的にする。

【解決手段】半導体回路が形成された基板と、基板に配設された第1の配線部材と、第1の配線部材に立設された垂直配線部材と、垂直配線部材に接続され第1の配線部材と平行に架設された第2の配線部材と、垂直配線部材に対向配置された第1の磁電変換素子と、垂直配線部材をはさんで第1の磁電変換素子と対向する第2の磁電変換素子と、第1の磁電変換素子と第2の磁電変換素子を直列に接続する第1の素子配線と、第1の素子配線の中点が入力される第1の増幅回路とを備えている。

(もっと読む)

回転−トルク転送磁気リード・アクセス・メモリのための選択デバイス

【課題】選択デバイスを改良した回転-トルク転送磁気リード・アクセス・メモリ(STT-MRAM)を提供する。

【解決手段】回転-トルク転送磁気リード・アクセス・メモリ(STT-MRAM)は、第1の導電性ラインと選択デバイスとの間で連結される磁気ビットを含む。選択デバイスは、少なくとも2つのトランジスタを含む。選択デバイスは、(a)少なくとも2つのトランジスタが第1の状態にあるとき、回転-トルク転送(STT)書き込みオペレーションのための磁気ビットを選択し、(b)少なくとも2つのトランジスタが第2の状態にあるとき、読み込みオペレーションのための磁気ビットを選択する、ように作動する。選択デバイスは、シリコン−オン−絶縁物(SOI)相補型金属酸化物半導体(CMOS)技術で実装される。

(もっと読む)

半導体装置

【課題】 従来、外付け抵抗の電圧降下から検出していたパワーN型MOSFETに流れる電流を、高感度のホール素子に発生するホール電圧VHにより検出する。

【解決手段】 アースラインに向かって配線されたソース配線層8の一部をN型層1に形成したトレンチ20内に配設する。これによりトレンチ20内に配設されたソース配線層8a近傍のN型層1に発生する磁束密度Bを高める。この高い磁束密度Bが発生しているトレンチ20内のソース配線層8a近傍のN型層1を横切るホール電流IH成分を増やし、ホール素子Hに発生するホール電圧VHを高くする。このように、高い磁束密度Bの発生領域にホール素子Hを配置することにより、パワーN型MOSFETのソース電流Iが数A程度でも大きなホール電圧VHを発生する。

(もっと読む)

半導体装置

【課題】従来、外付け抵抗の電圧降下から検出していたパワーN型MOSFETに流れる電流を、ホール素子に発生するホール電圧VHにより検出する。

【解決手段】アースラインに向かって配線されたソース配線層8の直下の絶縁膜7aを数10nm程度の厚さとする。これにより、ソース電流Iにより、ソース配線層8の直下領域または該ソース配線層8の両側面部のN型層1に発生する磁束密度Bを高くする。この高い磁束密度Bの発生領域にホール素子Hを配置することにより、パワーN型MOSFETのソース電流Iが数A程度でも大きなホール電圧VHを発生する。

(もっと読む)

半導体磁気センサー

【課題】従来よりも高感度かつ小面積の半導体磁気センサーを低コストで提供すること。

【解決手段】半導体基板上に化合物半導体から構成されたエピタキシャル成長層を分割することにより形成された3つのメサ領域が形成されている。メサ10Cはホール素子部100として使用される。メサ10A及びメサ10Bは、それぞれホール素子部100からの出力を増幅するための電界効果トランジスタ部200A、200Bとして使用される。メサ10Cとメサ10B、メサ10Cとメサ10Aはそれぞれ隣接して設けられているが、これらのメサ同士はエッチングにより分断されることによって絶縁されている。電圧検出用電極20A及び20Bは、それぞれ電界効果トランジスタ部200A及び200Bのゲート電極40A、40Bに直接接続されている。

(もっと読む)

半導体記憶装置

【課題】高速動作が可能なロジック回路とMRAMを備えた半導体記憶装置を提供する。

【解決手段】第1MOS型トランジスタのソース領域またはドレイン領域上の層間絶縁膜15A内にはコンタクトプラグ16Aが形成されている。ソース領域またはドレイン領域上の層間絶縁膜15A内にはコンタクトプラグ16Bが形成されている。コンタクトプラグ16A上には第1配線層M1Aが形成されている。磁気抵抗効果素子19は、コンタクトプラグ16B上の、第1配線層M1Aと半導体基板面から同じ高さの層に配置されている。第2MOS型トランジスタのソース領域またはドレイン領域上の層間絶縁膜15A内にはコンタクトプラグ16Cが形成されている。そして、第1配線層M1Bは、コンタクトプラグ16C上の、第1配線層M1A及び磁気抵抗効果素子19と半導体基板面から同じ高さの層に配置されている。

(もっと読む)

1 - 20 / 74

[ Back to top ]