Fターム[5F101BA33]の内容

不揮発性半導体メモリ (42,765) | 電荷蓄積機構 (9,664) | FG型 (6,485) | FG周囲絶縁膜 (3,604) | 薄膜化又は絶縁膜材料の特徴部位 (1,645)

Fターム[5F101BA33]の下位に属するFターム

Fターム[5F101BA33]に分類される特許

1 - 12 / 12

シリコン膜の形成方法及び半導体装置の製造方法

【課題】狭スペースへのシリコン膜の埋め込み性の向上を図る。

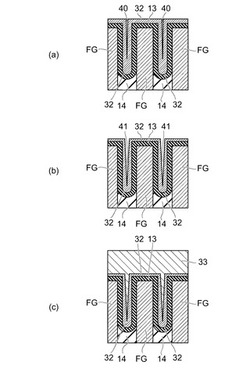

【解決手段】実施形態によれば、シリコン膜の形成方法は、凹部20の開口側からボトム側に向けてくぼんだくぼみ40を有するアンドープの第1のシリコン膜32を凹部20に形成する工程を含む。また、前記シリコン膜の形成方法は、凹部20内の第1のシリコン膜32の一部を塩素を含むガスを用いてエッチングし、第1のシリコン膜32に凹部20のボトム側よりも開口側で幅が広い隙間41を形成する工程を含む。また、前記シリコン膜の形成方法は、隙間41に面する第1のシリコン膜32の内壁に不純物を添加する工程を含む。また、前記シリコン膜の形成方法は、不純物の添加後、隙間41を埋める第2のシリコン膜33を形成する工程を含む。

(もっと読む)

半導体記憶装置およびその製造方法

【課題】微細化されても、コントロールゲートとフローティングゲートとの間のカップリング容量比を増大させることができる半導体記憶装置およびその製造方法を提供する。

【解決手段】半導体記憶装置は、半導体基板を備える。第1の絶縁膜は、半導体基板上に形成されている。フローティングゲートは、第1の絶縁膜上に設けられた第1のフローティングゲート部分、第1のフローティングゲート部分上に設けられた中間絶縁膜、および、中間絶縁膜上に設けられた第2のフローティングゲート部分を含み、電荷を蓄積可能に構成されている。第2の絶縁膜は、フローティングゲートの上面および側面に設けられている。コントロールゲートは、第2の絶縁膜を介してフローティングゲートの上面および側面に対向し、フローティングゲートの電圧を制御する。フローティングゲートの側面において中間絶縁膜が第1および第2のフローティングゲート部分に対して窪んでいる。

(もっと読む)

不揮発性半導体記憶装置及びその製造方法

【課題】動作信頼性を向上させる不揮発性半導体記憶装置及びその製造方法を提供する。

【解決手段】基板100上に形成された蓄積層105と蓄積層上に形成された制御ゲート電極107を備えた第1電極MTと、基板100上に形成された第2電極ST2及び第3電極ST2と、ゲート長方向に沿って対向する第2電極と第3電極ST2との側壁及び基板100上に形成された第2絶縁膜112と、第2、第3ゲート電極ST2間に埋設された第1絶縁膜113と、第2電極ST2及び第1電極MT間に埋設された第2絶縁膜109、110と、第1ゲート電極MT、第2ゲート電極ST2、第3ゲート電極ST2、及び第1、第2絶縁膜上113、112にそれぞれ形成され、且つ第1絶縁膜113における水素原子の拡散を防止する第3絶縁膜114とを具備する。

(もっと読む)

半導体記憶装置

【課題】隣接セルとの容量を低減し、カップリング比を向上させる。

【解決手段】半導体記憶装置は、半導体基板101と、前記半導体基板上に所定間隔を空けて設けられた複数の第1の絶縁膜103と、前記第1の絶縁膜間にビット線方向に沿って設けられた素子分離領域102と、前記第1の絶縁膜上に設けられた第1の電荷蓄積膜104a、前記第1の電荷蓄積膜上に設けられ、ワード線方向の幅が前記第1の電荷蓄積膜より狭い第2の電荷蓄積膜104b、及び前記第2の電荷蓄積膜上に設けられ、ワード線方向の幅が前記第2の電荷蓄積膜より広い第3の電荷蓄積膜104cを有する電荷蓄積層104と、前記第2の電荷蓄積膜と前記素子分離領域との間に設けられた第2の絶縁膜107と、前記電荷蓄積層上及び前記素子分離領域上に前記第2の方向に沿って設けられた第3の絶縁膜105と、前記第3の絶縁膜上に設けられた制御ゲート電極106と、を備える。

(もっと読む)

半導体装置およびその製造方法

【課題】ゲート電極間にエアギャップを制御良く形成する。

【解決手段】本発明の半導体装置の製造方法では、半導体基板2上のゲート絶縁膜3上に浮遊ゲート電極用の多結晶シリコン層4を形成するときに、多結晶シリコン層4の上下方向の中間部のドーパント濃度を、その上下部のドーパント濃度よりも高くするように形成し、この多結晶シリコン層4上に形成したゲート間絶縁膜5上に制御ゲート電極用の多結晶シリコン層9を形成するときに、多結晶シリコン層9の上下方向の中間部のドーパント濃度を、その上下部のドーパント濃度よりも高くするように形成し、複数のゲート電極の側面が露出した状態で熱酸化処理を行なった後、エッチングすることにより、多結晶シリコン層4、9の各側面に凹部11、12を形成し、複数のゲート電極間に絶縁膜7を埋め込み、埋め込まれた絶縁膜7の中にエアギャップ8を形成する。

(もっと読む)

半導体記憶装置及びその製造方法

【課題】動作速度が向上し、信頼性の高い不揮発性半導体記憶装置を提供する。

【解決手段】半導体基板101上に所定間隔を空けて形成され、順に積層された第1の絶縁膜102、電荷蓄積層103、金属酸化物を含む第2の絶縁膜104、及び制御ゲート電極105をそれぞれ有する複数のワードラインと、ワードラインの側面及びワードライン間の半導体基板表面を覆う膜厚が15nm以下の第3の絶縁膜110と、互いに隣接ワードラインの制御ゲート電極105間に形成された第4の絶縁膜111と、第3の絶縁膜110及び第4の絶縁膜111に囲まれ、互いに隣接するワードラインの電荷蓄積層間103に位置する空洞部112と、を備える。

(もっと読む)

フラッシュメモリ素子の製造方法

【課題】フローティングゲート間のインターフェアレンス効果を減少させることが可能なフラッシュメモリ素子の製造方法を提供する。

【解決手段】トンネル絶縁膜102の側壁を保護ウィングスペーサAを持つ素子分離用絶縁膜122を形成する。次に、露出した窒化膜108およびバッファ酸化膜106を順次エッチングして除去する。その後、バッファ膜124はウェットまたはドライエッチング工程を用いて除去する。ウェットエッチング工程は好ましくはFNを用いて行う。その後、素子分離用絶縁膜122を含んだ全体構造上に誘電体膜およびコントロールゲート用導電膜を順次積層して形成する。

(もっと読む)

半導体記憶装置の製造方法

【課題】フローティングゲートを有するスプリットゲート型不揮発性半導体記憶装置において、コントロールゲートの側壁に、シリサイド・ショートを防止できるのに十分な高さの側壁絶縁膜を形成することができる製造方法を提供する。

【解決手段】半導体記憶装置の製造方法は、半導体基板1に形成したPウエル4上にゲート絶縁膜2を介してフローティングゲート用の導電体層16を形成する工程と、導電体層16上にTEOS−NSG等の第1のシリコン酸化膜から構成される第1のスペーサ10と、第1のスペーサ10と隣接し第1のシリコン酸化膜10よりもエッチングレートが遅い第2の高温シリコン酸化膜から構成される第2のスペーサ11と、を形成する工程と、第1及び第2のスペーサ10,11をマスクにして導電体層16を選択的に除去する工程と、第1のスペーサ10を除去して導電体層16の一部を露出させる工程と、を含む。

(もっと読む)

セルフアラインソース工程を用いる不揮発性メモリ装置の製造方法

【課題】セルフアラインソース工程を用いる不揮発性メモリ装置の製造方法を提供する。

【解決手段】半導体基板の上部にフィールド酸化膜を形成して前記基板にアクティブ領域を設定した後、基板の上部にトンネル酸化膜、第1導電層、層間誘電膜、第2導電層、および第1絶縁膜を順次に形成する。アクティブ領域の上部に第1導電層と第2導電層との積層ゲートを形成する。前記積層ゲートにより露出されたアクティブ領域に第1不純物をイオン注入して第1濃度のソース/ドレイン領域を形成し、ワードラインをエッチング用マスクとして用いて露出されたフィールド酸化膜を取り除くと共に、前記ワードライン上の第1絶縁をも取り除くか、均等にエッチングする。メモリセルアレーの積層ゲートを形成するためのマスクを用いてSASエッチング工程を行うので、別途のSASエッチング工程用のマスクを必要とせず、ビットラインコンタクト領域における工程マージンを確保することができる。

(もっと読む)

不揮発性半導体記憶装置及びその製造方法

【課題】電荷保持寿命の低下を抑制する。また、書き換え回数の向上と回路動作の速度の向上との両立を図る。

【解決手段】P−型Si基板1のうち、センストランジスタ領域上に、浮遊ゲート4を形成する。このとき、トンネル膜7に接する部分のリン濃度をリンが析出しない濃度とする。その後、浮遊ゲート4の表面上から、P−型Si基板1のうち、選択トランジスタ領域上に至って、絶縁膜8を形成する。このとき、絶縁膜8は、窒化膜、オキシナイトライド膜等の酸化膜より耐湿性及び誘電率が高い膜を用いる。その後、選択トランジスタのゲート電極9を形成する。このとき、ゲート電極9のリン濃度を浮遊ゲート4のトンネル膜7に接する部分の濃度よりも高くする。また、センストランジスタの絶縁膜8aの表面上に、浮遊ゲート4を覆い、且つ固定電位とされる、浮遊ゲート4の電位を遮蔽するための導電性膜を形成する。

(もっと読む)

プログラミング速度を改善したEEPROM、その製造方法及びその駆動方法

【課題】プログラミング速度の改善されたEEPROMを提供する。

【解決手段】半導体基板、半導体基板に活性領域を定義する素子分離膜、活性領域に形成されたトレンチを充填する少なくとも一つの絶縁膜、絶縁膜上に形成された浮遊ゲート絶縁膜、及び浮遊ゲート絶縁膜上に形成された浮遊ゲート導電膜を備えるEEPROMである。

(もっと読む)

半導体装置およびその製造方法

【課題】 閾値変調が抑制され、かつ、デバイス特性の安定性や生産性を確保しながら、フローティングゲート電極−アシストゲート電極間の絶縁性を向上させた半導体装置およびその製造方法を提供する。

【解決手段】 半導体装置は、半導体基板10と、半導体基板10の主表面上にゲート絶縁膜42を介して複数形成された電荷蓄積用のフローティングゲート電極FGと、半導体基板10の主表面上における複数のフローティングゲート電極FG間に形成されたアシストゲート電極AGと、フローティングゲート電極FG上からアシストゲート電極AG上にONO膜である絶縁膜70を介して設けられるコントロールゲート電極CGとを備え、複数のフローティングゲート電極FG間にエアギャップ50Vが形成され、フローティングゲート電極FG−アシストゲート電極AG間にエアギャップ60Vが形成されている。

(もっと読む)

1 - 12 / 12

[ Back to top ]