Fターム[5F101BA46]の内容

不揮発性半導体メモリ (42,765) | 電荷蓄積機構 (9,664) | トラップ蓄積型 (3,039) | 絶縁膜材料 (2,488) | 窒化膜含む (1,689) | MNOS型 (90)

Fターム[5F101BA46]に分類される特許

1 - 20 / 90

半導体装置

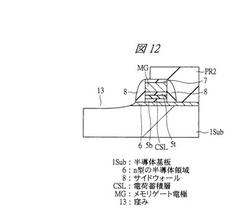

【課題】スプリットゲート型メモリセル構造を採用し、電荷蓄積層として窒化膜を用いる不揮発性メモリを有する半導体装置において電気的特性を向上させる。

【解決手段】半導体基板1Subの主面にn型の半導体領域6を形成した後、その上にスプリットゲート型のメモリセルのメモリゲート電極MGおよび電荷蓄積層CSLを形成する。続いて、そのメモリゲート電極MGの側面にサイドウォール8を形成した後、半導体基板1Subの主面上にフォトレジストパターンPR2を形成する。その後、フォトレジストパターンPR2をエッチングマスクとして、半導体基板1Subの主面の一部をエッチングにより除去して窪み13を形成する。この窪み13の形成領域では上記n型の半導体領域6が除去される。その後、その窪み13の形成領域にメモリセル選択用のnMISのチャネル形成用のp型の半導体領域を形成する。

(もっと読む)

メモリのプログラミング方法及びメモリアレイ

【課題】クリティカル・ディメンションの変動に鈍感であり且つ高速なメモリプログラミング方法等を提供する。

【解決手段】メモリの複数のメモリセルの夫々は、ウェルと、ソース及びドレイン領域と、記憶レイヤと、ゲートとを有する。メモリセルはマトリクス状である。同じ列ドレイン領域は同じビットラインへ接続し、同じ行ゲートは同じワードラインへ接続し、同じ列ソース領域は同じソースラインへ接続する。メモリは、いずれかのメモリセルへ電気的に接続されたワードラインへ第1の電圧を印加し、そのメモリセルへ電気的に接続されたビットラインへ少なくともプログラミング閾値だけ第1の電圧と異なる第2の電圧を印加し、そのメモリセルへ電気的に接続されたソースラインへ少なくともプログラミング閾値だけ第1の電圧と異なる第3の電圧を印加し、複数のメモリセルへ基板電圧を印加することによって、プログラミングされる。

(もっと読む)

半導体装置

【課題】頻繁なリフレッシュ動作が不要で、正常な読み出しを行うことのできる2トランジスタ型のDRAMを備えた半導体装置を提供する。

【解決手段】本実施形態の半導体装置は、ゲートが第1配線に接続され、第1ソース/ドレインの一方が第2配線に接続された第1トランジスタと、ゲート絶縁膜、ゲート電極、および前記ゲート絶縁膜と前記ゲート電極との間に設けられしきい値を変調するしきい値変調膜を有するゲート構造と、第2ソース/ドレインとを備え、前記ゲート電極が前記第1トランジスタの前記第1ソース/ドレインの他方に接続され、前記第2ソース/ドレインの一方が第3配線に接続され、前記第2ソース/ドレインの他方が第4配線に接続された第2トランジスタと、を備えている。

(もっと読む)

不揮発性半導体記憶装置及びその製造方法とデータ書き換え方法

【課題】データ保持時間を、マスクROMと同様の無限大とすることができる、長期にわたりデータを保持できる信頼性の高いEEPROMを提供する。

【解決手段】不揮発性半導体記憶装置は、所定のセンスレベルに対して熱平衡状態しきい値電圧が正方向である第1の不揮発性半導体記憶素子100に正のデータを記憶し、熱平衡状態しきい値電圧が負方向である第2の不揮発性半導体記憶素子200に負のデータを記憶することでデータ保持時間を無限大にする。

(もっと読む)

不揮発性半導体記憶装置、及びその製造方法

【課題】チャネル移動度を向上させた不揮発性半導体記憶装置、及びその製造方法を提供する。

【解決手段】不揮発性半導体記憶装置は、半導体基板20上に設けられたメモリトランジスタ40と選択トランジスタ50を有する。メモリトランジスタ40は、導電層41a〜41d、メモリゲート絶縁層43、柱状半導体層44、及び酸化層45を有する。導電層41は、メモリトランジスタ40のゲートとして機能する。メモリゲート絶縁層43は、導電層の側面に接する。半導体層44は、導電層と共にメモリゲート絶縁層43を一方の側面で挟み、半導体基板20に対して垂直方向に延び、メモリトランジスタ40のボディとして機能する。酸化層45は、半導体層44の他方の側面に接する。半導体層44は、シリコンゲルマニウムにて構成される。酸化層45は、酸化シリコンにて構成される。

(もっと読む)

半導体装置の製造方法

【課題】同一セル内に複数設けられたビットへの個々への書き込み動作が他ビットへの書き込み量に依存することなく正常に行われ、さらには、書き込み・読み出し特性を損なうことなくSONOS構造セルのいっそうの微細化を可能とする半導体装置およびその製造方法を提供する。

【解決手段】本発明による半導体装置は、一対の第1拡散領域を有する基板と、該基板上に形成された酸化膜および該酸化膜上に形成された電荷蓄積層とを有するゲート部とを有し、前記電荷蓄積層は当該電荷蓄積層中に離隔して位置する複数のビット領域を有する電気的絶縁膜である。また、酸化膜は、ビット領域に対応する部分がトンネル酸化膜として作用する膜厚の薄膜部およびビット領域間に位置する部分がトンネル効果による電荷輸送を抑制する膜厚の厚膜部を有している。

(もっと読む)

デュアル機能を有する不揮発性半導体メモリセル

【課題】デュアル機能を有する不揮発性半導体メモリセルは、基板、第1ゲート、第2ゲート、第3ゲート、電荷蓄積層、第1拡散領域、第2拡散領域及び第3拡散領域を有する。

【解決手段】第2ゲート及び第3ゲートは、デュアル機能のワンタイムプログラミング機能に対応する第1電圧及びデュアル機能のマルチタイムプログラミング機能に対応する第2電圧を受けるために用いられる。第1拡散領域は、ワンタイムプログラミング機能に対応する第3電圧及びマルチタイムプログラミング機能に対応する第4電圧を受けるために用いられる。第2拡散領域は、マルチタイムプログラミング機能に対応する第5電圧を受けるために用いられる。

(もっと読む)

半導体装置

【課題】緻密で高耐圧な絶縁膜を提供することを目的とする。

【解決手段】基板上に半導体膜を有し、半導体膜上に第1の絶縁膜を有し、第1の絶縁膜上に導電膜を有し、導電膜上に第2の絶縁膜を有し、第1の絶縁膜は、第2の絶縁膜よりも緻密であり、第1の絶縁膜は、珪素と、酸素と、窒素とを有する。第1の絶縁膜は、希ガスを有し、その膜厚は、1nm以上100nm以下である。このような第1の絶縁膜はゲート絶縁膜として機能させる。

(もっと読む)

半導体装置

【課題】FETの駆動力性能や遮断性能などを向上できる半導体装置を提供する。

【解決手段】半導体装置は、半導体基板と、前記半導体基板上に形成され、オフ状態とオン状態とで閾値電圧を可変させるFETからなる半導体素子と、を備える。前記半導体素子は、前記半導体基板のチャネル形成箇所の上方に形成される絶縁膜と、前記絶縁膜の上方に配置されるゲート電極と、前記絶縁膜と前記ゲート電極との間に介挿され、前記チャネルとの間よりも、前記ゲート電極との間で、より多くの電子の授受を行なうチャージトラップ膜と、を有する。

(もっと読む)

半導体記憶装置

【課題】電荷蓄積層及び制御ゲートを有する半導体記憶装置のバックバイアス効果による影響を低減させることにより集積度を向上させ、占有面積を増加させずに浮遊ゲートと制御ゲートとの容量の比をより一層増大させるとともに、製造プロセスに起因するセル特性のばらつきが抑制された半導体記憶装置を提供する。

【解決手段】半導体基板と、少なくとも1つの島状半導体層110、該島状半導体層110の側壁の周囲の全部又は一部に形成された電荷蓄積層513及び制御ゲート523から構成される少なくとも1つのメモリセルとを有する半導体記憶装置であって、前記メモリセルの島状半導体層110が不純物拡散層により前記半導体基板から電気的に絶縁されてなる。

(もっと読む)

不揮発性半導体記憶装置

【課題】 BiCSメモリのような積層型メモリの書き込み動作を高速化することが可能な不揮発性半導体記憶装置を提供する。

【解決手段】 積層型のメモリセル構造を有する不揮発性半導体記憶装置であって、半導体基板上に、複数のメモリセルを積層してなるストリングを複数個配置したメモリセルアレイ11と、メモリセルアレイ11の任意のストリングをサンプルストリングとして選択し、該選択したサンプルストリングに対してデータの書き込みを行う回路12,14,16,30と、サンプルストリングの各メモリセルに対する書き込み回数をレイヤー毎に保持する書き込み回数記憶部31と、記憶部31に記憶されたレイヤー毎の書き込みパルス数を同一レイヤーの他のストリングのメモリセルの書き込み電圧の初期値に反映させる回路33とを備えている。

(もっと読む)

半導体装置の製造方法

【課題】第1MISFETのゲート電極と第2MISFETのゲート電極とを別工程で形成する半導体装置の製造技術において、第1MISFETと第2MISFETの信頼性向上を図ることができる技術を提供する。

【解決手段】半導体基板20上にゲート絶縁膜26、電荷蓄積膜27、絶縁膜28、ポリシリコン膜29、酸化シリコン膜30、窒化シリコン膜31およびキャップ絶縁膜32からなる積層膜を形成する。そして、フォトリソグラフィ技術およびエッチング技術を使用して、低耐圧MISFET形成領域および高耐圧MISFET形成領域に形成されている積層膜を除去する。その後、半導体基板20上にゲート絶縁膜34、36、ポリシリコン膜37およびキャップ絶縁膜38を形成する。そして、低耐圧MISFET形成領域および高耐圧MISFET形成領域にゲート電極を形成した後、メモリセル形成領域にゲート電極を形成する。

(もっと読む)

不揮発性半導体記憶装置及びその製造方法

【課題】隣接セル間干渉を抑制した不揮発性半導体記憶装置及びその製造方法を提供する。

【解決手段】実施形態によれば、第1メモリストリングと、ソースコンタクトと、第2メモリストリングと、シールド導電層と、を備えた不揮発性半導体記憶装置を提供する。第1メモリストリングは、第1軸に沿って並ぶ第1メモリセル及び第2メモリセルを含む。ソースコンタクトは、第1メモリストリングのソース側の端に設けられる。第2メモリストリングは、第1軸に対して直交する第2軸に沿って第1メモリセルと並ぶ第3メモリセルを含み、第1軸に沿って延在する。シールド導電層は、第1メモリストリングと第2メモリストリングとの間において第1軸に沿って延在し、ソースコンタクトと電気的に接続される。

(もっと読む)

半導体記憶装置、半導体ウェーハ及び半導体記憶装置の製造方法

【課題】合わせマークを認識し易くし、マスク合わせ精度を向上する半導体記憶装置、半導体ウェーハ及び半導体記憶装置の製造方法を提供する。

【解決手段】実施形態によれば、メモリセルアレイ部と、メモリセルアレイ部と並置された合わせマーク部と、を備えた半導体記憶装置が提供される。メモリセルアレイ部は、第1メモリストリングと、第2メモリストリングと、素子分離絶縁層と、を含む。第1、第2メモリストリングは、半導体層の主面上に設けられる。素子分離絶縁層は、第1、第2メモリストリングを分断する。合わせマーク部は、マーク部半導体層及びマーク部絶縁層を含む。マーク部半導体層は、上記の半導体層の一部である。マーク部絶縁層は、素子分離絶縁層に用いられる材料と同じ材料を含む。マーク部半導体層の上面は、マーク部絶縁層の上面を含む平面とは異なる平面内に含まれる。

(もっと読む)

半導体装置

【課題】パーコレーションリークを抑制可能な構造を有する半導体装置を提供する。

【解決手段】ソース領域18、ドレイン領域18及びチャネル領域を有する半導体領域と、チャネル領域上に形成された第1のトンネル絶縁膜12と、第1のトンネル絶縁膜上に形成され、エネルギー障壁を有する障壁層13と、障壁層上に形成された第2のトンネル絶縁膜14と、第2のトンネル絶縁膜上に形成され、SiY(SiO2)X(Si3N4)1-X (ただし、0≦X≦1、Y>0)で表される絶縁膜を具備する電荷蓄積部15と、電荷蓄積部上に形成され、エネルギー障壁の高さを制御する制御電極17とを備え、X及びYは、[2×2X/(4−2X)+(4−4X)/(4−2X)]×[Y/(Y+7−4X)]≧0.016 なる関係を満たし、障壁層は、クーロンブロッケイド条件を満たす導電性微粒子を含んだ微粒子層で形成されている。

(もっと読む)

不揮発性半導体記憶装置

【課題】本実施形態は、データ書き込みの高速化をはかり得る不揮発性半導体記憶装置を提供する。

【解決手段】実施形態の不揮発性半導体記憶装置によれば、半導体基板上に積層された複数のワード線に、電荷蓄積層を有する複数のメモリセルがそれぞれ接続され、且つ、隣接するメモリセル間で電荷蓄積層が連続しているセル構造のメモリセルアレイと、前記メモリセルアレイのn番目(nは自然数)のワード線に接続されたメモリセル群にデータを書き込む際に、(n−1)番目及び(n+1)番目のワード線に接続されたメモリセル群に同一の書き込み電圧を同時に印加するよう制御する制御回路と、を具備したことを特徴とする。

(もっと読む)

半導体素子用パターン構造物の形成方法

【課題】ラインパターン構造物の形成方法を提供すること。

【解決手段】ラインパターン構造物及びその形成方法において、ラインパターン構造物は切断部位を含むライン形状を有する少なくとも1つの第1ラインパターンを含む。最外郭に位置する前記第1ラインパターンと隣り合って前記第1ラインパターンと平行した延在ラインと、前記第1ラインパターンの切断部位と隣接する領域で前記第1ラインパターン方向へ向かうように前記延在ラインから突出された少なくとも1つの突出パターンを含む2つの第2ラインパターンを含む。前記ラインパターン構造物は不良が減少し、簡単な工程を通じて形成されてもよい。

(もっと読む)

半導体装置の製造方法

【課題】レジスト膜のスリミング時にその膜厚の消費を抑制する半導体装置の製造方法を提供する。

【解決手段】半導体装置の製造方法は、基体11上に複数の絶縁層25と複数の導電層WLとを交互に積層して積層体を形成する工程と、積層体上にレジスト膜50を形成する工程と、レジスト膜50をマスクにして絶縁層25及び導電層WLをプラズマエッチングする工程と、ホウ素、リン及びヒ素の少なくとも1つを含むガスを用いたプラズマ処理により、レジスト膜50の上面に、ホウ素、リン及びヒ素の少なくとも1つを含む硬化層51を形成する工程と、レジスト膜50の上面に硬化層51が形成された状態で、酸素を含むガスを用いたプラズマ処理によりレジスト膜50の平面サイズをスリミングする工程と、を備えた。

(もっと読む)

不揮発性メモリ装置およびその動作方法と、それを含むメモリシステム

【課題】本発明は少ない消去単位を有する不揮発性メモリ装置の動作方法を提供する。

【解決手段】本発明の不揮発性メモリ装置の動作方法は、ビットラインに接続された第1ストリングの接地選択ラインをフローティングし、ビットラインに接続された第2ストリングの接地選択ラインに消去禁止電圧を印加し、そして第1及び第2ストリング等に消去動作電圧を印加する。

(もっと読む)

不揮発性半導体記憶装置

【課題】メモリセルアレイ端部の耐圧を向上させる。

【解決手段】不揮発性半導体記憶装置10は、メモリセルトランジスタが配置される第1の領域と、メモリセルトランジスタに電気的に接続されたワード線を引き出す電極21が配置される第2の領域と、周辺トランジスタが配置される第3の領域とを有する。第1の領域には、第1の幅を有する複数の第1のアクティブ領域AA1が設けられ、第2及び第3の領域にはそれぞれ、第1の幅より広い第2の幅を有する複数の第2及び第3のアクティブ領域AA3,AA5が設けられる。第2の領域の素子分離層23Bの上面は、第1の領域の素子分離層23Aの上面より高く、第2の領域の電荷蓄積層32Bは、上部の角の曲率半径が、第3の領域の電荷蓄積層43よりも大きい。

(もっと読む)

1 - 20 / 90

[ Back to top ]