Fターム[5F101BA62]の内容

不揮発性半導体メモリ (42,765) | 電荷蓄積機構 (9,664) | その他記憶作用 (122) | 強誘電体 (98)

Fターム[5F101BA62]に分類される特許

21 - 40 / 98

不揮発性メモリセル及びその製造方法

【課題】同一の基板上に形成されたメモリトランジスタ及び駆動トランジスタを備える透明不揮発性メモリセル及びその製造方法を提供する。

【解決手段】本発明による不揮発性メモリセルは、基板上に形成された半導体膜、バッファー膜、有機強誘電体膜及びゲート電極を含むメモリトランジスタと;前記基板上に形成された前記半導体膜、前記バッファー膜、ゲート絶縁膜及び前記ゲート電極を含む駆動トランジスタと;を備える。本発明によれば、同一の基板上に形成されたメモリトランジスタ及び駆動トランジスタを備え、可視光領域で透明な不揮発性メモリセルを提供することができる。

(もっと読む)

半導体装置及びその製造方法

【課題】優れた特性を有する半導体装置及びその製造方法を提供する。

【解決手段】半導体基板100に設けられた素子形成領域10bと、素子形成領域上に形成されたトンネル絶縁膜11と、トンネル絶縁膜上に形成された電荷蓄積絶縁膜12と、電荷蓄積絶縁膜上に形成されたブロック絶縁膜14と、ブロック絶縁膜上に形成された制御ゲート電極15と、を備えたメモリセルトランジスタと、メモリセルトランジスタに隣接して形成された素子分離領域13と、を具備し、メモリセルトランジスタのチャネル幅方向に平行な断面において、電荷蓄積絶縁膜の端部の膜厚は、電荷蓄積絶縁膜の中央部の膜厚よりも薄い。

(もっと読む)

不揮発性半導体記憶装置、その製造方法、その書き込み方法、その読み出し方法、記録媒体並びに半導体記憶装置

【課題】 電荷捕獲量の調節を容易且つ確実に行い、情報ばけ等の不都合の発生を防止して所望の多値情報を記憶する。

【解決手段】 ソース領域3−ドレイン領域4間のチャネル領域Cとゲート電極6との間に、ゲート酸化膜11、シリコン窒化膜12、シリコン酸化膜13、シリコン窒化膜14、シリコン酸化膜15、シリコン窒化膜16及びシリコン酸化膜17が順次積層されてなる電荷捕獲膜5が配されて半導体記憶装置が構成される。ここで、各窒化膜12,14,16とその下層の各酸化膜11,13,15,17との間に存するトラップに電荷を蓄積することで、4値("00","01","10","11")の情報が記憶される。

(もっと読む)

薄膜トランジスタ及び半導体メモリセル

【課題】バックゲート電極へのリーク電流を抑えた薄膜トランジスタ(MFSFET)を提供することにある。

【解決手段】基板11上に形成されたゲート電極12と、ゲート電極12上に形成された強誘電体膜からなるゲート絶縁膜13と、ゲート絶縁膜13上に形成されたオーミック電極からなるソース・ドレイン電極15s、15dと、ソース・ドレイン電極15s、15d間のゲート絶縁膜13上に形成された半導体膜14とを備え、ゲート絶縁膜13と半導体膜14との界面をチャネルとする。

(もっと読む)

半導体メモリセルおよびその製造方法

【課題】スイッチング特性に優れ、セルサイズの小さい半導体メモリセルを提供することにある。

【解決手段】ゲート絶縁膜が強誘電体膜4で構成されたMFSFET21からなるメモリ素子と、ゲート絶縁膜が常誘電体膜9で構成されたMISFET22からなる選択スイッチング素子とを備えた半導体メモリセル20であって、MFSFETの第1のゲート電極3は、基板1上の結晶性絶縁膜2表面に形成された結晶性導電膜3からなり、強誘電体膜4は、第1のゲート電極3を覆って結晶性絶縁膜2上に形成され、常誘電体膜9は、半導体膜5を介して強誘電体膜4上に形成され、MISFET22の第2のゲート電極10は、常誘電体膜9上に形成されている。

(もっと読む)

半導体メモリセルおよびその製造方法

【課題】スイッチング特性に優れ、セルサイズの小さい半導体メモリセルを提供することにある。

【解決手段】ゲート絶縁膜が強誘電体膜4で構成されたMFSFET21からなるメモリ素子と、ゲート絶縁膜が常誘電体膜9で構成されたMISFET22からなる選択スイッチング素子とを備え、強誘電体膜4と常誘電体膜9とはアモルファス半導体膜5を介して積層されており、強誘電体膜4側に、MFSFET21の第1のゲート電極3が形成され、常誘電体膜9側に、MISFETの第2のゲート電極10が形成されている。アモルファス半導体膜5は、MFSFET21及びMISFET22の共通のチャネル層を構成しており、アモルファス半導体膜5の主面上に、MFSFET21及びMISFET22に共通のソース電極6及びドレイン電極8が形成されている。

(もっと読む)

不揮発性記憶装置の記憶維持

【課題】NAND型の不揮発性記憶装置において、障壁高さが低い絶縁体や誘電率の高い絶縁体や電荷をトラップする絶縁体や強誘電体を記憶素子に使用し、高速化や書込み回数の制約を改善できるが、電荷の漏洩が増えて長期の記憶維持が困難になる。また、微細化や多値化によっても記憶維持が困難になっている。読書き操作時の電荷の漏洩をある程度容認し得る装置を提供する。

【解決手段】漏洩した電荷はリフレッシュ操作で回復して、動作マージンが不足気味の記憶素子でも利用可能にする。記憶ブロック毎の読書き回数をカウンタで集計して、読書き回数が一定の値を超過した記憶ブロックをリフレッシュする。

(もっと読む)

有機強誘電メモリーセル

【課題】優れた特性を有するメモリーセルを提供することにある。

【解決手段】

a)二つの対向面を有する有機半導体、

b)有機半導体の一つの面と接触する二つの隔置された電極(その間の距離はチャンネル長さであり、その間の有機半導体の部分はチャンネル領域として形成される)、

c)誘電率及び二つの対向面を有する強誘電ポリマー(一つの面はチャンネル領域の少なくとも一部について有機半導体の一つの面と接触している)、及び

d)チャンネル領域の少なくとも一部について強誘電ポリマーの一つの面と接触しているゲート電極

を含むことを特徴とするメモリーセル。

(もっと読む)

絶縁ゲート型半導体装置の製造方法

【課題】非ヒステリシストランジスタとヒステリシストランジスタとを混載する場合において、欠陥や不純物混入リスクの少ない良好な基板界面を保ったまま、同一材料の絶縁膜を用いて、ヒステリシストランジスタと非ヒステリシストランジスタとを同一基板上に混載することができる絶縁ゲート型半導体装置の製造方法を提供する。

【解決手段】第1及び第2のトランジスタ形成領域上に第1のトランジスタにヒステリシス特性を与える絶縁膜1を形成し、これを第1のトランジスタのゲート絶縁1膜とする工程、及び、第2のトランジスタ形成領域上の絶縁膜1を部分的にエッチング除去することにより、第2のトランジスタにヒステリシス特性を与えない絶縁膜とし、これを第2のトランジスタのゲート絶縁膜とする工程を含む。

(もっと読む)

半導体装置及びその製造方法

【課題】最適化された電荷蓄積層を有する特性が優れた半導体装置を提供する。

【解決手段】半導体基板10に設けられた素子形成領域と、素子形成領域上に形成されたトンネル絶縁膜11と、トンネル絶縁膜上に形成された電荷蓄積絶縁膜12と、電荷蓄積絶縁膜上に形成されたブロック絶縁膜14と、ブロック絶縁膜上に形成された制御ゲート電極15と、をそれぞれ備えた第1及び第2のメモリセルトランジスタと、第1のメモリセルトランジスタと第2のメモリセルトランジスタとの間に形成された素子分離領域13と、を具備し、第1及び第2のメモリセルトランジスタのチャネル幅方向の断面において、素子分離領域の上面は、電荷蓄積絶縁膜の上面の中央部よりも高く、チャネル幅方向の断面において、電荷蓄積絶縁膜の端部の膜厚は、電荷蓄積絶縁膜の中央部の膜厚よりも薄い。

(もっと読む)

強誘電体及び記憶装置

【課題】数nm程度のセルサイズを実現可能な強誘電体及び記憶装置を提供すること。

【解決手段】強誘電体2は、分子内で正に帯電された水素原子群(第一原子群)15と負に帯電された酸素原子群(第二原子群)16とが結合された水分子(極性分子)17同士が、さらに水素原子群15又は酸素原子群16が一端2a又は他端2bに配されるよう一方向に交互に配列された5本の一次元鎖13A〜13Eを有するアイスナノチューブ11Aと、アイスナノチューブ11Aを内包するカーボンナノチューブ(ナノチューブ)11Bと、を備えている。

(もっと読む)

強誘電体ゲート電界効果トランジスタ、それを用いたメモリ素子及び強誘電体ゲート電界効果トランジスタの製造方法

【課題】ゲート構造にIFI構造が含まれるMFS型メモリの強誘電体ゲート電界効果トランジスタにおいて、強誘電体膜の強誘電体特性及びトランジスタの電気特性の劣化を防止する。

【解決手段】Si基板1と、Si基板1上に少なくともHfSiON膜2、強誘電体膜3及びHfSiON膜4が、この順で積層されたゲート構造を有しており、HfSiON膜2及びHfSiON膜4は、強誘電体膜3を加熱処理によって形成する焼成温度で非晶質である。

(もっと読む)

強誘電体ゲート有機電界効果トランジスタ、それを用いたメモリ素子及び強誘電体ゲート有機電界効果トランジスタの製造方法

【課題】強誘電体膜及びゲート電極間のリーク電流値を低減させると共に耐絶縁性を向上させる。

【解決手段】Si基板1と、Si基板1上に少なくともHfSiON膜2、強誘電体膜3HfSiON膜4及びC60膜6が、この順で積層されたゲート構造を有しており、強誘電体膜3の、HfSiON膜4と接する側の表面におけるRa値とRms値との和の第1絶対値が、HfSiON膜4の膜厚以下であり、かつ、HfSiON膜4の、C60膜6と接している側の表面におけるRa値とRms値との和の第2絶対値が3.0nm以下である。

(もっと読む)

強誘電体膜、強誘電体膜を有する半導体装置、及びそれらの製造方法

【課題】 従来よりも小型化が可能で安定した動作が可能であり、下地との密着性に優れた強誘電体膜、強誘電体膜を用いた半導体装置、その製造方法および強誘電体膜を用いた強誘電体デバイスを提供する。

【解決手段】 半導体装置71は基板55、絶縁体56、酸化タンタル膜66、強誘電体膜(STN膜)57、上部電極膜62を有している。

酸化タンタル膜66は強誘電体膜(STN膜)57を結晶化する際に下地となる。

酸化タンタル膜66は酸素を含み、格子情報が強誘電体膜(STN膜)57の結晶と近似している。

そのため、酸化タンタル膜66上にSTNを結晶化すると、酸素欠損がなく、結晶粒径が100nm以下の強誘電体膜(STN膜)57が得られる。

(もっと読む)

半導体記憶装置

【課題】簡単な動作で、MFSFETに記憶された多値データを読み出すことのできる半導体記憶装置を提供することにある。

【解決手段】強誘電体膜13からなるゲート絶縁膜と、半導体膜14からなるチャネルとを有する第1の電界効果トランジスタ21で構成されたメモリセルと、メモリセルに直列に接続された読み出し用の負荷素子24とを備え、メモリセルは、強誘電体膜13の分極状態に応じた、少なくとも3値以上のチャネル抵抗値を多値データとして記憶している。メモリセルに記憶された多値データは、メモリセルと負荷素子24との間の中間電位を検出することによって読み出され、読み出し動作は、メモリセルに記憶された多値データを、チャネル抵抗値の高い状態から順に判別することによって実行される。

(もっと読む)

半導体装置およびその製造方法、および光変調装置およびその製造方法

【課題】自己整合でエッチング可能かつ製造方法の容易な光変調装置およびその製造方法を提供する。

【解決手段】下部電極2と、下部電極2上に配置される強誘電体膜3と、強誘電体膜3上に配置される上部電極4とを備えた強誘電体キャパシタを含む光変調装置であって、上部電極4が、強誘電体膜3のエッチングマスクとして強誘電体膜3と自己整合パターニングされた導電膜を含んでいることを特徴とし、さらに強誘電体キャパシタを駆動するための制御回路を半導体基板10上に有するとともに、強誘電体キャパシタを、下部電極2と上部電極4間に印加する電界に応じて強誘電体膜3の屈折率が変化するファブリーペロー型の共振器6として機能させる。

(もっと読む)

強誘電体メモリセルおよび強誘電体メモリ

【課題】強誘電体メモリセルに保持されたデータの読み出しマージンの低下を防止する。

【解決手段】強誘電体トランジスタFTRは、ゲート絶縁膜に強誘電体膜FFを有し、読み出しワード線RWLにソース/ドレインの一方が接続され、読み出しビット線RBLにソース/ドレインの他方が接続され、プレート線PLにウエルNWが接続されている。選択トランジスタSTRは、書き込みワード線WWLにゲートが接続され、書き込みビット線WBLにソース/ドレインの一方が接続され、強誘電体トランジスタのゲートにソース/ドレインの他方が接続されている。強誘電体トランジスタのソースおよびドレインを用いて読み出し動作を行うことで、読み出し動作時に、強誘電体トランジスタのゲート絶縁膜を構成する強誘電体膜に電圧が印加されることを避けることができ、強誘電体膜の分極状態が変化することを防止できる。

(もっと読む)

強誘電体メモリ

【課題】 強誘電体メモリセルに保持されたデータの読み出しマージンの低下を防止する。

【解決手段】 強誘電体トランジスタは、ゲート絶縁膜に強誘電体膜を有し、ソース/ドレインの一方がプレート線に接続され、ソース/ドレインの他方およびウエルが接続ノードに接続され、ゲートがドライブ線に接続されている。選択トランジスタは、ゲートがワード線に接続され、ソース/ドレインの一方がビット線に接続され、ソース/ドレインの他方が接続ノードに接続されている。プレート線およびドライブ線は、第1方向に並ぶメモリセルの列に共通に接続されている。ビット線は、第1方向に交わる第2方向に並ぶメモリセルの列に共通に接続されている。ワード線は、第1および第2方向に対して斜めに配線されている。第1方向に並ぶメモリセルおよび第2方向に並ぶメモリセルは、互いに異なるワード線に接続されている。

(もっと読む)

半導体素子及び半導体装置

【課題】短チャネル効果が抑制され高い電流駆動力を有する細線半導体素子を実現する。

【解決手段】半導体基板上に設けられた絶縁領域と、絶縁領域上に略平行に整列して設けられた第一導電型の複数の線状半導体層と、各線状半導体層に離間して設けられた第二導電型のソース・ドレイン領域と、ソース・ドレイン領域の間に設けられたチャネル領域と、各線状半導体層の上面と側面上に設けられた第一の絶縁膜と、第一の絶縁膜上に設けられ、複数の線状半導体層と交差するように連続的に設けられたゲート電極とを有し、線状半導体層を線方向に流れる電流に垂直、且つ基板表面に平行に測ったチャネル領域の長さが、チャネル領域中の不純物濃度で決まる最大空乏層幅の二倍以下であり、複数の線状半導体層の間隔が、線状半導体層の上面とゲート電極との間隔の二倍以下であり、絶縁領域の表面の少なくとも一部に於ける誘電率が、酸化シリコンの誘電率よりも低い。

(もっと読む)

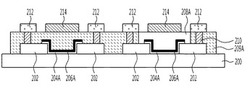

半導体メモリセル及びそれを用いた半導体メモリアレイ

【課題】安定した特性を有する半導体メモリセル、及びそれを用いた高密度な半導体メモリアレイを提供することにある。

【解決手段】第1のFET31からなるメモリ素子と、第2のFET32からなる選択スイッチとが直列に接続され、基板1上に積層された半導体膜4及び誘電体膜8が、第1及び第2のFET31、32の共通のチャネル及びゲート絶縁膜を構成している。誘電体膜8上には、第1のFET31の第1のゲート電極9、及び第2のFET32の第2のゲート電極10が形成され、半導体膜4上には、ドレイン電極5及びソース電極6が形成されている。そして、半導体膜4下には、強誘電体膜3を介してバックゲート電極2が形成され、チャネルを構成する半導体膜4の端部は、バックゲート電極2の端部の内側に位置している。

(もっと読む)

21 - 40 / 98

[ Back to top ]