Fターム[5F101BD15]の内容

不揮発性半導体メモリ (42,765) | 素子構造 (12,113) | メモリセル(センサ) (3,677) | MOSトランジスタ (3,641) | チャンネル領域 (360) | チャンネルドープ (111) | 部分的チャンネルドープ (56)

Fターム[5F101BD15]に分類される特許

1 - 20 / 56

半導体記憶装置及び半導体記憶素子

【課題】素子の面積を増大させることなく、かつ、コントロールゲート電圧を制御しなくとも、低電圧で書き込み量を大幅に増やすことが可能であり、また、安定して十分な書き込みを行うことが可能である不揮発性半導体装置を提供すること。

【解決手段】ドレインアバランシェホットエレクトロンにより書き込みを行う半導体記憶素子であって、第1導電型の半導体基板に形成された第2導電型の第1の半導体層と、前記第1の半導体層上に絶縁膜を介して設けられたフローティングゲートと、前記フローティングゲート下部の前記第1の半導体層の表面に形成されたチャネル領域と、前記チャネル領域に接触するように前記第1の半導体層上に設けられた第1導電型のソース領域及びドレイン領域とを有するMOSトランジスタであって、前記チャネル領域が2種類以上のキャリア濃度の分布をもつ半導体記憶素子とした。

(もっと読む)

不揮発性半導体装置およびその製造方法

【課題】絶縁体に電荷を蓄える不揮発性メモリにおいて、データ保持特性を向上させることのできる技術を提供する。

【解決手段】メモリゲート電極MGと半導体基板1との間に介在する電荷蓄積層CSLをメモリゲート電極MGのゲート長または絶縁膜6t,6bの長さよりも短く形成して、電荷蓄積層CSLとソース領域Srmとのオーバーラップ量(Lono)を40nm未満とする。これにより、書込み状態では、書き換えを繰り返すことによって生じるソース領域Srm上の電荷蓄積層CSLに蓄積される正孔が少なくなり、電荷蓄積層CSL中に局在する電子と正孔との横方向の移動が少なくなるので、高温保持した場合のしきい値電圧の変動を小さくすることができる。また、実効チャネル長を30nm以下にすると、しきい値電圧を決定する見かけ上の正孔が少なくなり、電荷蓄積層CSL中での電子と正孔との結合が少なくなるので、室温保持した場合のしきい値電圧の変動を小さくすることができる。

(もっと読む)

半導体装置の製造方法

【課題】同一セル内に複数設けられたビットへの個々への書き込み動作が他ビットへの書き込み量に依存することなく正常に行われ、さらには、書き込み・読み出し特性を損なうことなくSONOS構造セルのいっそうの微細化を可能とする半導体装置およびその製造方法を提供する。

【解決手段】本発明による半導体装置は、一対の第1拡散領域を有する基板と、該基板上に形成された酸化膜および該酸化膜上に形成された電荷蓄積層とを有するゲート部とを有し、前記電荷蓄積層は当該電荷蓄積層中に離隔して位置する複数のビット領域を有する電気的絶縁膜である。また、酸化膜は、ビット領域に対応する部分がトンネル酸化膜として作用する膜厚の薄膜部およびビット領域間に位置する部分がトンネル効果による電荷輸送を抑制する膜厚の厚膜部を有している。

(もっと読む)

半導体装置およびその製造方法

【課題】スプリットゲート構造の不揮発性メモリセルを有する半導体装置において、メモリアレイのレイアウト面積を低減する。

【解決手段】給電領域において、メモリゲートシャント部が形成される領域の素子分離部に溝25が形成されており、選択ゲートシャント部に備わる選択ゲートシャント電極VCは、メモリセル形成領域に形成された選択ゲート電極CGに繋がる第1導電膜からなり、メモリゲートシャント部に備わるメモリゲートシャント電極VMは、給電領域に形成された選択ゲート電極CGの延長部の片側面の一部および素子分離部に形成された溝25の側面の一部に絶縁膜6b,6tおよび電荷蓄積層CSLを介してサイドウォール状に形成され、メモリセル形成領域に形成されたメモリゲート電極MGに繋がる第2導電膜からなる。

(もっと読む)

不揮発性半導体記憶装置および不揮発性半導体記憶装置の製造方法

【課題】対向する二つの記憶素子のコントロールゲートのゲート長に起因する記憶素子の特性のばらつきを抑制する。

【解決手段】上記の課題を解決するために、不揮発性半導体記憶装置(1)を以下のように構成する。第1不揮発性メモリセル(1a)は、第1チャネル領域(11a)と、第1フローティングゲート(5a)と、第1コントロールゲート(6a)とを含むものとする。また、第2不揮発性メモリセル(1b)は、第2チャネル領域(11b)と、第2フローティングゲート(5b)と、第2コントロールゲート(6b)とを含むものとする。ここにおいて、第1チャネル領域(11a)は、第1フローティングゲート側チャネル領域(13a)と、第1コントロールゲート側チャネル領域(12a)とを備え、第1コントロールゲート側チャネル領域(12a)は不純物濃度が濃い高濃度ポケット領域(10)を備える。

(もっと読む)

半導体装置

【課題】半導体装置の信頼性を向上する。

【解決手段】メモリセルMCは、半導体基板1の主面上のゲート絶縁膜5を介して設けられたコントロールゲート電極CGと、コントロールゲート電極CGの側面および半導体基板1の主面に沿って設けられたONO膜9と、ONO膜9を介してコントロールゲート電極CGの側面および半導体基板1の主面上に設けられたメモリゲート電極MGとを有する。コントロールゲート電極CGおよびメモリゲート電極MGの上部には、シリサイド膜15およびシリサイド膜15の表面の酸化によって形成された絶縁膜51が設けられている。

(もっと読む)

半導体装置

【課題】書き込みおよび消去特性が良好で、記憶情報の不揮発性が高い不揮発性記憶装置を提供する。

【解決手段】不揮発性記憶装置は、第1不純物領域1、第2不純物領域2、並びに第1不純物領域1および第2不純物領域2のいずれとも離間して形成された一組のソース領域3およびドレイン領域4、が区画された半導体基板10と、半導体基板10の上に形成された絶縁膜と、フローティングゲート30と、を有し、フローティングゲート30は、平面視において、第1部分31は第1不純物領域1に重複し、第2部分32は第1不純物領域1および第2不純物領域2の間に位置し、第3部分33は一組のソース領域3およびドレイン領域4の間に位置し、フローティングゲート30の第3部分33と半導体基板10との間に位置する絶縁膜は、フローティングゲート30の他の部分と半導体基板10との間に位置する絶縁膜よりも厚みが大きい。

(もっと読む)

半導体記憶装置およびその制御方法

【課題】SOI構造の半導体記憶装置に電気的に書換え可能な不揮発性メモリを形成する手段を提供する。

【解決手段】第1の拡散層16、第2の拡散層17、前記第1および第2の拡散層間に配置された第3の拡散層、および第4の拡散層21と、前記第1および第2の拡散層とそれぞれ一部がオーバーラップし、前記第3の拡散層上から前記第4の拡散層にかけて延在するフローティングゲート電極13と、前記第1の拡散層および前記第3の拡散層に、共通の第1の電位を与える第1の制御線31と、前記第2の拡散層に、第2の電位を与える第2の制御線37と、前記第4の拡散層に、第3の電位を与える第3の制御線33と、を備え、前記フローティングゲート電極が前記第4の拡散層とオーバーラップした面積が、前記第2の拡散層とオーバーラップした面積よりも大きく、前記第1および第3の拡散層とオーバーラップした合計の面積よりも小さい。

(もっと読む)

半導体装置の製造方法および半導体装置

【課題】スプリットゲート型メモリセル構造を採用し、電荷蓄積層として窒化膜を用いる不揮発性メモリを有する半導体装置において電気的特性を向上させる。

【解決手段】半導体基板1Subの主面にn型の半導体領域6を形成した後、その上にスプリットゲート型のメモリセルのメモリゲート電極MGおよび電荷蓄積層CSLを形成する。続いて、そのメモリゲート電極MGの側面にサイドウォール8を形成した後、半導体基板1Subの主面上にフォトレジストパターンPR2を形成する。その後、フォトレジストパターンPR2をエッチングマスクとして、半導体基板1Subの主面の一部をエッチングにより除去して窪み13を形成する。この窪み13の形成領域では上記n型の半導体領域6が除去される。その後、その窪み13の形成領域にメモリセル選択用のnMISのチャネル形成用のp型の半導体領域を形成する。

(もっと読む)

不揮発性半導体記憶装置

【課題】不揮発性半導体記憶装置の信頼性を向上できる技術を提供することにあり、特に、スプリットゲート型トランジスタのメモリゲート電極への給電を確実に行なうことができる技術を提供する。

【解決手段】給電配線ESLは、給電配線ESLの一端を終端部TE1上に配置し、かつ、給電配線ESLの他端を終端部TE2上に配置し、さらに、給電配線ESLの中央部をダミー部DMY上に配置している。つまり、終端部TE1と終端部TE2およびダミー部DMYはほぼ同じ高さであるので、終端部TE1上からダミー部DMY上を介して終端部TE2上に配置されている給電配線ESLの大部分は同じ高さに形成される。

(もっと読む)

不揮発性半導体メモリデバイス、その製造方法および動作方法

【課題】書き換え時の閾値電圧変動を抑制し、かつ、データ保持特性低下を防止する。

【解決手段】メモリトランジスタMが、シリコン基板11に形成されているソース領域17S等と、これと離れて形成されているドレイン領域17D等と、両領域間のチャネル形成領域11Aを少なくとも覆って形成されているボトム絶縁膜12Aと、離散化された電荷蓄積手段(キャリアトラップ)を含む電荷蓄積膜12Bと、トップ絶縁膜12Cと、ゲート電極13と、を有する。ボトム絶縁膜12Aは、チャネル形成領域11Aにおけるシリコン基板11とのバリアハイトが、SiO2とSiとのバリアハイトより低いSiONから形成され、このSiONとSiとの界面は、窒素の組成比が9%以上である。

(もっと読む)

2ビットU字型メモリ構造及びその製作方法

【課題】U字型の底部を有するフローティングゲートを備える2ビットメモリ構造及びその製作方法を提供する。

【解決手段】メモリ構造は、基板50と、基板50上に設けられる制御ゲート70と、制御ゲート70の両側に設けられ、それぞれ基板50に埋まったU字型の底部57を備える複数のフローティングゲート74と、制御ゲート70と基板50の間に設けられる第一誘電層52と、フローティングゲート74のU字型底部と基板50の間に設けられる第二誘電層62と、制御ゲート70とフローティングゲート74の間に設けられる第三誘電層68と、フローティングゲートチャネル80の周りに設けられるローカルドープ領域58と、基板50の中でフローティングゲート74の一方の側に設けられるソース/ドレイン領域76と含む。

(もっと読む)

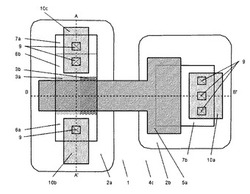

不揮発性半導体記憶装置及びその製造方法

【課題】 ゲート絶縁膜にかかる電界を増大させるとともに、ホットエレクトロン発生数を増加させることにより、書き込み効率の向上を実現することができる。

【解決手段】 本発明の不揮発性半導体記憶装置は、第1導電型の半導体基板1内に互いに離間して形成された第2導電型のソース領域2及びドレイン領域3の間に、ソース領域2及びドレイン領域3と離間形成されるように第2導電型の半導体領域4を備える。そして、このソース領域2と半導体領域4との間、及びドレイン領域3と半導体領域4との間の半導体基板1上には、第1及び第2の浮遊ゲート6a、6bが互いに隔てられ、かつ第1のゲート絶縁膜5を介してそれぞれ形成されている。また、第1及び第2の浮遊ゲート6上、並びに第1及び第2の浮遊ゲート6a、6b間の第1のゲート絶縁膜5上に、ゲート間絶縁膜7及び第2のゲート絶縁膜8をそれぞれ介して制御ゲート9が設けられている。

(もっと読む)

半導体装置およびその製造方法

【課題】電界効果トランジスタのオン電流を小さくすることなく、微細化を実現することのできる技術を提供する。

【解決手段】半導体基板の主面に素子分離領域2によって周囲を規定された活性領域3が配置され、この活性領域3は、周辺部3aに凹状の段差3cを有する断面形状となっており、活性領域3の周辺部3aの半導体基板の上面は、活性領域3の中央部3bの平坦な半導体基板の上面よりも低く形成されている。活性領域3の周辺部3aに凹状の段差3cを設けることにより、この活性領域3に形成されるMIS・FETの実質的なゲート幅を増加させて、MIS・FETのドレイン電流を増加させる。

(もっと読む)

不揮発性半導体記憶装置およびその製造方法

【課題】金属酸化膜とその上下を挟む絶縁膜との相互拡散を抑制することにより、電荷蓄積膜に金属酸化膜を用いた不揮発性メモリセルの電荷保持特性を向上させることのできる技術を提供する。

【解決手段】メモリセルMC1に備わる電荷保持用絶縁膜4を、半導体基板1のチャネル領域側から、ボトム絶縁膜4a、金属酸化膜からなる電荷蓄積膜4c、およびトップ絶縁膜4eが順次形成された積層膜によって構成し、さらに、ボトム絶縁膜4aに対してプラズマ窒化処理を行うことにより、ボトム絶縁膜4a中の上面側に、ピーク値を有して窒素濃度が1原子%以上の窒化領域4bを形成し、その窒化領域4bの厚さを0.5nm以上、1.5nm以下、窒素濃度のピーク値を5原子%以上、40原子%以下、窒素濃度のピーク値の位置をボトム絶縁膜4aの上面から2nm以内とすることにより、ボトム絶縁膜4aと電荷蓄積層4cとの相互反応を抑制する。

(もっと読む)

不揮発性半導体記憶装置の製造方法

【課題】メモリセルの電気特性が良好で、高集積化に適した不揮発性半導体記憶装置の製造方法を提供する。

【解決手段】まずメモリゲート電極MGの一方の側壁側に犠牲層ILのパターンが位置する配置状態が形成される。その配置状態から、メモリゲート電極MGの他方の側壁による段差部を覆うようにコントロールゲート用導電層CGが形成される。コントロールゲート用導電層CGに異方性エッチングを施してメモリゲート電極MGの他方の側壁に沿ってコントロールゲート用導電層CGを残存させることにより、コントロールゲート用導電層CGからコントロールゲート電極CGが形成される。

(もっと読む)

半導体記憶装置およびその製造方法

【課題】スプリットゲート型MONOSメモリセルにおいて、SSI方式による書込み時のディスターブ耐性を向上させることのできる技術を提供する。

【解決手段】選択用nMISQncと、選択用nMISQncの側面に絶縁膜6b、6tおよび電荷蓄積層CSLを介して形成されたメモリ用nMISQnmとを含むメモリセルMC1において、選択ゲート電極CGのゲート長方向端部下のゲート絶縁膜4の厚さが、ゲート長方向中央部下のゲート絶縁膜4の厚さよりも厚く形成され、選択ゲート電極CGと電荷蓄積層CSLとの間に位置し、かつ半導体基板1に最も近い下層の絶縁膜6bの厚さが、半導体基板1と電荷蓄積層CSLとの間に位置する下層の絶縁膜6bの厚さの1.5倍以下に形成される。

(もっと読む)

不揮発性メモリトランジスタ

【課題】書き換え可能な不揮発性メモリトランジスタであって、書き換えの繰り返しによる閾値電圧特性の変化が抑制された信頼性の高い不揮発性メモリトランジスタを提供する。

【解決手段】第1導電型の半導体基板31の表層部に、第2導電型のソース領域32とドレイン領域33が形成され、トンネル酸化膜41を介して、半導体基板31上でドレイン領域33に部分的に重なるようにして、浮遊ゲート電極51が設けられてなる書き換え可能な不揮発性メモリトランジスタ100であって、ソース領域32とドレイン領域33を最短距離で結ぶ断面において、ドレイン領域33と浮遊ゲート電極51の重なり寸法Lが、0.15μm以上、0.5μm以下、である不揮発性メモリトランジスタ100とする。

(もっと読む)

半導体装置およびその製造方法

【課題】MONOS型不揮発性メモリセルを有する半導体装置において、メモリセルに書き込まれたデータの消去残りを防いで、データの書き換え劣化を抑制することのできる技術を提供する。

【解決手段】選択ゲート電極CGとメモリゲート電極MGとの間のギャップ部側に多結晶シリコン膜からなる第1メモリゲート電極MG1を設け、ソース領域Srm側に第1メモリゲート電極MG1を構成する多結晶シリコン膜よりも不純物濃度の高い多結晶シリコン膜からなる第2メモリゲート電極MG2を設ける。これにより、データ書き込み時に、ギャップ部および第1メモリゲート電極MG1下の電荷蓄積層CSLに注入されるホットエレクトロンの注入量を第2メモリゲート電極MG2下の電荷蓄積層CSLに注入されるホットエレクトロンの注入量よりも減少させて、ギャップ部および第1メモリゲート電極MG1下の電荷蓄積層CSLにおけるデータの消去残りを防ぐ。

(もっと読む)

不揮発性半導体記憶装置及びそのデータ書き換え方法

【課題】書き換え回数の増加に伴う書き込み後の閾値電圧の低下を抑制することのできる不揮発性半導体記憶装置及びそのデータ書き換え方法を提供する。

【解決手段】アバランシェ降伏により、チャネル形成領域のドレイン近傍端部に生じるホットキャリアによって消去を行う電気的に書き換え可能な不揮発性半導体記憶装置において、チャネル形成領域を、ドレインから所定領域の第1チャネル形成領域と、第2チャネル形成領域に隣接する第2チャネル形成領域とにより構成した。そして、第2チャネル形成領域の不純物濃度を第1チャネル形成領域の不純物濃度よりも高くするとともに、2つのチャネル形成領域の境界を、ドレイン近傍端部とは異なり、ドレイン近傍端部とソース近傍端部との間の中間部内とした。

(もっと読む)

1 - 20 / 56

[ Back to top ]