Fターム[5F101BD30]の内容

不揮発性半導体メモリ (42,765) | 素子構造 (12,113) | SOI、薄膜トランジスタ、三次元素子 (1,051)

Fターム[5F101BD30]に分類される特許

1,041 - 1,051 / 1,051

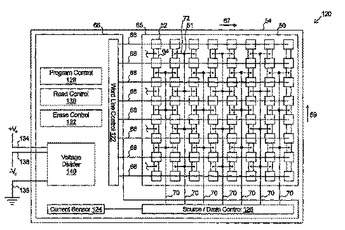

スタガー式ローカル接続構造を持つメモリセルアレイ

メモリセルアレイ(50)は、半導体基板(54)に製造された、2次元アレイのメモリセル(52)を含む。メモリセル(52)は、行方向(67)を形成する複数の行と、列方向(69)を形成する複数の列で並べられている。メモリセル(52)の各列は、複数の交互に配置されたチャネル領域(58)及びソース/ドレイン領域(64)を含む。各ソース/ドレイン領域(64)上には導電性インターコネクト(72)が配置されており、この導電性インターコネクト(72)はただ1つのその他のソース/ドレイン領域(64)に結合する。この1つのソース/ドレイン領域(64)とは、その列に隣接する第2の列に存在する領域である。導電性インターコネクト(64)は、1つおきの導電性インターコネクト(64)がその列の右側に隣接する列に接続するように、また、1つおきの導電性インターコネクトが、その列の左側に隣接する列に接続するように、配置される。複数のソース/ドレインコントロールライン(70)は、隣接するメモリセル(52)の列間に延在し、また、その隣接する列と列との間を結合する各導電性インターコネクト(72)に電気的に結合する。  (もっと読む)

(もっと読む)

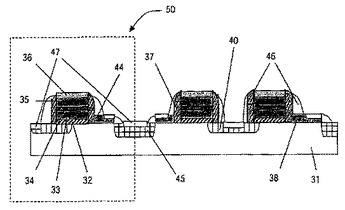

短チャネル効果を減少させる埋め込みチャネルフラッシュ構造

短チャネル効果を減少させたメモリセルを記載する。ソース領域(54)およびドレイン領域(56)を半導体ウェーハ(58)中に形成する。ソース領域(54)およびドレイン領域(58)の間にトレンチ領域(59)を形成する。このトレンチ領域、ソース領域およびドレイン領域の下に埋め込みチャネル領域(52)を形成する。半導体基板のトレンチ領域中にゲート絶縁層(60)を形成する。このゲート絶縁層は、埋め込みチャネル領域上に、およびソース領域とドレイン領域との間に形成される。埋め込みチャネル領域の上の半導体基板上に、制御ゲート層(70)を形成する。この制御ゲート層は、ゲート絶縁層によって埋め込みチャネルから分離される。  (もっと読む)

(もっと読む)

完全空乏型シリコン・オン・インシュレータのCMOSロジック

【課題】SOI技術を用いた部分空乏型CMOSデバイスにおける浮遊ボディの不必要な影響を制御可能とする。

【解決手段】シリコン・オン・インシュレータのCMOSメモリデバイスにおいて、引き出し線を含む領域が用いられる。引き出し線を逆方向にバイアスすることで、部分空乏型メモリセルのボディ領域から少数キャリアを取り除く。これにより、ボディ領域を完全空乏化し、浮遊ボディの不必要な影響を抑制する。

(もっと読む)

2−トランジスタメモリセル及びその製造方法

本発明は、メモリゲートスタック(1)を有する記憶トランジスタ(1)及び選択トランジスタを有する2-トランジスタメモリセルを基板(50)上に製造する方法であって、トンネル誘電層(51)が前記基板(50)と前記メモリゲートスタック(1)との間にもたらされる方法を提供する。前記方法は、第一の導電層(52)及び第二の導電層(54)をもたらし、前記第二の導電層(54)をエッチし、それによってコントロールゲートを形成し、前記第一の導電層(52)をエッチし、それによってフローティングゲートを形成することによって前記メモリゲートスタック(1)を形成するステップを有する。前記方法は更に、前記第一の導電層(52)がエッチされる前に、前記トンネル誘電層(51)の下に形成されるべきチャネルの方向で前記コントロールゲートに対してスペーサ(81)を形成するステップと、その後、前記第一の導電層(52)をエッチするために前記スペーサ(81)をハードマスクとして使用し、それによって前記フローティングゲートを形成し、それによってフローティングゲートをコントロールゲートに自己整合させるステップとを有することを特徴とする。本発明は、前記コントロールゲート(54)は前記フローティングゲート(52)よりも小さくなり、スペーサ(81)が、前記コントロールゲート(54)に隣接してもたらされるメモリセルも提供する。  (もっと読む)

(もっと読む)

不揮発性メモリ装置を製造する方法及びそれによって得られるメモリ装置

本発明は、ダブル・ゲート・スタック及びシングル・アクセス・ゲートを備える不揮発性メモリ・セル(50)を加工する方法に関する。この方法は、アクセス・ゲートを加工する方法を、自己整合的な、ソース注入とは別のドレイン注入と組み合わせる。本発明の方法は、マスク位置合せ精度を考慮せずに、メモリ装置を消去するための延長されたドレインを自己整合的に注入することを可能にする。さらに、この方法は、さらなるマスクを使用せずにドレイン及びソース注入を互いに異なるドーピングで実施する方法を提供する。  (もっと読む)

(もっと読む)

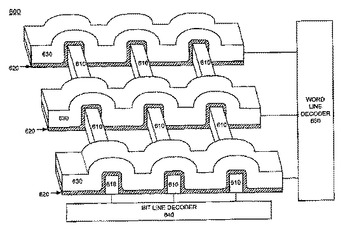

三次元集積回路構造及びこれを作る方法

垂直方向の半導体装置は、電気装置そして/または相互接続を含む分離して作られた基板に付加される。多くの垂直方向の半導体装置は物理的に互いに分離され、そして同一半導体本体又は半導体基板内には配置されない。多くの垂直方向の半導体装置は取り付けられた後に個別のドープされたスタック構造を生成するため、エッチングされた数個のドーピングされた半導体領域を含む薄い層として分離して作られた基板へ付加される。あるいは多くの垂直方向の半導体装置が分離して作られた基板に取り付けるのに先立ち製作される。ドープされたスタック構造は、ダイオードキャパシタ、n‐MOSFET、p‐MOSFET、バイポーラトランジスタ、及び浮遊ゲートトランジスタのベースを形成する。強誘電体メモリー装置、強磁性体メモリー装置、カルコゲニド位相変更装置が分離して作られた基板と連結して使用するために、堆積可能なアッド‐オン層に形成される。堆積可能なアッド‐オン層は相互接続ラインを含む。

(もっと読む)

(もっと読む)

不揮発性メモリデバイス

不揮発性メモリデバイス(100)は、基板(110)、絶縁層(120)、フィン(210)、複数の誘電層(310〜330)及び制御ゲート(510/520)を備える。絶縁層(120)は、基板(110)上に形成され、フィン(210)は、絶縁層(120)上に形成される。誘電層(310〜330)は、このフィン(210)を覆うように形成され、制御ゲート(510/520)は、誘電層(310〜330)上に形成される。誘電層(310〜330)は、メモリデバイス(100)の電荷格納構造として機能する酸化物−窒化物−酸化物層を備える。  (もっと読む)

(もっと読む)

個別ゲート構造を備えたトランジスタ

個別ゲート構造(701,703)を備えたトランジスタを形成する方法。これらのゲート構造はそれぞれ、半導体構造(105)の複数の側壁に隣接する。本方法は、ゲート材料層(203)を含む少なくとも一つの共形な層を、チャネル領域を含む半導体基板の上に堆積させることを含む。平坦層(403)がウェハの上に形成される。平坦層は、基板上の所定の位置において少なくとも一つの共形な層の頂部表面よりも低い位置に頂部表面を有する。少なくとも一つの共形な層をエッチングすることにより、半導体構造の上のゲート材料は除去される。  (もっと読む)

(もっと読む)

電荷蓄積場所を有するメモリ

メモリは、チャネル領域(1725)を含む半導体構造(1105)の対向する側壁に隣接するゲート構造と、ゲート構造と対向する側壁との間にある複数の電荷蓄積場所(1713、1715、1709及び1711)とを有する。チャネル領域は、2つの電流端子領域間に配置され、それらの電流端子領域は一例ではソース/ドレイン領域としての役割を果たす。メモリセルは、メモリセルのアレイ(1801)内に実装することができ、一方のゲート構造が1つのワード線に結合され、他方のゲート構造が別のワード線に結合される。一例では、各セルは、それぞれが1ビットのデータを記憶する、4つの電荷蓄積場所を含む。  (もっと読む)

(もっと読む)

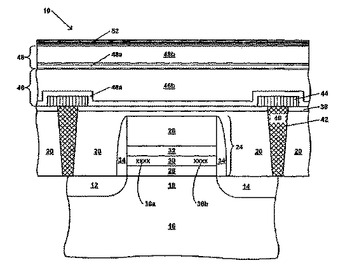

BEOLプロセスにおいて、UVによって誘発されたSONOSデュアルビットのフラッシュメモリデバイスの電荷を低減するUVブロック層

SONOSフラッシュメモリセル(24)をUVにより誘発される電荷から保護する方法であって、SONOSフラッシュメモリセル(24)を半導体デバイス(10、50)に製造するステップと、SONOSフラッシュメモリセル(24)上に、少なくとも1つのUV保護層(38、46、48、又は52)を蒸着させるステップとを含み、UV保護層には実質的にUV不透過性の材料が含まれる。SONOSフラッシュメモリセル(24)と、少なくとも1つのUV保護層(38、46、48又は52)(UV保護層には実質的にUV不透過性の材料が含まれる)を含むSONOSフラッシュメモリデバイス(10、50)が提供される。  (もっと読む)

(もっと読む)

非揮発性メモリセルアレイの非活性領域に隣接する非揮発性メモリセルを読み出すための改善された方法

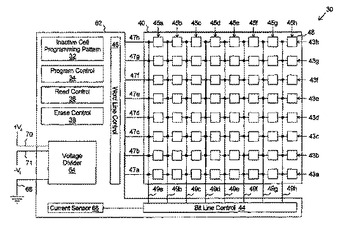

メモリセル48のアレイ30にデータパターンをストアし、再生するための方法であり、活性コラム45b及び45gと、不活性コラム45c及び45fとを含み、活性コラム45b及び45gにデータパターンをストアする。不活性メモリセルプログラミングパターン32が識別される。バルク消去中、過消去及び活性メモリセル48への電流リークを回避するために定期的に電荷をストアする目的で電荷がストアされる、不活性コラム45c及び45fのメモリセル48の全てあるいは選択された複数のメモリセルを、前述の不活性メモリセルプログラミングパターン32が識別する。  (もっと読む)

(もっと読む)

1,041 - 1,051 / 1,051

[ Back to top ]